Преобразователь последовательного кода в параллельный

Иллюстрации

Показать всеРеферат

Изобретение относится к вычис- . лительной технике, а именно к устройствам преобразования информации, представленной в веде последовательного кода, и может быть использовано в автоматических системах для связи с цифровыми вычислительнь1Ми устройствами . Преобразователь формирует на выходе параллельный код только в том случае, если на его вход поступило заранее заданное количество разрядов последовательного кода и в момент преобразования не было сбоев, вызванных кратковременным снятием питания или эти сбои не при- .вели к искажению входной информации. Данное свойство обеспечивает преобразователю высокую функциональную надежность. Преобразователь последовательного кода в параллельный содержит генератор тактовых импульсов, два счетчика импульсов, два элемента И, четыре триггера, два распределителя импульсов, регистр сдвига и формирователь импульсов. 1 ил.

COOS СОВЕТСКИХ

РЕСПУБЛИК

Ai (19) (21) (51) 4 Н 03 М 9/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АВТОРСНОМЪ СВИДЕТЕЛЬСТВУ ь .

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3941972/24-24 (22) 27.06 ° 85 (46) 15.01.87, Бюл. Н - 2 (72) Ю.А.Ильченко и Г.С.Ушаков (53) 681.325(088.8) (56) Авторское свидетельство СССР

В 1081639, кл. С 06 F 5/04, 1982.

Авторское свидетельство СССР

У 783789, кл. G 06 F 5/04, 1979. (54) ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО КОДА В ПАРАЛЛЕЛЬНЫЙ (57) Изобретение относится к вычислительной технике, а именно к устройствам преобразования информации, представленной в виде последователь— ного кода, и может быть использовано в автоматических системах для связи с цифровыми вычислительными устройствами. Преобразователь формирует на выходе параллельный код только в том случае, если на его вход поступило заранее заданное количество разрядов последовательного кода и в момент преобразования не было сбоев, вызванных кратковременным снятием питания или эти сбои не при.вели к искажению входной информации, Данное свойство обеспечивает преобразователю высокую функциональную надежность. Преобразователь последо" вательного кода в параллельный содержит генератор тактовых импульсов, . два счетчика импульсов, два -элемента И, четыре триггера, два распреде- 1р

O лителя импульсов, регистр сдвига и формирователь импульсов ° 1 ил.

1 128

Изобретение относится к вычислительной технике, а именно к устройствам преобразования информации, и может быть использовано в автоматических системах для связи с цифровыми вычислительными устройствами.

Цель изобретения — повышение фун" кциональной надежности эа счет исключения сбоев, вызванных кратковременным снятием питания,и за счет фор— мирования выходного кода только после приема достоверной информации.

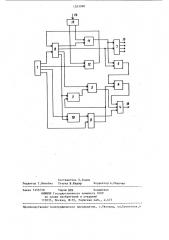

Ка чертеже представлена функциональная схема преобразователя.

Преобразователь последовательного кода в параллельный содержит генератор 1 тактовых импульсов,.первый счетчик 2 импульсов, первый триггер

3, первый и второй элементы И 4 и 5, второй триггер 6, регистр 7 сдвига,, первый и второй распределители 8 и 9 импульсов, второй счетчик 10 импуль сов, третий и четвертый триггеры 11 и 12, формирователь 13 импульсов.

Вход формирователя 13 импульсов является входом 14 преобразователя, выходы регистра 7 — выходами 15 преобразователя, а выход элемента И 4выходом записи 16 преобразователя.

Преобразователь последовательного кода в параллельный работает следующим образом.

Двоичный последовательный 32-разрядный код поступает по входу 14 в формирователь импульсов 13, где преобразуется в последовательность импульсов информации и импульсов синхронизации. 1 .мпульс синхронизации поступает на информационный вход четвертого триггера 12 и тактовыми импульсами с генератора 1 записывается в четвертый триггер 12 и с его выхода подается на вход первого распределителя 8 импульсов, на другой вход которого поступают тактовые импульсы с генератора 1, на входе первого распределителя 8 импульсов формируется последовательность импульсов,.первый из которых, поступая на вход синхронизации третьего триггера 11, записывает информацию в третий триггер 11

Второй импульс с выхода первого распределителя 8 импульсов, поступая на вход регистра 7 сдвига, производит последовательный сдвиг информации,поступившеч с третьего триггера 11.

Третий импульс поступает на нулевой вход триггера 3 и переводит его в нулевое состояние, при этом на его

3980 2 выходе вырабатывается запрещающий сигнал. Четвертый импульс подается на счетный вход первого счетчика 2, увеличивая его состояние на "1", и

5 на вход установки в "0" второго счетчика 10, устанавливая его в нулевое состояние. С выхода третьего триггера 11 информационные импульсы поступают на вход регистра 7 сдвига„ в котором под воздействием тактовых импульсов с выхода первого распределителя 8 импульсов происходит продвижение информации, и одновременно информационные импульсы, соответству15 ющие коду "1" „ через второй элемент

И 5 поступают на счетный вход второго триггера 6. В 32-рязрядном коде,поступающем по входу 14, содержится разряд четности, дополняющий инфор2О мацию до нечетного состояния, Таким образом, при поступлении всех 32-х разрядов кода на выходе второго триггера 6 формируется разрешающий сигнал, если количество "единиц" в ко25 де было нечетное. После прохождения

32-х импульсов следует пауза. В этот момент времени на вход установки в

"0" второго счетчика 10 сигналы не оступают, а на счетный вход подаются

30 пульсы с выхода генератора 1. Если реми между импульсами синхронизации соответствует паузе между слова-. ми, на выходе второго счетчика 10 вырабатывается разрешающий сигнал,ко35 торый, поступая на второй распределитель импульсов 9, под воздействием тактовых импульсов с генератора 1 вырабатывает два импульса. Первый импульс поступает на второй вход пер40 вого элемента И 4, если есть разрешение от триггера 3 и триггера 6, формирует сигнал разрешения записи информации, выдаваемой по выходу 16.

Второй импульс с выхода второго рас45 пределителя 9 импульсов подается на первый счетчик 2 и триггер 6 : o6нуляет их. Триггер 3 формирует сигнал разрешения, .если поступило 32 импульса, если импульсов больше или

gp.меньше 32-х, сигнал разрешения приема информации не формируется, Импульсы на выходах генератора 1 тактовых импульсов формируются в та55 кой последовательно, что на каждом последующем выходе импульс формируется по заднему фронту импульса на предшествующем выходе. Причем формирование импульса на первом входе про3 1283980 исходит по заднему фронту импульса на четвертом выходе.

Формула изобретения

Преобразователь последовательного кода в параллельный, содержащий генератор тактовых импульсов, первый счетчик импульсов, выход которого соединен с S-входом первого тригге- () ра, выход которого соединен с первым входом первого элемента И, второй элемент И, выход которого соединен со счетным входом второго триггера, и регистр сдвига, о т л и ч а ю щ и й-f5 с я тем, что, с целью повыщения функциональной надежности преобразователя за счет исключения сбоев, вызванных кратковременным снятием питания, и за счет формирования выходного ко- Zg да только после приема достоверной входной информации, в него введены распределители импульсов, второй счетчик импульсов, третий и четвертый триггеры и формирователь импульсов, 25 первый и второй выходы которого соединены с D-входами третьего и четвертого триггеров соответственно,первый выход первого распределителя импульсов соединен с С-входом третьего 30 триггера, второй выход — с первыми входами регистра сдвига и второго элемента И, третий выход — с R-входом первого тригера, четвертый выход — со счетным входом первого счет- З5 чика импульсов и входом установки нуя второго счетчика импульсов, перый выход второго распределителя импульсов соединен с входами установки нуля первого счетчика импульсов и второго триггера, выход второго счетчика импульсов соединен с первым входом второго распределителям импульсов, второй выход которого соединен с вторым входом первого элемента

И, выход второго триггера соединен с третьим входом первого элемента И, выход третьего триггера соединен с вторыми входами регистра сдвига и второ о элемента И, выход четвертого триггера соединен с первым входом первого распределителя импульсов,первый выход генератора тактовых импульсов соединен с вторым входом первого распределителя импульсов, второй выход — с С-входом четвертого триггера, третий выход — со счетным входом второго счетчика импульсов, четвертый выход — с вторым входом второго распределителя импульсов, вход формирователя импульсов является входом преобразователя последовательного ко" да в параллельный, выходы регистра сдвига являются информационными вы ходами преобразователя последовательного кода в параллельный, выход первого элемента И является дополнительным выходом записи преобразователя последовательного кода в параллельный.

Составитель Б,Ходов

Редактор Т.Митейко Техред В.Кадар, Корректор А,Обручар

Заказ 7459/58 Тираж 899 Подписное

ВНИИХИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д,4/5

Производственно-полиграфическое предприятие, r.ужгород, ул.Проектная,4