Устройство согласования скоростей цифровых потоков при передаче сигналов цифрового радиовещания

Иллюстрации

Показать всеРеферат

Изобретение относится к радиотехнике и связи. Цель изобретения - повышение точности согласования скоростей. Устройство содержит выделитель I синхроимпульсов, блок 2 последовательно-параллельного преобразования , блок 7 синхронизации, два буферных регистра (БР) 10 и П, переключатель 12, блок 13 уплотнения и блок 14 параллельно-последовательного преобразования. Вновь введены анализатор 3 рассиихронизации, счетчик 4, коммутатор 5, форми-, рователь 6 синхроимпульсов, анализатор 8 пауз, блок 9 задержки. Приоритетным является режим считывания, а для обеспечения возможности компенсации как опережения, так и отставания предусмотрено неполное заполнение БР 10 и 11 в режиме синхронизма. Информация с БР 10 и II после отработки в блоках 13 и 14 к виду, удобному для передачи, подается на выход устройства. 1 ил. 3 (Л

союз советских

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (Ю 4 H 04 J 3 06

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3931993/24-09 .(22) 11.07.85 (46) 15,01.87. Бюл. У 2 (71) .Московский электротехнический институт связи (72) М.В. Гитлиц, В.В. Добровольский, А.Ю. Зеленин, О.Б. Попов и B.À. Севрюгин (53) 621.395.44 (088.8) (56) Заявка Японии У 59-28737, кл. Н 04 J 3/06, 1984.

Патент США У 4058682, кл. Н 04 J 3/06, 1976. (54) УСТРОЙСТВО СОГЛАСОВАНИЯ СКОРОСТЕЙ ЦИФРОВЫХ ПОТОКОВ ПРИ ПЕРЕДАЧЕ

СИГНАЛОВ ЦИФРОВОГО РАДИОВЕЩАНИЯ (57) Изобретение относится к радио- " технике и связи. Цель изобретения повышение точности согласования скоростей. Устройство содержит выде„,SU 128 9 А I.литель 1 синхроимпульсов, блок 2 последовательно-параллельного преобразованияния, блок 7 синхрониз ации, два буферных регистра (БР) 1О и 11, переключатель 12, блок 13 уплотнения и блок 14 параллельно-последовательного преобразования. Вновь введены анализатор 3 рассинхронизации, счетчик 4, коммутатор 5, форми-, рователь 6 синхроимпульсов, анализатор 8 пауз, блок 9 задержки. Приоритетным является режим считывания, а для обеспечения воэможности компенсации как опережения, так и отставания предусмотрено неполное заполнение БР 10 и 11 в режиме синхронизма.

Информация с БР 10 и ll после отработки в блоках 13 и 14 к виду, удобному для передачи, подается на выход устройства. 1 ил.

1 !28

Изобретение относится к радиотехнике и связи, в частности к передаче и приему звуковых сигналов, и может быть использовано в цифровых системах радиовещания с независимыми синхрогенераторами.

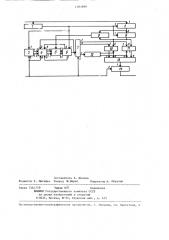

Цель изобретения - повышение точности согласования скоростей, На чертеже приведена структурная электрическая схема устройства согласования скоростей цифровых потоков при передаче сигналов цифрового радиовещания.

Устройство содержит выделитель 1 синхроимпульсов, блок 2 последовательно-параллельного преобразования, анализатор 3 рассинхронизации, счетчик 4, коммутатор 5, формирователь 6 синхроимпульсов, блок 7 синхронизации, анализатор 8 пауз, блок 9 задержки, первый и второй буферные регистры 10 и 11, переключатель 12, блок 13 уплотнения и блок 14 параллельно-последовательного преобразования.

Устройство согласования скоростей цифровых потоков при передаче сигналов цифрового радиовещания работает следующим образом, При поступлении сигнала «а вход выделения 1 на его выходе образуется последовательность импульсов, ко» торая подается на первые входы ана— лизатора 3, формирователя 6, блока

9 и вход блока 2. На синхронизирующий вход анализатора 3 подается последовательность эталонных синхроимпульсов. При отставании или опережении эталонной последовательности ат входной на несколько полных тактов на первом или втором выходе анализатора 3 формируется командный импульс, который фиксируется в счетчике, выполненном реверсивным.

Анализатор 8, подключенный к входу и выходу блока 9, определяет наличие сигнала паузы в принятом сигнале и формирует на своем выходе сигнал "разрешение трансформации паузы". Параметры блока 9 определяются минимально допустимым временем паузы в передаваемом сигнале с точки зрения качества его восприятия слушателем.

При опережении эталонной после, довательности по отношению к входной число целых тактов опережения фиксируется в счетчике 4, на пер3989 2

f0

55 вом выходе которого формируется ко-. мандный сигнал "Опережение", который при наличии сигнала "Разрешение трансформации паузы подается с помощью коммутатора 5 на второй вход формирователя 6. Наличие командного сигнала на втором входе формирователя 6 при поступлении на

его первый вход очередного входного импульса обеспечивает на первом выходе формирователя б формирование синхропоследовательности. Сформированная синхропоследовательность поступает на прямой вход счетчика

l блока 7, обеспечивающего подачу ее на второй или третий выходы в зависимости от используемого в данный момент для записи информации первого или второго буферного регистра 10 или 11. При этом в ячейки соответствующего первого или второго буферного регистра 10 или

11 производится запись избыточных импульсов символа "пауза" с выхода блока 9. Одновременно;синхропоследовательность с первого выхода формирователя б поступает на третий вход счетчика 4, а на его пятый вход подается сигнал peedpca счетчика

"Опережение" с третьего выхода формирователя 6. После компенсации тактов опережения, зафиксированных в счетчике 4, и обнуления всех его ячеек снимается сигнал "Опережение" с первого выхода счетчика 4, что приводит к прекращению работы синхрогенератора и записи дополнительных импульсов в один из буферных регистров 10 или 12 В процессе дальнейшего считывания информации из буферного регистра длительность сигнала увеличивается sa счет удлинения паузы на необходимое количество циклов, При отставании эталонной синхропоследовательности от входной число целых тактов отставания фиксируется в счетчике 4, а на его втором выходе формируется сигнал "Отставание", который в случае наличия сигнала

"Разрешение трансформации паузы" на третьем входе коммутатора 5 подается на третий вход формирователя

6, снимая синхроимпульс с его первого выхода. В этом случае синхроим пульсы не попадают на вход блока 7 и, следовательно, на его второй и третий выходы. Запись символа паузы

3 1283989 4 в первый и второй буферные регистры

10 и ll не производится в течение времени, необходимого для компенсации. Одновременно с второго выхода формирователя 6 подается сигнал реверса счетчика 4 по его четвертому входу, а на вход этого счетчика подается эталонная синхропоследовательность. После компенсации тактов отставания, зафиксированных B счетчике, и обнуления всех его ячеек сигнал "Отставание" снимается с второго выхода анализатора 3, и процесс компенсации прекращается.

Считывание информации с первого и второго буферных регистров 10 и

11 производится под действием синхропоследовательности, подаваемой одновременно на вход соответствующего счетчика 4, работающего в режиме реверса. По обнулении всех его ячеек подается сигнал смены регистров и начинается считывание с второго буферного регистра 11 вне зависимости от его заполненности. л а и з о синхроимпульсов, пеРвый выход котои з о б р е т е н и я

40 рого подключен к входу блока синхроТаким образом, приоритетным является режим считывания, а для обеспечения возможности компенсации как опережения, так и отставания предусмотрено неполное заполнение первого и второго буферных регистров

10 и 11 в режиме синхронизма.

Информация с первого и второго буферных регистров 10 и 11 после ,обработки в блоках 13 и 14 к виду, удобному для передачи, подается на выход устройства.

30 35 входам соответственно первого и второго буферных регистров, выходы которых подключены соответственно к первому и второму входам блока уплотнения, выход которого подключен к входу блока параллельно-последовательного преобразования, о т л и ч а ю щ е е с я тем, что, с целью повышения точности согласования скоростей, введены анализатор рассинхронизации, счетчик, коммутатор, формирователь синхроимпульсов, анализатор пауз и блок задержки, первый вход которого соединен с входом блока последовательно-параллельного преобразования, выход которого соединен с объединенными первым васодом анализатора пауз и вторым входом блока задержки, выход которого соединен с объединенными вторыми входами первого и второго буферного регистра и анализатора пауз, выход которого подключен к управляющему входу коммутатора, первый и второй входы которого подключены к первому и второму выходу счетчика, первый и второй входы которого соединены с первым и вторым выходами анализатора рассинхронизации, вход которого соединен с.вуходом выделителя синхроимпульсов, и первым входом формирователя синхроимпульсов, первый, второй и третий выходы которого соединены соответственно с третьим, четвертым и пятым входами счетчика, первый и второй выходы коммутатора соединены с первым и вторым входами формирователя

Устройство согласования скоростей цифровых потоков при передаче сигналов цифрового радиовещания, содержащее последовательно соединенные выделитель синхроимпульсов и блок последовательно-параллельно/ го преобразования, входы которых объединены, а также последовательно соединенные блок синхронизации и переключатель, первый и второй выходы которого подключены к первым

45 щие входы анализатора рассинхронизации, счетчика, блока синхрониэа50 ции и блока параллельно-последовательного преобразования объединены. низации, второй и третий выходы которого подключены к третьим входам .. соответственно первого и второго буферных регистров, первые входы которых объединены соответственно с третьим и четвертым входами блока уплотнения, при этом синхрониэирую! 283989

Составитель В. Шевцов

Редактор Т. Митейко Техред И.Верес Корректор А. Обручар

Заказ 7461/59 Тираж 637 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д, 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4