Устройство для контроля логических схем

Иллюстрации

Показать всеРеферат

Изобретение отдосится к вычислительной технике, в частности к сред ствам контроля и отладки цифровых устройств и является усовершенство- .ванием изобретения по авт.св.№ 744580. Цель изобретения - повьшение достоверности контроля. Для этого в устройство для контроля логических схем введены блок регистрации импульсов малой длительности и переключатель. Предлагаемое устройство может быть использовано для контроля и диагностики неисправностей в устройствах цифровой вычислительной техники и дискретйой автоматики. 3 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (11) (51) 4 G 06 F 11/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

IlO ДЕЛАМ ИЗОБРЕТЕНИЙ ИОТНРЫТИЙ (61) 744580 (21)3858068/24-24 (22) 20.02.85 (46) 23,01.87. Вюл. У 3 (72) И.В.Соков и А.В.Пчелинцев (53) 681.3(088.8) (56) Авторское свидетельство СССР

)) 744580, кл. С 06 F 11/00, 1978. (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЛОГИЧЕСКИХ СХЕК (57) Изобретение отяосится к вычислительной технике, в частности к сред» ствам контроля и отладки цифровых .устройств и является усовершенствованием изобретения по авт.св.)) 744580 °

Цель изобретения — повышение достоверности контроля. Для этого в устройство для контроля логических схем введены блок регистрации импульсов малой длительности и переключатель.

Предлагаемое устройство может быть использовано для контроля и диагностики неисправностей в устройствах цифровой вычислительной техники и дискретной автоматики. 3 ил.! 285476 2

Изобретение относится к вычислительной технике, в частнос.ти к средствам контроля и отладки цифровых устройств, и является усовершенствованием изобретения по ант. св.

N- 744580.

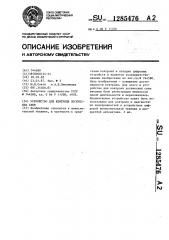

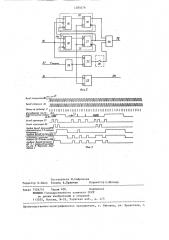

Цель изобретения — повышение достоверности контроля, На фиг. 1 приведена структурная схема устройства;на фиг. 2 — функциональная схема блока регистрации импульсов малой длительности; на фиг, 3 — временная диаграмма работы устройства в режиме анализа логических временных диаграмм.

Устройство содержит блок 1 регистрации импульсов малой длительности, переключатель 2, регистр 3, цифровой компаратор 4, блок 5 задержки, блок

6 памяти, первый блок 7 управления, второй блок 8 управления, блок 9 ин дикации, генератор 10 синхроимпульсов, блок 11 синхронизации, преобразователь 12 кодов, блок 13 выработки временной диаграммы, блок 14 выработки знаковой информации, информационные входы 15 и 16 устройства и вход

17 внешней синхронизации.

Блок регистрации импульсов малой длительности (фиг. 2) содержит триггеры 18-23, переключатель 24, элемент ИЛИ 25, элемент НЕ 26, тактовый вход 27, выходы 28 и 29. Триггеры

18, 20 и 19, 21 образуют соответственно первый и второй формирователи

30 и 31.

Устройство работает в двух режимах — режиме анализа логических состояний и режиме анализа логических временных диаграмм.

В режиме анализа логических временных диаграмм устройство работает следующим образом.

При установке движка переключателя 2 в нижнее положение информационный вход 15 подключается непосредственно к соответствующему входу регистра 3. В этом случае устройство устойчиво регистрирует сигналы, длительность которых превышает время дискретизации dt определяемое быстродействием блока 6 памяти и задаваемое тактовой частотой генератора 10 синхроимпульсов F, „, (частотой занесения информации на регистр 3), В том случае если в исследуемой последовательности импульсов оказывают-, ся такие, длительность которых мень5

20 ше времени дискретизации (t d t), схема не может обеспечить гарантированную их регистрацию на регистре

3 и в блоке 6 памяти (фиг. 3).

При установке движка переключателя 2 в верхнее положение первый вход регистра 3 отключается от информационного входа 15 и подключается к выходу блока 1 регистрации импульсов малой длительности, При поступлении одиночного импульса малой длительности (t - д t) срабатывает формирователь 31 состоящий из триггеров 19 и 21. При этом формирователь 30, составленный из триггеров 18 и 20, блокирован сигналом низкого уровня с выхода триггера 21. При повторном поступлении импульса малой длительности во время следующего такта работы генератора синхроимпульсов срабатывает формирователь 30, состоящий из триггеров 18 и 20 (фиг. 3). ловии, что общая длительность "пачки" меньше h t) или и чередующихся сигналов длительностью dt (при условии, что ширина "пачки" находится в пределах длительности и периодов тактовой частоты Р „ генератора синхроимпульсов). В зависимости от положения движка переключателя 24 возможны два варианта работы блока регистрации импульсов малой длительности.

В нижнем положении движка переключателя 24 при помощи элемента ИЛИ 25 происходит наложение сформированных триггерами 20 и 21 импульсов на ис35

40 лов. При этом в устройстве регистрируются либо импульсы с формирователей

30 и 31 блока 1, которые воспроизводятся на временной диаграмме в виде отдельных сигналов длительности

50 сов малой длительности), либо сигнает h t. Триггеры 22 и 23 служат для устранения временного рассогласования фронтов входных сигналов с фронТаким образом, на первый и второй входы элемента ИЛИ 25 подаются или одиночный сигнал длительностью, равной d t (при наличии одиночного импульса малой длительности), или

30 "пачки" подобных импульсов (при усследуемую последовательность сигнаdt(n" ) — при поступлении импульсов малой длительности ("пачек" импульлы входнои последовательности — при условии, что их длительность превыша1285476 тами импульсов, формируемых триггерами 20 и 21.

В верхнем положении движка переключателя 24 на выходе элемента ИЛИ 25 формируется либо импульс длительностью At соответствующий появлению любого фронта в исследуемой последо-. вательности сигналов, либо импульс длительностью п b,t, соответствующий появлению "пачки" импульсов малой 10 длительности или дроблению фронта исследуемого сигнала.

Анализ исследуемых последовательностей сигналов производится при вос- 15 произведении зарегистрированной временной диаграммы на экране блока 9 индикации, формула из обретения 20

Устройство для контроля логических схем по авт. св. N - 744580, о т л и— ч а ю щ е е с я тем, что, с целью повышения достоверности контроля, в него введены блок регистрации импульсов малой длительности и переключатель, блок регистрации импульсов ма— лой длительности содержит шесть триггерон, элемент ИЛИ, элемент НЕ и пе- З0 реключатель, причем в блоке регистрации импульсов малой длительности синхровходы первого и второго триггеров и информационный вход третьего триггера объединены и подключены к пер- 35 .вому информационному входу устройства, нулевые входы первого и второго тригrepoa соединены соответственно с инверсными выходами четвертого и пятого триггеров, информационные входы которых подключены к прямым выходам первого и второго триггеров соответственно, синхровходы третьего, четвертого, пятого и шестого триггеров объединены и подключены к выходу элемента НЕ, вход которого соединен с выходом генератора синхроимпульсов устройства, информационный вход первого триггера соединен с прямым выходом пятого триггера, информационный вход второго триггера является шиной задания потенциала логической единицы блока регистрации импульсов малой длительности, информационный вход и выход шестого триггера подключены соответственно к второму информационному входу устройства и первому замыкающему контакту переключателя устройства, второй замыкающий контакт которого подключен к выходу элемента

ИЛИ блока регистрации импульсов малой длительности, первый.и второй входы элемента ИЛИ соединены с выходами четвертого и пятого триггеров соответственно, выход третьего триггера подключен через переключатель к третьему входу элемента ИЛИ, размыкающие контакты переключателя устройства подключены соответственно к первому и второму информационным входам устройства, переключающие контакты переключателя устройства соединены с соответствующими информационными входами регистра.

1285476

Фиг. 2

dt

Выхо8 генератора6(Г )

НЛПВОПП5 ""." Р"" " о 1111111111 .! 1111111111111111111111111111I I I I I I I! I I ! I додатвльность иипульИ со8 Вх 18 Выход триггера 2!

Выход триггера 20

Пер8ый Выход регистра 3 (переключатель 2 8 нижнем положении )

ПеЬВью Выход регистра 3

<переключатель 2 8 Верх положении; переключатель 2Ь В нижн. полож.

Вербый Выход регистра 3 (переключатели

2и 2Ч В Верхнем положении ) юг.З

Составитель И.Сафронова

Редактор Е.Папп Техред А.Кравчук Корректор С.Шекмар

Заказ 7526/51 Тираж 670 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Прректная, 4