Ячейка памяти

Иллюстрации

Показать всеРеферат

Изобретение относится к цифровой вычислительной технике и может быть использовано в оперативных запоминающих устройствах. Целью изобретения является повышение помехозащищенности ячейки памяти при действии напряжения на адресном входе. Для достижения этой цели в ячейку памяти введены два накопительных конденсатора,которые включены между адресным входом ячейки памяти и узловыми точками триггера ячейки памяти. Благодаря конденсаторам при действии сигнала на адресном входе повьшается потенциал затвора открытого МДП-транзистора триггера , что приводит к уменьшению эффективного сопротивления транзистора и снижению вероятности, ложного переключения триггера. 1 ил. (Л

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН

„„SU„„1285533 А1 (594 G 11 С 11 40 4 f

4 ь 1...

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3833579/24-24 (22) 29.12.84, (46) 23.01.87. Бюл. Ф 3 (71) Московский институт электронной техники (72) В.В.Баринов, П.M.ÃàôàðîB и О.А.Титов (53) 681.327.66(088.8) (56) Алексенко А.Г., Шагурин И.И.

Микросхемотехника. М.: Радио и связь, 1982, с. 255.

IEEE J. of Solid State Circuits ч. SC-18, 1983, й- 4, р. 414-417. (54) ЯЧЕЙКА ПАМЯТИ (57) Изобретение относится к цифровой вычислительной технике и может быть использовано в оперативных запоминающих устройствах. Целью изобретения является повышение помехозащищенности ячейки памяти при действии напряжения на адресном входе. Для достижения этой цели в ячейку памяти введены два накопительных конденсатора,которые включены между адресным входом ячейки памяти и узловыми точками триггера ячейки памяти. Благодаря конденсаторам при действии сигнала на адресном входе повышается потенциал затвора открытого МЦП-транзистора триггера, что приводит к уменьшению эффективного сопротивления транзистора и снижению вероятности. ложного переключения триггера. 1 ил.

1 12855

Изобретение оТНосНТс.ÿ к цифровой вычислительной технике и может быть использовано в оперативных запоминающих устройствах.

Цель изобретения — повышение по5 мехозащищенности ячейки памяти при действии напряжения на адресном входе.

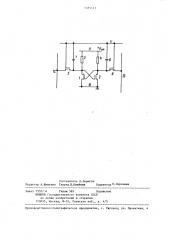

На чертеже приведена схема ячейки памяти. 1О

Ячейка памяти содержит триггер, состоящий из ключевых МДП-транзисторов 1 и 2 и нагрузочных резисторов

3 и 4, коммутирующие элементы, выполненные на 11ДП-транзисторах 5 и б, 15 и зарядные элементы, выполненные на конденсаторах 7 и 8. На схеме показаны также шина 9 питания, шина 10 нулевого потенциала, адресный вход

11, первый 12 и второй 13 разрядные 20 входы.

Ячейка памяти работает следующим образом.

В режиме хранения на адресной шине

11 устанавливается потенциал, меньший 25 порогового. напряжения транзисторов

5 и 6, Для записи информации в ячейку памяти необходимо установить потенциалы на разрядных входах 12 и 13 вводимой информации: на одном — низкий (приблизительно нулевой) а на другом — высокий (приблизительно потенциал источника питания +U ). При увеличеин нии потенциала на адресном входе 11 35 до высокого уровня открываются транзисторы 5 и б и в узле триггера, подключенном к разрядному входу с низким потенциалом, устанавливается низкий потенциал, а в другом узле — 40 высокий потенциал.

При этом триггер переключается в соответствующее состояние.

При считывании информации потенциал на адресном входе изменяется так 45 же, как и при записи. Разрядные входы в начале считывания обычно имеют высокий потенциал. Рассмотрим слу33 2 чай, когда потенциал còîêë транзистора 1 низкий, а потенциал ст ха транзистора 2 — высокий. В этом случае на разрядном входе 12 появляется сигнал считывания в результате протекания тока по цепи последовательно включенных открытых транзисторов 5 и и 1.

При этом увеличивается потенпиал стока транзистора 1, что может привести к ложному переключению триггера. Благодаря введенному конденсатору 8 повышается потенциал стока транзистора 2 и затвора транзистора 1, что приводит к уменьшению эффективного" сопротивления транзистора 1 по сравнению с известным устройством и к снижению вероятности ложного переключения триггера. Наличие конденсатора 7 не приводит к росту потенциала стока транзистора 1 из-за очень малой постоянной времени разряда конденсатора 7 через открытый транзистор 1, в то же время потенциал стока транзистора 2 уменьшается медленно, так как разряд конденсатора 8 происходит через резистор 4, имеющий большое сопротивление.

Формула и з о б р е т е н и я

Ячейка памяти, содержащая триггер и первый и второй коммутирующие элементы, каждый из которых выполнен на ИДП-транзисторе, истоки МДП-транзисторов соединены с соответствующими входами-выходами триггера, стоки являются соответствующими разрядными входами, а затворы — адресным входом ячейки памяти, о т л и ч а ю щ а я с я тем, что, с целью повышения помехозащищенности, в нее введены первый и второй зарядные элементы, каждый из которых выполнен на конденсаторе, выводы которого соединены с затвором и истоком ИДП-транзистора соответствующего коммутирующего элемента.

1285533

12

Составитель А.Дерюгин

Редактор А.Шишкина Техред Л.Олейник корректор Е.Сирохман

Заказ 7532/54 Тираж 589 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4