Измеритель частоты

Иллюстрации

Показать всеРеферат

Изобретение относится к радиотехнике и предназначено для измерения частоты гармонического сигнала. Цель изобретения - повьшение быстродействия устройства. Измеритель частоты содержит линию 1 задержки и перемножитель 2. Введение в устройство сумматора 3, делителя 4, ключа 5, фиксирующей цепи 6, блоков 7 и 10 нелинейного преобразования, линии 8 задержки, перемножителя 9, компаратора 11 и образование новых функциональных связей исключает влияние амплитуды входного сигнала на величину оценки частоты. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН (19) (11) (51) 4 G 01 R 23 00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ,» "

Фиг. f

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

К А ВТОРСКОМ,Ф СВИДЕТЕЛЬСТВУ (21) 3907844/24-21 (22) 11.06.85 (46) 30.01.87. Бюл. ¹ 4 (71) Уральский политехнический институт им.С.М.Кирова (72) А.А.Калмыков, Н.П.Никитин, В.И.Лузин и В.A.Äoáðÿê (53) 621.3 17 (088.8) (56) Авторское свидетельство СССР № 581439, кл.G 01 R 23/00, 1976.

Авторское свидетельство СССР № 600461, кл. С 01 R 23/00, 1973.

Качанов. Системы автоматического регулирования в радиопередатчиках.

M.: Связь, 1969, с.232. (54) ИЗМЕРИТЕЛЬ .ЧАСТОТЫ (57) Изобретение относится к радиотехнике и предназначено для измерения частоты гармонического сигнала °

Цель изобретения — повышение быстродействия устройства. Измеритель частоты содержит линию 1 задержки и перемножитель 2. Введение в устройство сумматора 3, делителя 4, ключа

5, фиксирующей цепи 6, блоков 7 и 10 нелинейного преобразования, линии 8 задержки, перемножителя 9, компаратора ll и образование новых функциональных связей исключает влияние амплитуды входного сигнала на величину оценки частоты. 1 ил.

1? 87028 2 при t < О, О

U !! при Ъ2!, . при !,, при t>7> °

1 Ui!

arccos

II Э

cosset, +cps (2ut-(Ê ) при при (,3 1: 2 3 при t>2!.> .

1+соз2и(с- )

2соз указ

Изобретение относится к радиотехнике и предназначено для измерения частоты гармонического сигнала.

Целью изобретения является повышение быстродействия измерителя частоты.

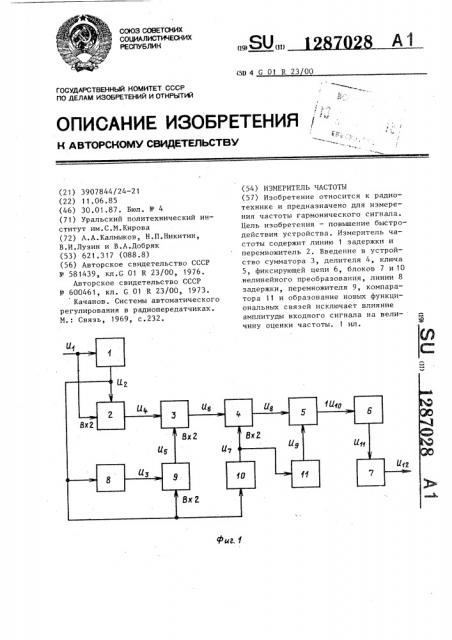

На фиг.1 изображен измеритель частоты; на фиг.2 — временные диаграммы, поясняющие работу устройства.

Измеритель частоты содержит последовательно соединенные первую линию задержки 1 и первый перемножитель 2, второй вход которого соединен с входом первой линии задержки 1, последовательно соединенные сумматор 3, делитель 4, ключ 5, фиксирующую цепь

6 и первый блок нелинейного преобразования 7, при этом между выходом первой линии задержки 1 и вторым входом сумматора 3 включены последовательно соединенные вторая линия задержки 8 и второй перемножитель

9,.а между выходом первой линии задержки 1 и управляющим входом ключа

5 включены последовательно соединенные второй блок нелинейного преобразования 10 и компаратор 11, причем второй вход второго перемножителя 9 соединен с выходом первой линии задержки 1, а второй вход делителя 4 соединен с выходом второго блока .нелинейного преобразования 10.

Измеритель работает следующим образом.

Пусть на вход измерителя подается сигнал

Ucoscat npu t > О.

Второй блок нелинейного преобразования возводит в квадрат входное напряжение.

Сигнал на выходе второго блока нелинейного преобразования 10

U = т — !1i-сов (2ld(t- l,)j

Сигнал на выходе делителя 4

На вход измерителя вместе с сигналом U!, частоту которого необходимо оценить, всегда поступают шумы.

Эти шумы, пройдя соответствующие цепи, поступают на первый и второй входы делителя 4. В моменты времени

t (фиг.2) HsnpSReHHH Ug H U поступающие на входы делителя 4, определяются шумами и на выходе делителя 4 могут сформироваться выбросы напряжения, так как возможны случаи, когда величина шумового напряжения

U (знаменатель) значительно меньше ! величины шумового напряжения U< (числитель). Для исключения таких выбросов в схему измерителя между делителем частоты 4 и первым блоком нелинейного преобразования 7 введены последовательно соединенные ключ 5 и фиксирующая цепь 6, причем управляющий вход ключа через компаратор 11 подключен к выходу второго блока нелинейного преобразования 10. Эта часть схемы работает следующим образом. В моменты времени, близкие к и tz срабатывает компаратор 11 и формирует на своем выходе прямоугольный импульс U, который размыкает ключ 5. Этим самым выбросы напряжения на выходе делителя 4 не проходят к входу первого блока нелинейного преобразования 7. Фиксирующая цепь 6 запоминает вепичину напряжения U на выходе ключа 5 в момент его размыкания и сохраняет эту величину до момента следующего замыкания ключа 5.

Таким образом, на вход первого блока нелинейного преобразования 7 поступает напряжение Un беэ шумовых выбросов. Величина напряжения UI! определяется как

О при

cosQ< +сов(2G3t — я g)

"+cos2u(t "э) прис t 2ь,, 2cos и, Первый блок нелинейного преобразования осуществляет преобразование входного напряжения U в соответствии с алгоритмом

Учитывая выражение для U!ö I, можно записать, что при > 2с>

Б = д/2 !! т.е. напряжение на выходе предлагаемого измерителя оказывается равным частоте входного сигнала. Время измерения .частоты составляет 2 ь> !!

При выборе времени задержки а <в

4) 1287028 время измерения частоты входного сигнала может быть сделано меньше периода колебаний сигнала. и, О и>

О и

О и>

О на

Ug

О

Пу

Фиг. 2

Составитель Н. Губанов

Техред N.Õoäàíè÷ Корректор А.Обручар

Редактор Т.Парфенова

Заказ 77 11/46

Тираж 730 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r.Óæãoðoä, ул.Проектная,4.

В предлагаемом измерителе величина оценки частоты не зависит от амплитуды входного сигнала.

Формула и з о б р е т е н и я

Измеритель частоты, содержащий последовательно соединенные первую линию задержки и перемножитель, второй вход которого соединен с входом первой линии задержки, о т л и ч аю шийся тем, что, с целью повышения быстродействия измерителя, к выходу перемножителя подсоединены последовательно соединенные сумматор, делитель, ключ. фиксирующая цепь и первый блок нелинейного преобразования, при этом между выходом первой линии задержки и вторым входом сумматора включены последовательно соединенные вторая линия задержки и второй перемножитель, а между выходом первой линии задержки и управляющим входом ключа включены последовательно соединенные второй блок нелинейного преобразования и компаратор, причем второй вход второго перемножителя соединен с выходом первой линии задержки, а второй вход делителя соединен с выходом второго блока нелинейного пре образования. I