Формирователь сложной функции

Иллюстрации

Показать всеРеферат

Изобретение относится к цифровой вычислительной технике и может быть использовано в цифровых вычислительных комплексах, устройствах автоматики и вычислительной технике. Целью изобретения является расширение функциональных возможностей формирователя за счет реконфигурации каналов выдачи сложной функции. Формирователь сложной функции содержит блок 1 управления, регистр 2 информации, демультиплексор 3, регистр 4 адреса, генератор 5 тактовых импульсов,счетчик 6, группу из N блоков 7.1...7.N оперативной памяти, коммутатор 8, N-1 сумматоров 12.1 ... 12 (N-1), регистр 13 Настройки. Формируемая функция может быть преобразована в аналоговую форму с помощью цифроаналоговых преобразователей 11.1 ... 11.N в каждом из N каналов. 2 ил. с

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК 511 4 0 06 F 1/02

ОПИСАНИЕ ИЗОБРЕТЕНИЯ ! й:;; °

-«« ° «««.

Н А ВТОРСНОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21 ) 3952208/24-24 (22) 13.09,85 (46) 30.01.87. Бюл, Е 4 (72) В.А.Мельников, П.И.Кныш и С.И.Ряполов (53) 681.325 (088.8) (56) Авторское свидетельство СССР

К- 995312, кл. Н 03 К 13/02, 1981.

Авторское свидетельство СССР

11 1075400, кл. Н 03 К 13/02, 1982. (54) ФОРМИРОВАТЕЛЬ СЛОЖНОЙ ФУНКЦИИ (57) Изобретение относится к цифровой вычислительной технике и может быть использовано в цифровых вычислительных комплексах, устройствах автоматики и вычислительной технике.

„„80„„1287135 A1

Целью изобретения является расширение, функциональных возможностей формирователя за счет реконфигурации каналов выдачи сложной функции. Формирователь сложной функции содержит блок

1 управления, регистр 2 информации, демультиплексор 3, регистр 4 адреса, генератор 5 тактовых импульсов, счетчик 6, группу из N блоков 7.1...7.N оперативной памяти, коммутатор 8, И-1 сумматоров 12. 1 ... 12 (N-1), регистр 13 йастройки. Формируемая функция может быть преобразована в аналоговую форму с помощью цифроаналоговых преобразователей 11. 1

11.N в каждом из N каналов. 2 ил.

128713

Изобретение относится к цифровой вычислительной технике и может быть использовано в цифровых вычислительных комплексах, устройствах автоматики и вычислительной техники. 5

Целью изобретения является расширение функциональных возможностей формирователя за счет реконфигурации каналов выдачи сложной функции.

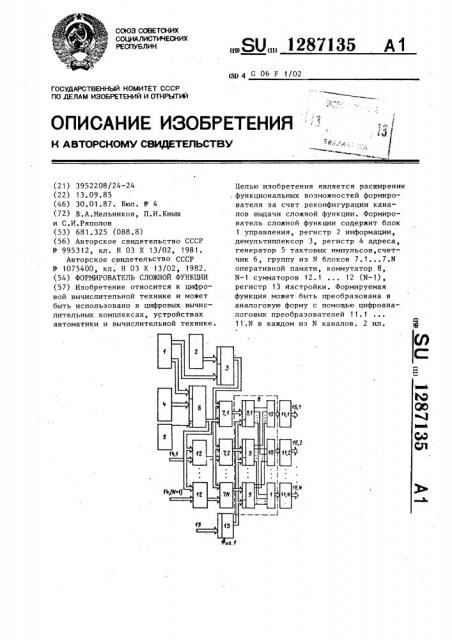

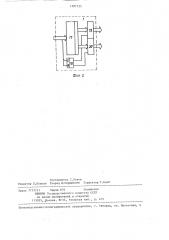

На фиг. 1 представлена функциональная схема формирователя сложной функции на фиг. 2 — схема блока управления.

Формирователь сложной функции (фиг. 1) содержит блок 1 управления (БУ), регистр 2 информации, демультиплексор 3, регистр 4 адреса, генератор 5 тактовых импульсов, счетчик 6, группу из N блоков оператив- ной памяти 7.1 — 7.N, коммутатор 8> содержащий И демультиплексоров 9.1

9.N u N элементов ИЛИ 10.1 — 10 N, N цифроаналоговых преобразователей

11.1 — 11,N (N-1) сумматоров 12.1

12 (М-1), регистр 13 настройки, вход25 ные шины 14.1 — 14 (N — 1), управляющий вход 15, выходные шины 16.1

16.N формирователя. !

Демультиплексор 9. (i=i, N) co- gg держит дешифратор и блок элементов И.

В зависимости от кода настройки, поступающего на управляющий вход демультиплексора, информация со входа поступит на один из N выходов демультиплексора.

Блок 1 управления (фиг. 2) содержит регистр 17 управления, триггер

18 режима (работы), первую 19 н вторую 20 группы элементов И. 40

Формирователь сложной функции работает следующим образом, Устройство может функционировать в двух режимах: "Подготовка" и "Работа". 45

Режим "Подготовка > используется для занесения информации, соответствующей воспроизводимым функциям, в блоки оперативной памяти 7.1 — 7.N и устанавливается единичным сигналом на первом выходе блока 1 управления.

Выбор режима функционирования формирователя определяется поступлением управляющего сигнала на один из входов триггера 18 режима работы. Так, в режиме "Подготовка" триггер 19 режима устанавливается в единичное состояние. В результате этого сигнал логической 1" с единичного выхода

5 2 триггера 18 режима разрешает прохождение информации с выхода регистра

17 управления на управляющий вход демультиплексора 3 через группу элементов И 20. При этом в счетчик 6 из регистра 4 адреса заносится код адреса ячейки, в которую необходимо занести информацию. Содержимое счетчика 6 подается на адресный вход оперативного запоминающего блока 7.1 и через сумматоры 11.1 — 11 (М-1) — на адресные входы блоков оперативной памяти

7.2 — 7.N, В режиме "Подготовка" на входные шины 14.1 — 14 (N-1) формирователя подается комбинация "все нули".

Информация, которую необходимо занести в соответствующую ячейку одного из оперативных запоминающих блоков

7.1 — 7.N с адресом, установленным в счетчике 6, с выхода регистра 2 через демультиплексор 3 поступает на вход одного из блоков 7.1

7.N. Номер же запоминающего блока, в который заносится информация, определяет регистр 17 управления блока 1.

Режим "Работа" начинается при приведении триггера 18 режима работы блока 1 управления в нулевое состояние.

При этом счетчик 6 начинает работать в счетном режиме (на фиг. 1 цепи запуска генератора 5 тактовых импульсов не показаны).

Блоки 7. 1 — 7.N начинают функционирование в режиме "Считывание", Выходной код счетчика поступает на адресный вход блока 7.1. На адресные входы блоков 7.2 — 7.N подаются коды с выходов сумматоров 11 ° 1

11 (N 1),.êîòîðûå являются суммой выходного кода счетчика 6 и управляющих кодов, подаваемых на соответствующие входы 14.1 — 14.(N-1) формирователя.

При формировании периодических функций с периодом Т, управление фазой каждой функции на выходах блоков 7.2 — 7.N может производиться с дискретом Т/2n, где п — разрядность адресного кода, путем изменения управляющих кодов, подаваемых на входные шины 14.1 — 14 (N-1) формирователя.

Набор воспроизводимых функций можно менять, программируя соответствующим образом блоки 7.1 — 7.N.

Управление фазами воспроизводимых функций может осуществляться непре1287135 рывно в процессе работы устройства, 11 ll а занося перед режимом Работа в счетчик 6 определенный код, можно воспроизводить по первому каналу (блок 7.1) устройства функцию с любой начальной фазой, соответствующей этому коду.

При необходимости выдачи функции с одних каналов в другие на управляющий вход 15 устройства подается соответствующий код настройки. Код настройки с выхода регистра 13 настройки поступает на управляющие входы коммутатора 8. На соответствующем дешифраторе каждого из демультиплексоров 8.1-8.N код настройки преобразуется иэ позиционного в унитарный, т.е. для каждого кода дешифратор определяет необходимый выходной канал. Коммутатор 8 осуществляет перестроение выходных каналов в зависимости от кода настройки, поступающего с выхода регистра 13 настройки. Это позволяет, имея программы сложной функции в одних каналах, воспроизводить их (или прекращать выполнение) по другим каналам. Такой режим работы позволяет расширить область применения формирователя, так как любой канал может отрабатывать все множество программ сложных функций.

Формула изобретения

Формирователь сложной функции, содержащий генератор тактовых импульсов, регистр, адреса, счетчик, блок управления, первый блок .оперативной памяти, регистр информации, (И-1) сумматоров, причем выход регистра адреса подключен к информационному входу счетчика, счетный вход которого подключен к выходу генератора тактовых импульсов, вход

f0

45 управления режимом работы счетчика подключен к первому выходу блока управления, выход счетчика подключен к адресному входу первого блока оперативной памяти и к первым информационным входам (М-1) сумматоров, вторые информационные входы которых подключены к (N-1) информационным входам формирователя соответственно, о т— л и ч а ю шийся тем, что, с целью расширения функциональных воэможностей за счет реконфигурации каналов выдачи сложной функции, в него введены (N-1) блоков оперативной памяти, демультиплексор, регистр настройки, коммутатор, причем выход

i-ого сумматора (i = 1 — N — 1) подключен к адресному входу i+1-ого блока оперативной памяти, выход К-го (К= 1, N). блока оперативной памяти подключен к К-ому информационному входу коммутатора, управляющий вход которого подключен к выходу регистра настройки, информационный вход которого подключен к входу настройки формирователя, второй выход блока управления подключен к входу управления демультиплексора, информационный вход которого подключен к выходу регистра, информационный выход демультиплексора подключен к информационным входам

К блоков оперативной памяти, К выходов коммутатора подключены к К информационным выходам формирователя соответственно, причем блок управления содержит регистр управления, триггер режима, две группы элементов И, причем прямой выход триггера режима подключен к первым входам элементов И первой группы, вторые входы которых подключены к выходам старших разрядов регистра управления, выходы младших разрядов которого подключены к прямым входам элементов И второй группы, вторые входы которых подключены к инверсному выходу триггера режима.

Составитель С.Курош

Редактор Л.Повхан Техред Л.Сердюкова Корректор Т.Колб

Заказ 7717/51 Тираж 670 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, -MocKBa, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4