Узел формирования переноса в сумматоре

Иллюстрации

Показать всеРеферат

Изобретение относится к области автоматики и вычислительной техники. Цель изобретения - упрощение узла формирования переноса в сумматоре. Узел содержит шесть МДП-транаисторов р-типа, шесть МДП-транзисторов п-типа и два инвертора. Узел формирования переноса в сумматоре работает в режиме формирования собственного переноса и в режиме формирования сквозного переноса. 1 ил., 1 табл.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (504G 06 F 7 50

ОПИСАНИЕ ИЗОБРЕТЕНИЯ:-К А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3950069/24-24 (22) 04,09.85 (46) 30,01.87. Бюл, № 4 (72) В, А, Максимов, Я. Я. Петричкович, А. E. Заболотный и С. Н. Косоусов (53) 681.325.5(088.8) (56) Патент Японии № 54-42573» кл. G 06 F 7/59, 1979.

Авторское свидетельство СССР

¹ 1177809, кл. G 06 F 7/50, 1984.

„„SU„„1287147 А 1 (54) УЗЕЛ ФОРМИРОВАНИЯ ПЕРЕНОСА В

СУММАТОРЕ (57) Изобретение относится к области автоматики и вычислительной техники.

Цель изобретения — упрощение узла формирования переноса в сумматоре.

Узел содержит шесть МДП-транзисторов р-типа, шесть МДП-транзисторов и-типа и два инвертора. Узел формирования переноса в сумматоре работает в режиме формирования собственного переноса и в режиме формирования сквозного переноса. 1 ил., l табл.!

287147

11зобретение относится к выччслительной технике и электронике и может быть использовано при построении арифметико-логических устройств обработки цифровой информации, в частности при построении многоразрядных сумматоров в качестве элемента цепи ускоренного переноса.

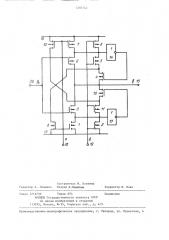

Цель изобретения — упрощение узла формирования переноса в сумматоре, На чертеже представлена схема уз— ла формирования переноса в сумматоре, Узел формирования переноса в сумматоре содержит первый 1, второй 2, третий 3, четвертый 4, пятый 5 и шес- 15 той 6 МДП-транзисторы и-типа„ первый

7, второй 8, третий 9, четвертый 10, пятый 1! и шестой 12 МДП-транзисторы р-типа, элементы НЕ 13 и 14, выход 15 переноса, шину 16 питания, шину 17 нулевого потенциала, входы 18 и 19 соответствующих разрядов первого и второго операндов и вход 20 переноса.

Узел формирования переноса в сумматоре работает в режиме формирования собственного переноса и в режиме формирования сквозного переноса, Соответствующий режим работы определяется комбинацией сигналов на входах

18 и 19 слагаемых. При комбинации . 30 сигналов на входах 18 и 19 "00" или

"11" схема находится в режиме формирования собственного переноса, на выходе 15 формируется сигнал, инверсный по отношению к сигналам слагае— мых. При равенстве нулю сигналов слагаемых а=О, b=0 закрытые МДП вЂ” тран— зисторы и-типа 1, 2 и 6 не препятствуют формированию на входах первого

13 и второго 14 элементов HE логи40 ческих единиц через открытые транзисторы 12, 11, 8 и 7, В этом случае на выходе схемы 15 формируется уровень логической единицы через открытый по

45 затвору логическим нулем с выхода первого элемента НЕ 13 транзистор 10, Дополнительная цепь формирования логической единицы на выходе 15 образована одним из открытых транзисторов 9 (р,=О) или 3 (р =1)., Учитывая дуальность схемы по отношению к входным сигналам, характер функционирования узла формирования переноса в случае равенства единице сигналов слагаемых а=1, b=! аналоги55 чен рассмотренному, т,е, на выходе

15 формируется уровень логического нуля.

При противоположных значениях сигналов слагаемых а=Ь узел находится в режиме формирования сквозного переноса, При комбинации сигналов на входах !8 и 19 соответственно "О" и "1" закрытые транзисторы 6 и 11 не препятствуют транзисторам 7 и 11 соответственно формировать на их стоках логические уровни соответственно "1" и "О ", При этом первый 13 и второй 14 элементы НЕ формируют уровни соответственно 11 и О, запирающие транзисторы !О и 4. Транзисторы 9 (если р, =О) или 3 (если р, =1) формируют на выходе 15 сигнал, инверсный сигналу, установленному на входе 20 переноса, Работа узла формирования переноса в сумматоре иллюстрируется таблицей состояний транзисторов и соответствующим этим состояниям логическим значениям выхода 15 переноса °

Таким образом, узел формирования переноса в сумматоре реализует булеву функцию

p=ab+apÄ +bp,, где а, b p — сигналы на входах 18, 19 и 20 соответственно.

Формула и з о б р е т е н и я

Узел формирования переноса в сумматоре, содержащий в каждом разряде первый, второй, третий и четвертый

МДП-транзисторы р-типа, первый, вто— рой, третий, четвертый МДП-транзисторы п-типа, первый элемент НЕ, причем истоки первого и второго МДПтранзисторов р-типа соединены с шиной питания узла, истоки первого и второго МДП-транзисторов п-типа соединены с шиной нулевого потенциала узла, затворы первого МДП-транзистора р-типа и первого МДП-транзистора и †ти соединены с входом соответствующего разряда первого операнда узла, стоки первого МДП-транзистора р-типа и первого МДП-транзистора и-типа соединены соответственно с истоками, третьего МДП-транзистора-.-. р-типа и третьего МДП-транзистора п-типа, стоки третьего и четвертого

МДП-транзисторов р-типа и стоки третьего и четвертого МДП-транзисторов и-типа соединены с выходом переноса в следующий разряд узла формирования переноса, о т л и ч а ю ш и и с я

1287147 тем, что, с целью упрощения, в каждый его разряд введены пятый и шестой МДП-транзисторы р-типа, пятый и шестой ИДП-транзисторы п-типа, вто— рой элемент НЕ, причем затворы третьих ИДП-транзисторов р-типа и п-типа соединены с входом переноса из предыдущего разряда узла, сток первого МДП-транзистора р-типа соединен со стоком второго ИДП-транзистора 10 р-типа, истоком пятого ИДП-транзистора и-типа и входом первого элемента НЕ, выход которого соединен с затвором четвертого МДП-транзистора п-типа, сток первого МДП-транзистора п-типа соединен со стоком второго

МДП-транзистора п-типа, истоком пя— того МДП-транзистора р-типа и входом второго элемента НЕ, выход которого а Ь р Открытые транзис- Закрытые транзис- Выход о э торы торы

2,1,6,4,5,3

2,1,6,4,5,9

11,16,10,8,3,4 с 11,16,10,8,9,4

7,12,2,5,10,3,4

7,12,2,5,10,9,4

7,12,11,8,10,3

7,12,11,8,10,9

1,6,2,5,9,4

1,6,2,5,3,4

0 0 0

0 0 1

0 l 0

0 1 1

1 . 0 0

1 0 1

1 1 0

1 1 1

8,7,12,11,10,9

8,7,12,11,10,3

5,7,12,2,9

5,7,12,2,3

1,6,8,11,9

1 6,8,11,3 соединен с затвором четвертого ИДПтранзистора р-типа, исток которого соединен со стоками пятого и шестого

МДП вЂ транзистор р-типа, исток четвертого ИДП-транзистора и-типа соединен со стоками пятого и шестого

МДП-транзисторов п-типа, затворь1 второго и пятого МДП-транзисторов р-типа соединены с затворами второго и пятого ИДП-транзисторов и-типа и с входом соответствующего разряда второго операнда узла, затворы шестых

МДП-транзисторов и-типа и р-типа соединены с входом соответствующего разряда первого операнда узла, истоки шестых ИДП-транзисторов р-типа и и-типа соединены соответственно с шинами питания и нулевого потенциала узла, 1287)47

Составитель И, Есенина

Редактор А, Лежнина Техред Л.Олейник

Корректор М, Пожо

Заказ 7718/50 Тираж 694

ВКИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д, 4/5

Подписное

11роизводственно-полиграфическое предприятие, r, Ужгород, ул, Проектная, 4