Устройство микропрограммного управления

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в устройствах управления ЭВМ. Целью изобретения является повышение быстродействия устройства. Устройство содержит нультиплексор, регистр адреса, блок памяти микрокоманд , блок оперативной памяти, блок приращения, депшфратор, триггер, реверсивный счетчик, группу элементов И. Поставленная цель достигается за счет обеспечения перехода из подпрограммы любого уровня сложности в главную программу с дальнейшим возвратом в подпрограмму. 2 ил. с S (Л

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

А1

„.SU„„ ц11 4 С 06 F 9/22

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АВТОРСНОМ,Ф СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ . (21) 3849342/24-24 (22) 24.01.85 (46) 30.01.87. Вюл. N- 4 (71) Казанский авиационный институт им. А.Н.Туполева и Ульяновское конструкторское бюро приборостроения (72) В.А.Макушин, 10.Л.Масленников, Л.П.Губарев и А.С.Мандрак (53) 681.325 (088.8) (56) Авторское свидетельство СССР

У 477411, кл. G 06 F 9/46, )975.

Авторское свидетельство СССР

N- 544965, кл. G 06 F 9/22, 1977.

Патент США Ф 390979, кл. G 06 F 9/22, 1976. (54) УСТРОЙСТВО МИКРОПРОГРАММНОГО

УПРАВЛЕНИЯ (57) Изобретение относится к вычислительной технике и может быть использовано в устройствах управления

ЭВМ. Целью изобретения является повьппение быстродействия устройства.

Устройство содержит . льтиплексор, регистр адреса, блок памяти микрокоманд, блок оперативной памяти, блок приращения, дешифратор, триггер, реверсивный счетчик, группу элементов И. Поставленная цель достигается за счет обеспечения перехода из подпрограммы любого уровня сложности в главную программу с дальнейшим возвратом в подпрограмму. 2 ил.

87154 2

S0

1 12

Изобретение относится к вычислительной технике и может быть использовано в устройствах управления ЭВМ, в частности при проектировании дисплейных процессоров, Целью изобретения является повышение быстродействия устройства.

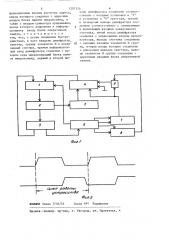

На фиг.1 представлена структурная схема предлагаемого устройства; на фиг.2 — последовательность синхроимпульсов, необходимая для синхронизации устройства.

Устройство содержит мультиплексор

1, регистр 2 адреса, блок 3 памяти микрокоманд, блок 4 оперативной памяти, сумматор 5 приращения, дешифратор 6, триггер 7, реверсивный счетчик 8, группу элементов И 9. Сумматор 5 приращения представляет собой схему, реализующую функцию увеличения входной информации на постоянную величину.

Синхронизация .устройства осуществляется от двухфазного генератора, вырабатывающего две синхропоследовательности Т и Т .

Устройство работает следующим образом.

В набор микрокоманд устройства кроме микрокоманд нПереход к подпрограмме" и "Возврат из подпрограммы" вводятся микрокоманды Переход в главную программун и "Возврат в программу", для обработки которых, собственно, и предназначены дешифратор 6, триггер 7, реверсивный счетчик 8 и группа элементов И 9.

Цикл работы устройства начинается с появлением переднего фронта фазы

Т . По переднему фронту Т, производится запись в регистр 2 адреса очередной микрокоманды. С некоторой задержкой от переднего фронта Т, с выходов блока 3 памяти микрокоманд появляется код микрокоманды, который поступает на дешифратор 6 и первый вход мультиплексора 1. Фаза Т слу2 жит для задания режима работы блока

4 оперативной памяти и управления реверсивным счетчиком 8 и триггером 7.

На всем протяжении положительного импульса фазы Т блока 4 находятся

2 в режиме записи и переписывают содержимое регистра 2, увеличенное на единицу, все остальное время блок

4 находится в режиме считывания. Запись и чтение осуществляются в ячейке, адрес которой задается реверсивным счетчиком 8, если триггер 7 сбро5

1О

35 шен в О" и в ячейке с адре.-.ом О, если триггер 7 установлен в "!".

Увеличение и уменьшение содержимого реверсивного счетчика 8, а также установка и сброс триггера 7 осуществляются задним фронтом фазы Т

Д т.е, их состояние изменяется в конце цикла работы устройства после записи в блок 4 оперативной памяти.

Рассмотрим работу устройства при переходе к подпрограмме. Микрокоманда "Переход к подпрограмме" занимает в блоке памяти микрокоманд одно слово и содержит код микрооперации и адрес первой микрокоманды подпрограммы. Допустим содержимое регистра 2 равно А, это — адрес микрокоманды

"Переход к подпрограмме". Адрес первой микрокоманды подпрограммы В. При этом содержимое реверсивного счетчика 8 равно "О" и триггер 7 также обнулен, что соответствует выбору в блоке 4 ячейки с адресом О.

Сумматор 5 приращения производит приращение содержимого регистра 2 и, на информационный первый вход блока

4 поступит код А+1. По фазе Т этот

2 код запишется в нулевую ячейку блока 4, что соответствует запоминанию адреса возврата. С выхода кода микроопераций блока 3 памяти микрокоманд на вход дешифратора 6 поступает комбинация, соответствующая разрешению приращения реверсивного счетчика 8 на единицу.

По заднему фронту фазы Т: содержимое счетчика 8 становится равным единице, а в ячейке с адресом О за— поминается адрес возврата. С появлением на выходе блока 3 памяти микрокоманд микрокоманды Переход к подпрограмме мультиплексор 1 переключает вход регистра 2 с выхода блока 4 на адресный выход блока

3 памяти микрокоманд.. Тогда в следующем цикле в регис тре 2 по переднему фронту фазу Т„будет загружен код В. В первую ячейку блока 4 запишется код В+1 и произойдет обратное переключени е мультиплексора 1 .

Таким образом, за один цикл работы устройства произошло запоминание адреса возврата в ячейке блока

4 н переход к первой микрокоманде подпрограммы. Переход из этой подпрограммы в следующую реализуется аналогично. Адреса возврата будут храниться н нулевой и перной яч ейк 7154

Для реализации микрокоманд Переход в главную программу" и Возврат в подпрограмму" служит триггер 7, который коммутирует адресные входь! блока 4 через группу элементов И 9 с выходами счетчика 8. Если триггер

7 сброшен, на адресный вход подается содержимое реверсивного счетчика

8, при ; .тановке триггера 7 адрес становится равным О, что соответствует обращению к ячейке блока 4, в которой хранится адрес возврата в главную программу. Вставив в подпрограмму любого уровня вложености микрокоманду «Переход в главную про«« грамму, можно временно прервать ее выполнение и вернуться в главную программу, при этом содержимое реверсивного счетчика 8 не изменится, а в ячейке блока 4 с адресом, на который указыва ет реверсивнь«й счетчик 8, сохранится адрес микрокомандь«, сле50

3 !28 блока 4, а содержимое реверсивного счетчика 8 станет равным двум.

Возврат из подпрограммы происходит по микрокоманде "Возврат из подпрограммы, являющейся последней микрокомандой подпрограммы.

Допустим, обрабатывается подпро-грамма первого уровня вложенности, начальный адрес которой равен В, по адресу В+3 находится "Возврат, содержимое реверсивного счетчика 8 равно единице, адрес возврата хранится в ячейке блока 4 с адресом О.

По переднему фронту фазы Т, адрес микрокоманды « Возврат«« В+3 заносит— ся в регистр 2 и с некоторой задерж— кой на выходе блока 3 памяти микрокоманд появляется код микрокоманды

"Возврат". На вход дешифратора 6 поступает кодовая комбинация, соответствующая разрешению уменьшения

r содержимого реверсивного счетчика

8 на единицу, и к началу следующе— го такта из блока 4 будет считываться ячейка с адресом О, в которой хранится адрес возврата, для нашего примера равный А+1, который в следующем цикле по переднему фронту фазы

И, запишется в регистр 2. При отработке микрокоманды "Возврат из подпрограммы « по фазе Т в первую ячей2 ку блока 4 был занесен код В+4, это свойство используется в дальнейшем для обработки микрокоманд "Переход в главную программу" и Возврат в подпрограмму".

f5

45 дуюп(!«Й за !«Нот руки«! сй IIpp E Yojl, в главную программу, что позволяет в свою очередь передать управление из главной программы в подпрограмму, из которой произошел переход.

Допустим, выполняется подпрограмма второго уровня вложенности по адресу С в этой подпрогра«ме находится микрокоманда Переход в главную программу« . По переднему фронту фазы Т, адрес С заносится в регистр

2, и с некоторой задержкой на выходе блока 3 памяти появится код микрокоманды Переход в главную программу

При этом на вход дешифратора 6 поступает кодовая комбинация, разрешая установку триггера 7 в единичное состояние. Установка триггера производится по заднему фронту фазы

Т . Заметим, что в ячейке блока 4, на которую указывает реверсивный счетчик 8, после окончания фазы Т будет храниться код, равный С+1, т.е. адрес следующей микрокоманды подпрограммы. Установка триггера 7 в единичное состояние приводит к поступлению на адресные входы блока

4 логического нуля. Таким образом, по окончании фазы, в которой хранит"-ся адрес возврата в главную программу. В следующем цикле этот адрес по переднему фронту фазы Т, запишется в регистр 2.

После выполнения некоторых действий в главной программе (как правило это передача переменных параметров в устройство) можно вернуться обратно в подпрограмму на адрес С, Это происходит по микрокоманде "Возврат в подпрогра!!му, при выполнении которой производится установка триггера в нулевое состояние, что ведет к поступлению на адресные входы блока 4 содержимого реверсивного счетчика 8 через группу элементов И 9.

Ф о р м у л а и з о б р е т е н и я

Устройство микропрограммного управления, содержащее мультиплексор, регистр адреса, блок памяти микро— команд, блок оперативной памяти и сумматор приращения, причем первый информационный вход мультиплекс.ора соединен с адресным выходом блока памяти микрокоманд„второй информационный вход мультиплексора соединен с выходом блока оперативной памяти, выход мультиплексора соединен с инl 2871

ВНИИПИ Заказ 7718/52

Тираж 694 Подписное

Произв.-полигр. пр-тие, г. Ужгород, ул. Проектная, 4 формационным входом регистра адреса, выход которого соединен с адресным входом блока памяти микрокоманд, а также с входом сумматора приращения, выход которого подключен к информационному входу блока оперативной памяти, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия, в него введены дешифратор, триггер, группа элементов И и ревер- 10 сивный счетчик, причем информационный вход дешифратора соединен с выходом кода микроопераций блока памяти микрокоманд, первый и второй вы54 6 ходы дешифратора соединены соответ— ственно с входами установки в "1" и установки в О" триггера, третий и четвертый выходы дешифратора сое— динены соответственно с суммирующим и вычитающим входами реверсивного счетчика, пятый выход дешифратора соединен с управляющим входом мультиплексора, выходы счетчика соединены с первыми входами элементов И группы, вторые входы которых соединены с инверсным выходом триггера, выходы элементов И группы соединены с адресными входами блока оперативной памяти.