Устройство для контроля за ходом выполнения программы

Иллюстрации

Показать всеРеферат

Изобретение относится к цифровой вычислительной технике и может быть использовано при тестировании и отладке в реальном масштабе времени программного обеспечения цифровых вычислительных машин. Цель изобретения - расширение области применения устройства за счет обеспечения контроля хода программы с произвольной :структурой. Устройство для контроля за ходом выполнения программь содержит регистр 1 адресов команд переходов , дешифратор 2 кода операций, блоки 3 и 4 сравнения, буферные регистры 5 и 6, блоки 7 и 8 памяти прямых адресов , распределитель 9, коммутаторы 10 и 11, блоки 12 и 13 памяти косвенных адресов, коммутаторы 14, 15 и 16, регистр 17 текущего адреса, регистр 18 адреса данных, регистр 19 адреса, регистр 20 обмена и блок 21 равнозначности . Данное изобретение обеспечивает контроль хода по каждой ветви., программы и выявление всех ошибок переходов к незапланированным ветвям программы. 1 шт. Вх Икодне п п/хIffOffffS Ш (Л N9 00 sl Од Од

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

ÄÄSUÄÄ 1287166

А1 (51) 4 G 06 Р 11/28

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCHOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3954248/24-24 (22) 01.07.85 (46) 30.01.87. Бюл. Р 4 (72) А.Ф. Кирьяков, А. В. Королев, В.С.Пушкин, И.В.Лукашин и В.А.Горбатов (53) 681.3 (088. 8) (56) Авторское свидетельство СССР

Ф 807289, кл. G 06 F 11/00, 1978.

Авторское свидетельство СССР

У 1103238, кл. G 06 F 11/00, 1983 ° (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЗА ХОДОМ

ВЫПОЛНЕНИЯ ПРОГРАММЫ (57) Изобретение относится к цифровой вычислительной технике и может быть использовано при тестировании и отладке в реальном масштабе времени программного обеспечения цифровых вы1 числительных машин. Цель изобрете- ния — расширение области применения

Вх устройства за счет обеспечения контроля хода программы с произвольной

; структурой. Устройство для контроля за ходом выполнения программы содержит регистр 1 адресов команд переходов, дешифратор 2 кода операций, блоки 3 и 4 сравнения, буферные регистры

5 и 6, блоки 7 и 8 памяти прямых адресов, распределитель 9, коммутаторы

10 и 11, блоки 12 и 13 памяти косвенных адресов, коммутаторы 14, 15 и 16 регистр 17 текуцего адреса, регистр

18 адреса данных, регистр 19 адреса, регистр 20 обмена и блок 21 равнозначности. Данное изобретение обеспечивает контроль хода по каждой ветви . программы и выявление всех ошибок пе- реходов к незапланированным ветвям программы. 1 ил.

25

1 12871

Изобретение относится к цифровой вычислительной технике и может быть использовано при тестировании и отладке в реальном масштабе времени программного обеспечения цифровых вы- 5 числительных машин.

Цель изобретения — расширение области применения устройства за счет обеспечения контроля хода выполнения программы с произвольной структурой.

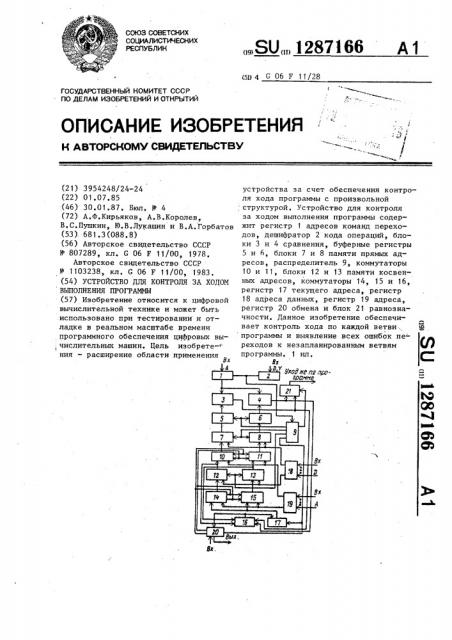

На чертеже приведена блок-схема предлагаемого устройства для контроля за ходом выполнения программы.

Устройство содержит регистр 1 арресов команд переходов, дешифратор 2. 15 кода операций, блоки.3 и 4 сравнения, буферные регистры 5 и 6, блоки 7 и 8 памяти прямых адресов (БПА), распределитель 9 (импульсов), коммутаторы

10 и 11, блоки 12 и 13 памяти косвен- 20 ных адресов, коммутаторы 14-16, регистр 17 текущего адреса, регистр 18 данных, регистр 19 адреса, регистр 20 рбмена и блок 21 равнозначности.

Устройство работает следующим образом.

В режиме загрузки блоков 7 и 8, 12 и 13 памяти в управляющие разряды регистра 20 от технологической ЗВИ заносится код 10. При этом коммутаторы 10 и 11, 14 и 15 подключают выходы регистра 19 адреса к адресным входам блоков 7 и 8, 12 и 13, на информационные входы блоков 7 и 8, 12 и 13 поступают данные с выхода регистра 18 данных. Загрузка осуществляется с помощью технологической ЭВИ, от которой адреса и данные поступают на входы регистров 18 и 19. После окончания процесса загрузки содержимое управляющих разрядов регистра 20 по директиве от технологической ЭВМ изменяется на код 01, переключая уст" ройство посредством коммутаторов 10 и 11, 14 и 15 в режим "Работа".

Таким образом, после анализа испытываемой программы и построения ее модели в виде ориентированного графа данный граф может быть задан двумя матрицами: матрицей А,. = //А. //, где А . физический адрес i-й команды перехода

i = 1,2,...,n; n — число команд- перехода в испытываемой программе; матрицей В структурных последова- тельностей А;, описывающей все возможные передачи управления в структуре rpaAa

Для графа дан пример вложения данных матриц в блоки 7 и 8, 12 и 13 памяти.

При исполнении, в ходе тестирования программ адреса команд запоминаются в регистре 1 адресов команд переходов. В случае выборки одной из команд, перехода на выходе дешифратора

2 будет сформирован сигнал чтения, по которому запускается распределитель 9 импульсов, представляющий из себя группу элементов задержки. В свою очередь на выходе распределителя 9 будут формироваться сигналы

"Чтения/Запись" в следующей последовательности: "Чтение" блоков 12 и 13;

"Чтение" блоков 7 и 8; "Запись" в регистры 5 и 6; "Запись" в регистры

17 и 20.

При этом алгоритм записи информации в регистры 5 и 6 о физических адресах последующих команд перехода будет следующим: по адресу, записанному в регистре

17 адреса (начальный адрес — 0000}, читается содержимое блоков 12 и 13 и блоков 7 и 8, по косвенным адресам (где косвенные адреса — индексы адресов команд переходов А, выбираемое из блоков 12 и

13) читается содержимое блоков 7 и 8; выбранная из блоков 7 и 8, информация записывается в регистры 5 и 6.

После записи информации о возможных направлениях ветвления программы в регистры 5 и 6, т.е. физических адресов А;, А . последующих команд перехода, на блоках 3 и 4 сравнения будет сравниваться содержимое регистра 1 с содержимым регистров 5 и 6. При этом на выходе блоков 3 и 4 будут формироваться сигналы или "0", "1" или

"1", "О",, т.е. будет определено одно из двух возможных направлений ветвления программы. С выходов блоков 3 и 4 информация "1", "О" или "0", "1" в зависимости от выбранного направления ветвления программы, поступит на вход коммутатора 16, подключая входы регистра 17 к выходам блока 12. После чего в регистры 17 и 20 будет записан

i-й индекс идентифицированной вершины А„ . После чего из регистра 20 информация об индексе ицентифицирован1287166 ной вершины будет переписана в память технологической ЭВМ.

Таким образом, каждый раз после записи в регистр 1 адреса текущей

KoMBHpbl перехода и определения напра- r вления ветвления программы в память технологической ЭВМ будет записан индекс очередной вершины графа. В результате в ходе выполнения программы в памяти технологической ЭВМ будет 10 записана последовательность индексов вершин rpaha, соответствующая входным значениям, поданным на управляющую

ЭВМ.

Таким .образом, основным состояни- 15 ем, фиксирующим уход программы по той или иной ветви, являются состояния выходов блоков 3 и 4 сравнения "0","1" или "1", "0", Очевидно, что при уходе программы в непредсказуемую разработ-2Р чиком область вычислений на выходах блоков 3 и 4 сравнения будет состояние несравнения "0", "0".

В случае, если переход будет произведен в область, которая не запланирована, то ни на одном из блоков 3 и 4 не будет единичного сигнала. Блок

21 равнозначности при появлении нулевых сигналов на его входах вырабатывает единичный сигнал, который поступит на выход устройства и укажет на неверный ход программ.

Формула изобретения

Устройство для контроля за ходом ,выполнения программы, содержащее регистр адресов команд переходов, дешифратор кода операций, первый и второй блоки сравнения, первый и вто- др рой буферные регистры, первый и второй блоки памяти прямых адресов, распределитель импульсов, причем входы адресов команд переходов и кодов операций устройства соединены соответственно с информационными входами регистра адресов команд переходов и дешифратора кода операций, выход которого соединен с входом записи регистра команд переходов и входом запуска распределителя импульсов, информационный выход регистра адресов команд переходов соединен с первыми входами первого и второго блоков сравнения, информационные выходы пер-55 вого и второго блоков памяти прямых адресов соединены с информационными входами соответственно первого и вто- рого буферных регистров, первый и второй выходы распределителя импульсов соединены соответственно с входом записи первого и второго буферных регистров и входом чтения первого и второго блоков памяти прямых адресов, о т л и ч а ю щ е е с я тем, что, с целью расширения области применения за счет обеспечения контроля хода выполнения программы с произвольной структурой, в устройство введены пять коммутаторов, первый и второй блоки памяти косвенных адресов, регистр адреса и регистр данных, регистр обмена, регистр текущего адреса и блок равнозначности, причем информационный вход и вход адресов модели хода программы соединены с информационными входами соответственно регистра данных и регистра адреса, первый выход которого соединен с первыми информационными входами первого и второго. коммутаторов, второй выход регистра адреса соединен с первыми информационными входами третьего и четвертого коммутаторов, выходы которых соединены с адресными входами соответственно первого и второго блоков памяти косвенных адресов, первый информационный выход регистра данных соединен с информационными входами первого и второго блоков памяти прямых адресов, второй информационный выход регистра данных соединен с информационными входами первого и второго блоков памяти косвенных адресов, третий выход распределителя импульсов соединен с входами чтения первого и второго блоков памяти косвенных адресов, информационный выход первого блока памяти косвенных адресов соединен с вторым информационным входом первого коммутатора и с пер-. вым информационным входом пятого коммутатора, информацибнный выход второго блока памяти косвенных адресов соединен с вторым информационным входом второго коммутатора и вторым информационным входом пятого коммутатора, выход которого соединен с информационными входами регистра текущего адреса и регистра обмена, четвертый. выход распределителя импульсов соединен с входом записи регистра обмена и регистра текущего адреса, выход которого соединен с вторыми информационными входами третьего и четвертого коммутаторов, первый и второй выходы регистра обмена соединены соответственно с первыми и вторыми входами

1287166

Составитель И.Сигалов

Техред А.Кравчук Корректор Е.СиРохман

Редактор IO.Ñåðåäà

Заказ 7719/53

Тираж 694 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4 первого, второго, третьего и четвертого коммутаторов, вход установки режима устройства соединен с информационным входом регистра обмена, третий выход которого является информационным выходом устройства, выход равенства первого блока сравнения соединен с первым входом блока равнозначности и первым управляющим входом пятого коммутатора, выход равенства второго блока сравнения соединен с вторым входом блока равнозначности и вторым управляющим входом пятого коммутатора, пятый выход распределителя им-пульсов соединен с третьим входом блока равнозначности, выход которого является выходом ошибки хода вычислительного процесса устройства.