Устройство для сопряжения двух процессоров через общую память

Иллюстрации

Показать всеРеферат

Изобретение относится к области вычислительной техники и предназначено для сопряжения процессоров через общую память в микропроцессорных системах . Реализация устройства требует незначительных аппаратурных затрат за счет соответствующего построения цепей синхронизации. Устройство содержит блок 1 оперативной памяти, мультиплексор 2 адреса, регистр 3, блок 4 синхронизации, триггер 5, элемент И 6 и двунаправленный шинный формирователь 7. В качестве сопрягаемых процессоров могут использоваться процессор системы и видеоконтроллер 8, в этом случае конструкция блока 4 упрощается. Обращение видеоконтроллера 8 в блок 1 за выборкой происходит с частотой вдвое больщей, чем необходимо для поддержания заданной скорости выдачи видеосигнала видеоконтроллером 8. Этим исключаются конфликты при обмене и достигается высокое качество изображения при сохранении скорости работы процессора системы. 2 ил. // C3f,CSLC32 о ж (Л с

СОЮЗ СОВЕТСНИХ СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (gg 4 G 06 F 12/16, 13/16

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCKOMV СВИДЕТЕЛЬСТВУ за счет соответствующего построения цепей синхронизации. Устройство содержит блок 1 оперативной памяти, мультиплексор 2 адреса, регистр 3, блок 4 синхронизации, триггер 5, элемент И 6 и двунаправленный шинный формирователь 7. В качестве сопрягаемых процессоров могут использоваться процессор системы и видеоконтроллер

8, в этом случае конструкция блока 4 упрощается. Обращение видеоконтроллера 8 в блок 1 за выборкой происходит с частотой вдвое большей, чем необходимо для поддержания заданной скорости выдачи видеосигнала видеоконтроллером 8. Этим исключаются конфликты при обмене и достигается высокое качество иэображения при сохранении скорости работы процессора системы.

2 ил. (21) 3965237/24-24 (22) 19. 07. 85 (46) 30.01.87. Бюл. ? 4 (71) МГУ им. M.Â.Ëîìîíîñîâà (72) И.Г.Персианцев, Н,Н.Рой, А.В.Скурихин и О.А.Щербаков (53) 681.325(088.8) (56) TRS-80, Model 3. Technical Reference. Tandy Corp., USA, рр. 1-259.

Патент США (4400801, кл. G 11 С 7/00, 1983. (54) УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ДВУХ

ПРОЦЕССОРОВ ЧЕРЕЗ ОБЩУЮ ПАМЯТЬ (57) Изобретение относится к области вычислительной-техники и предназначено для сопряжения процессоров через общую память в микропроцессорных системах. Реализация устройства требует незначительных аппаратурных затрат

„„SU 1287167 А I

1287167

Изобретение относится к вычислительной технике и может быть использовано для сопряжения процессора с видеоконтроллером в микро-3ВМ с большой информативностью отображаемой 5 информации.

Целью изобретения является упрощение устройства.

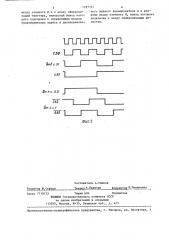

На AHl .1 приведена функциональная схема устройства и пример ее подклю- 10 чения к видеоконтроллеру; на фиг.2— временные диаграммы работы блока синхронизации.

Устройство (фиг.1) содержит блок

1 оперативной памяти, мультиплексор

2 адреса, регистр 3, блок 4 синхронизации, триггер 5, элемент И 6, двунаправленный шинный формирователь 7.

Видеоконтроллер 8 подключается к устройству через входы 9 и 10 данных и адреса и вход 11 запроса синхронного, доступа от второго процессора. Процессор подключается к устройству через вход-выход 12 данных, вход 13 адреса и вход 14 запроса асинхронного

25 доступа от первого процессора. В ка- честве второго процессора может быть использован видеоконтроллер .КР 580ВГ75.

Под доступом к памяти подразуме:вается как цикл чтения, так и цикл записи в память.

Устройство работает следующим образом. 35

Видеоконтроллер 8 выдает адрес на мультиплексор 2. Мультиплексор 2 подает на блок 1 либо адрес процессора, либо адрес видеоконтроллера. Переключение источника адреса производится 40 триггером 5 на который поступает сигнал асинхронного запроса доступа процессора. Блок 4 обеспечивает формирование сигналов управления блока

1 с удвоенной частотой. В отсутствие сигнала доступа от процессора адрес от видеоконтроллера 8 поступает в блок 1, откуда происходит выборка информации для видеоконтроллера 8 и ее запоминание в регистре 3. Видеоконт- 50 роллер 8 принимает данные с частотой отображения на экране индикатора.

При поступлении сигнала асинхронного доступа от процессора мультиплексор

2 производит подачу адреса с входа

13 адреса на блок 1, блокируя посредством элемента И 6 запись выбранной из блока 1 информации в регистр 3.

При этом происходит переключение двунаправленного шинного формирователя

7 и выбранная из блока 1 информация поступает на вход-выход 12 данных процессора. Тем самым на один такт чтения информации из блока 1 оперативной памяти видеоконтроллером 8 приходится два такта .обращения к блоку 1, а в случае отсутствия доступа к видеопамяти от процессора происходит двойная (дублирующая) запись информации в регистр 3. Когда же в один из этих двух тактов происходит обращение процессора в блок 1, блокировка записи в регистр 3 позволяет сохранять правильную информацию для выборки видеоконтроллера 8, Таким образом, безконфликтный обмен через память организуется при помощи незначительных аппаратных затрат.

Формула и з о брет ения

Устройство для сопряжения двух процессоров через общую память, содержащее блок оперативной памяти, мультиплексор адреса, регистр, элемент И, блок синхронизации и триггер, информационный вход которого является входом запроса асинхронного доступа от первого процессора устройства, первый и второй информационные входы мультиплексора адреса являются входами адреса от первого и второго процессоров устройства соответственно, выход мультиплексора подключен к входу адреса блока оперативной памяти, выход которого подключен к информационному входу регистра, выход которого является выходом данных на второй процессор устройства, тактовый вход блока синхронизации является входом запроса синхронного доступа от второго процессора устройства, о т— л и ч а ю щ е е с я тем, что, с целью упрощения устройства, в него введен двунаправленный шинный формирователь, первый информационный вход-выход которого является входом-выходом данных от первого процессора устройства, второй информационный вход-выход двунаправленного шинного формирователя соединен с выходом и информационным входом блока оперативной памяти, вход управления записью-считыванием которого подключен к первому выходу блока синхронизации, второй выход которого подключен к первому

- 1287167

g52

OmOK 56

Фиг. 2

Составитель А.Ушаков

Техред А КРавчУк Корректор JI Пилипенко

Тираж 694 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Редактор Ю.Середа

Заказ 7719/53

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 входу элемента И и к входу сйнхронизации триггера, инверсный выход которого подключен к управляющим входам мультиплексора адреса и двунаправленС48

om tKf

gA8 ного шинного формирователя и к второму входу элемента И, выход которого подключен к входу синхронизации регистра.