Интегратор

Иллюстрации

Показать всеРеферат

Изобретение предназначено для выполнения математической операции . , интегрирования разности двзпс аналоговьк напряжений. Целью изобретения является повьшение точности интегриро . г вания и расширение функциональных возможностей за счет обеспечения управления вехшчиной зоны нечувствительности . Интегратор содержит дифференциальный операционный усилитель 1, управляемый источник тока, образованный источниками 9 и 10 напряжения и преобразователями 7 и 8 напряжения в ток, и блок интегрирования, образованный накопительным конденсатором 11 и повторителем 12 напряжения. Интегратор позволяет обеспечить равенство коэффициента интегрирования для различных полярностей входного напряжения за счет использования для компенсации зоны нечувствительности двухпо- Q лярного управляемого источника тока, что также позволяет, изменяя только величину резистора, включенного между базами и эмиттерами первого и второго транзисторов, изменять величину зоны нечувствительности интегратора как в сторону увеличения, так и в сторону уменьшения, ато, в свою очередь, приводит к повышению точности интегрирования и расширению функциональных возможностей интегратора. 1 ил. (Л с:

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (51) 4 С 06 С 7/18.

ОПИСАНИЕ ИЗОБРЕТЕНИЯ:

Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ вания и расширение функциональных возможностей за счет обеспечения управления величиной зоны нечувствительности. Интегратор содержит дифференциальный операционный усилитель 1, управляемый источник тока, образованный источниками 9 и 10 напряжения и преобразователями 7 и 8 напряжения в ток, и блок интегрирования, образованный накопительным конденсатором 11 и повторителем 12 напряжения. Интегратор позволяет обеспечить равенство коэффициента интегрирования для различных полярностей входного напряжения за счет использования для компенсации зоны нечувствительности двухпо- < лярного управляемого источника тоха,. что также позволяет, изменяя только величину резистора, включенного между базами и эмиттерами первого и второго .транзисторов, йзменять величину зоны нечувствительности интегратора как Я в сторону увеличения, так и в сторону уменьшения, это, в свою очередь, приводит к повышению точности интегрирования и расширению функциональных возможностей интегратора. 1 ил.

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3955180/24-24 (22) 17.09.85 (46) 30.01 ° 87. Бюл. Р 4 (71) Московский авиационный институт им. Серго Орджоникидзе (72) Е.Н.Кисин, В.И.Михайлов, В.Л.Похваленский и П.Е.Швецов (53) 681 335(088.8) (56) Гутников В.С. Интегральная электроника в измерительных устройствах.

Л.: Энергия, 1980, с. 133 °

Авторское свидетельство СССР

У 623216, кл. С Об G 7/18, 1977.

Калмыков И.В. и др. Транзисторный интегратор для адаптивных систем управления. Сборник: Проблемы авиационной и космической кибернетики./

Под ред. Б.Н.Петрова. Информационные материалы 6 (53), изд. АН СССР, 1972, с. 133, рис. 2. (54) ИНТЕ ГРАТОР (51) Изобретение предназначено для выполнения математической операции . интегрирования разности двух аналоговых напряжений. Целью изобретения является повышение точности интегриро1 я.Я0 1287195 А 1

87195.2

1О

1 12

Изобретение-,относится к автоматике и вычислительной технике.

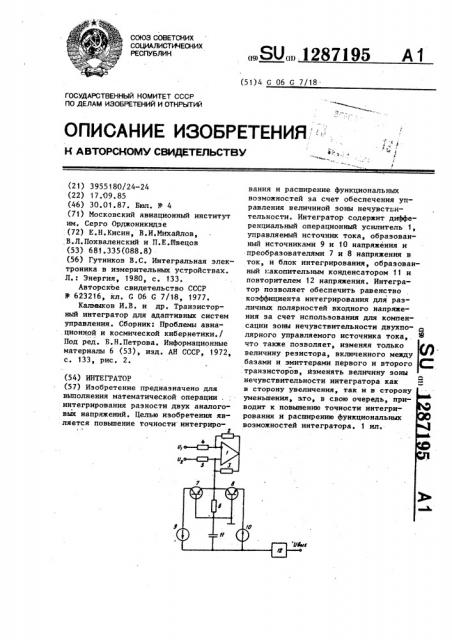

Цель изобретения — повышение точности интегрирования и расширение функциональных возможностей -путем обеспечения управления величиной зоны нечувствительности. . На чертеже приведена функциональ,ная схема предлагаемого интегратора.

Интегратор содержит дифференциальный операционный усилитель 1, масштабные резисторы 2-6, преобразователи напряжения в ток, выполненные на биполярных транзисторах 7 и 8, источники 9 и 10 постоянного напряжения, накопительный конденсатор 11 повторитель 12 напряжения.

Выход дифференциального операционного усилителя 1 через масштабные резисторы 2 и 3 соединен соответственно с инвертирующим и неинвертирующим входами усилителя 1. Инвертирующий вход усилителя 1 через масштабНый резистор 4 соединен с первым информационным входом интегратора, неинвертирующий вход усилителя 1 через масштабный резистор 5 соединен с вторым информационным входом интегратора, а через масштабный резистор 6— с шиной нулевого потенциала.

Змиттеры транзисторов 7 и 8 соединены с неинвертирующим входом дифференциального операционного усилителя, базы — с шиной нулевого потенциала, а коллекторы соединены с первыми выводами источников 9 и 10, вторые выводы которых подключены к од.ному из выввдов накопительного конденсатора 11 и входу повторителя 12 напряжения. Второй вывод накопительного конденсатора 11 соединен с шиной нулевого потенциала.

Интегратор работает следукштим образом.

Входные сигналы через резисторы 4 ,и 5 поступают на инвертирующий и неинвертирующий .входы усилителя 1, охваченного через резисторы 2 и 3 соответственно отрицательной и положительной обратными связями. В этом случае между неинвертирующим входом усилителя 1 и шиной нулевого потенциала через база-эмиттернйй переход транзистора 7 (или 8) и резистор 6 протекает ток, величина и наттравление которого определяются величиной и знаком разности входных напряжений.

Ток, протекающий по база-эмиттерной цепи транзистора 7 (или 8), вызывает соответствующий ток в коллекторной цепи транзисторов, который заряжает накопительный конденсатор 11 до напряжения соответствующей полярности, величина которого ограничена напряжением источников 9 и 10. Напряжение с конденсатора 11 через повторитель

12 напряжения поступает на выход интегратора. !

Повьппение точности интегрирования достигнуто путем введения усилителя

1 и резисторов 2-6, соответствующим выбором которых достигается заданная величина зоны нечувствительности интегратора и равенство коэффициентов интегрирования для положительных и отрицательных входных сигналов.

Формула изобретенЪтя

Интегратор, содержащий накопительный конденсатор, повторитель напряжения, выход которого является выходом интегратора, первый и второй преобразователи напряжения в ток, выполненные на первом и втором биполярных транзисторах, базы которых соединены с первым выводом накопительного конденсатора и подключены к шине нулевого потенциала, два последовательЗ5 но соединенных источника постоянного напряжения, общий вывод которых под, ключен к второму выводу накопительного конденсатора и входу повторителя напряжения, а другие выводы соединены с коллекторами соответственно первого и второго биполярных транзисторов, отличающийся тем, что, с целью повьппения точности интегрирования и расширения функциональных возможностей эа счет обеспечения управления величиной зоны нечувствительности, в него введены дифференциальный операционный усилитель и пять мас— штабных резисторов, причем первые вы50 воды первого и второго масштабных резисторов являются соответственно первым и вторым информационными входами интегратора, вторые их выводы подключены соответственно к инвертирующему

55 и неинвертируюцему входам дифференциального операционного усилителя, и соответственно через третйй и четвертый масштабные резисторы к его выхоСоставитель С.Белан

Техред И.Попович

Корректор. М.Демчик

Редактор С.Лисина

Заказ 7720/54

Тираж 670

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Подписное

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

3 1287195 4 ду, эмиттеры первого и второго бипо- операционного усилителя и через пятый лярных транзисторов соединены с неин- масштабный резистор — с шиной нулевовертирующим входом дифференциального ro потенциала.