Одноразрядный компаратор на мдп транзисторах

Иллюстрации

Показать всеРеферат

Изобретение относится к импульсной технике. Может быть использовано при разработке универсальных ЦВМ. Целью изобретения является повьшение надежности за счет упрощения. Введены 1/овые функциональные связи, что позволило достичь поставленную цель. Эффективность устройства по сравнению с прототипом заключается в том, что он содержит на два транзистора меньше. Кроме того, предлагаемое устройство развязывает электрически входные и выходные сигналы, т.е. не использует двунаправленных ключевых элементов, что повышает нагрузочную способность. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„.80„„1287367 А 1 дц 4 Н 03 K 5/24

ОПИСАНИЕ ИЗОБРЕТЕНИЯ,

1 ) с

К ASTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3880126/24-21 (22) 01. 04. 85 (46) 30.01.87.. Бюл. Ф 4 (72) С.В.Быков, Л.Н.Корягин и О.И.Гусакова (53) 621.374.33 (088.,8) (56) Титце У. и др. Полупроводниковая схемотехника. М.: Мир, 1982, с. 330, рис. 19 ° 23 ° (54) ОДНОРАЗРЯДНЫЙ КОМПАРАТОР НА МДП ТРАНЗИСТОРАХ (57) Изобретение относится к импуль, сной технике. Может быть использовано при разработке универсальных ЦВМ.

Целью изобретения является повьппение надежности за счет упрощения. Введены новые функциональные связи, что позволило достичь поставленную цель.

Эффективность устройства по сравнению с прототипом заключается в том, что он содержит на два транзистора меньше. Кроме того, предлагаемое устройство развязывает электрически входные и выходные сигналы, т.е. не использует двунаправленных ключевых элементов, что повышает нагрузочную способность. 1 ил.

128/267

Изобретение относится к импульсной технике и может быть использовано при разработке универсальных

ЦВИ.

Целью изобретения является повышение надежности.эа счет упрощения.

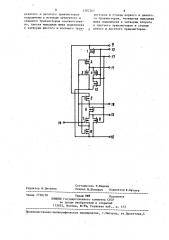

На чертеже представлена принципиальная схема заявленного устройОдноразрядный компаратор на NJJIIтранзисторах содержит последовательную цепочку первого и второго транзисторов 1, 2 первого типа, к стоку второго транзистора подключены стоки 1I5 третьего и четвертого транзисторов 3, 4 второго типа соответственно, пятый, шестой транзисторы 5, 6 первого типа соединены последовательно, сток шестого транзистора 6 подключен к сто- 20 кам седьмого, восьмого транзисторов

7, 8 второго типа, истоки первого, пятого транзисторов 1, 5 подключены к первой шине 9 питания, истоки третьего, восьмого транзисторов 3, 8 подключены к второй шине 10 питания, стоки второго и шестого транзисторов 2, 6 подключены к первой и второй выходным шинам 11, 12 соответственно, затворы первого, четверто- ÇÎ о транзисторов 1, 4 подключены к псрвой входной шине 13, затворы пятого, сецьмого транзисторов 5, 7 подключены к второй выходной шине 14, затворы второго, третьего и шестого, 35 восьмого транзисторов 2, 3, 6, 8 по- парно соединены, истоки девятого 15, десятого 16 транзисторов второго типа подключены к второй шине 10 питания, затворы девятого и десятого 0 транзисторов 15, 16 подключены к первой и второй входным шинам 1", 14, а стоки девятого и десятого транзисторов 5, 16 подключены к истокам четвертого и седьмого транзисторов

4, 7 соответственно, третья .выходная шина 17 подключена к затворам шестого, восьмого транзисторов 6, 8, истокам первого, девятого транзисторов

1, 15, четвертая выходная шина 18 подключена к затворам второго, третьего транзисторов 2, 3 и стокам пятого, десятого транзисторов 5, 16.

Устройство работает следующим образом. 55

На шины 9, t0 подключаются "плюс" и,минус источников питания соответственно. Потенциалы плюса" и минуса источника питания принимаются соответственно эа "1" и "0".

Входные сигналы подаются на шины 13 и 14. -На транзисторах 1, 15 и 5, 16 образованы инверторы для этих сигналов а выходными шинами 17, 18. Одновременно транзисторы 1 и 5 являются транзисторами, входящими в схемы элементов ИЛИ-НЕ с выходными шинами 11, 12. Транзисторы 4, 7 предназначены для развязки соответствующих инверторов и элементов ИЛИ-НЕ. Если принять сигналы, приходящие соответственно на шины 13 и 14, в логическом обозначении эа сигнал А и Б, то на шинах 11 и 12 будут выполняться функции А.В н А Б.

Предлагаемое устройство содержит два транзистора меньше„ чем известное. Кроме того, предлагаемое устройство развязывает электрически входные и выходные сигналы, т.е. не использует двунаправленных ключевых элементов, что повышает нагрузочную способность.

Ф о р м у л а и з о б р е т е н и я

Одноразрядным компаратор на ЩП транзисторах, содержащий последова = тельную цепочку первого и второго транзисторов первого типа, к стоку второго транзистора подключены стоки третьего и четвертого транзисторов второго типа, пятый, шестой транзисторы первого типа соединены последовательно, сток шестого транзистора подключен к стокам седьмого, восьмого транзисторов второго типа, истоки третьего и восьмого транзисторов подключены к второй шине питания, стоки второго и шестого транзисторов подключены к первой и второй выходным шинам соответственно, затворы первого и четвертого тран— зисторов подключены к первой входной шине, затворы пятого и седьмого транзисторов подключены к второй входной шине, затворы второго, третьего, шестого и восьмого транзисторов попарно соединены, истоки девятого и десятого транзисторов второго типа подключены к второй шине питания, затворы девятого и десятого транзисторов подключены к первой и второй входным шинам соответственно, о т л и ч а ю шийся тем, что, с целью повышения надежности, стоки

1287267

Составитель Н.Маркин

Техред И.Попович Корректор В.Бутяга

Редактор М.Циткина

Заказ 7728/58

Тираж 893 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35; Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r.Óõãîðîä, ул.Проектная,4 девятого и десятого транзисторов подключены к истокам четвертого и седьмого транзисторов соответственно, третья выходная шина подключена к затворам шестого и восьмого транэисторов и стокам первого и девятого транзисторов, четвертая выходная шина подключена к затворам второго и третьего транзисторов и стокам пятого и десятого транзисторов.

У

1З