Преобразователь перемещения в код

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике, может быть использовано в цифровых позиционных регуляторах, информационных системах, системах управления положением механизмов. Целью изобретения является повьппение достоверности передаваемой информации преобразователем . Для этого в-преобразователь перемещения в код, содержащий кодирующий элемент 1, чувствительные элементы 2, преобразователь 3 кода, регистр 4 и элемент ИЛИ-НЕ 7, введены блок 5 контроля кода, формирователь 6 управляющих импульсов, D-триггер 8 и элемент ИЛИ 9. Поставленная цель достигается за счет того , что вместе с кодом, передаваемым потребителю, формируются сигналы Готовность и Запрет, которые запрещают считывание кода с выходов преобразователя при наличии ошибки кодирования и преобразования, а также на время переходных процессов в цепях преобразователя и линиях связи. I з.п. ф-лы, 4 ил. (/)

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (19) (И) (б)) 4 Н 03 М 1/26

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

H А ВТОРИЧНОМ,Ф СВИДЕТЕЛьСтВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3941992/24-24 (22) 24.06.85 (46) 30.01.87. Бюл. ¹ 4 (71) Киевский институт автоматики им. XXV съезда КПСС (72) А.В. Мельников, А.В. Зарин, В.А. Ипатов, Ю.С. Голуб и Г.В. Салов (53) 681.325(088.8) (54) ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕЩЕНИЯ В

КОД (57) Изобретение относится к автома— тике и вычислительной технике, может быть использовано в цифровых позиционных регуляторах, информационных системах, системах управления положением механизмов. Целью изобретения является IIQBbBIIpHHe достоверности передаваемой информации преобраэователем. Для этого в .преобразователь перемещения в код, содержащий кодирующий элемент 1, чувствительные элементы 2, преобразователь 3 кода, регистр 4 и элемент ИЛИ вЂ 7, введены блок 5 контроля кода, формирователь 6 управляющих импульсов, D òðèããåð 8 и элемент ИЛИ 9. Поставленная цель достигается эа счет того, что вместе с кодом, передаваемым потребителю, формируются сигналы "Готовность" и "Запрет, которые запрещают считывание кода с выходов преобразователя при наличии ошибки кодирования и преобразования. а также на время переходных процессов в цепях преобразователя и линиях связи. 1 з.п. ф-лы, 4 ил.

1?87287

Изобретение относится к автоматике и вычислительной технике и может быть использовано в цифровых позиционных регуляторах, информационных системах, системах управления поло- 5 жением механизмов.

Цель изобретения — повышение достоверности передаваемой информации преобразователем.

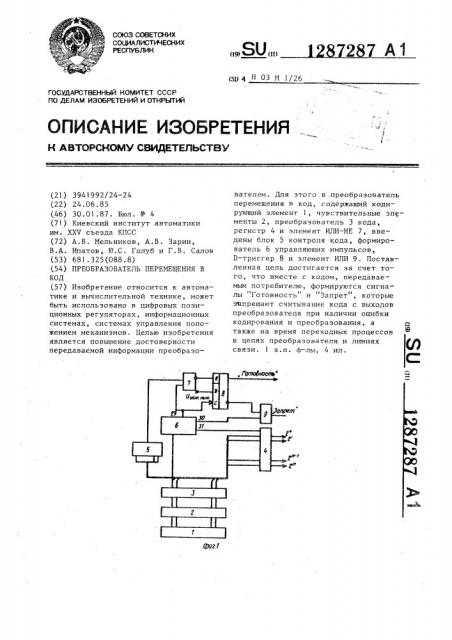

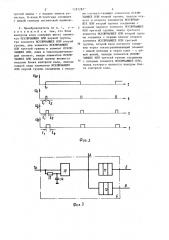

На фиг. 1 изображена схема преобразователя перемещения в параллель— ный код; на фиг. 2 — диаграмма работы формирователя импульсов; на фиг.3 схема формирователя управляющих импульсов; на фиг. 4 — пример выполнения блока контроля кода для. двенадцати разрядов.

Преобразователь перемещения в код содержит кодирующий элемент 1, блок 2 чувствительных элементов, преобразователь 3 кода, регистр 4, блок 5 контроля кода, формирователь

6 управляющих импульсов, элемент

ИЛИ-HE 7, D — триггер 8, элемент ИЛИ 9, Формирователь 6 управляющих им-! пульсов содержит элемент ИСКЛЮЧАЮЩЕЕ

ИЛИ 10, ждущие мультивибраторы 11 и

12, резистор 13, конденсатор 14.

Блок 5 контроля кода содержит элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 15-26, токоограничивающий элемент на резисторе 27 и ключ 28. Формирователь 6 управляющих импульсов имеет выходы

29-31.

Преобразователь работает следующим образом.

Перемещение кодирующего элемента

1 вызывает срабатывание чувствительных элементов блока 2, которые считывают информацию и передают ее на вхо40 ды преобразователя 3 кода. Изменение уровня сигнала на выходе первого разряда чувствительных элементов блока

2 влечет начало процесса коммутации элементов преобразователя 3 кода в соответствии с выбранным методом пре.образования "двойная щетка" или Vсчитывания и формирования кода перемещения на его выходах, соответственно на входах регистра 4 и блока

5 контроля кода. Изменение кода на выходе преобразователя 3 кода вызывает срабатывание элементов блока 5 контроля кода.

Изменение уровня сигнала первого разряда на выходе преобразователя 3 .кода вызывает появление трех импульсов (фиг. 2) разной длительности (;t t,) н» выходах 29 — 31 формирователя 6 управляющих импульс<,ов, причем tò t. t1 С вЂ” t1 .

В исходном состоянии на выходах

29 — 31 формирователя 6 управляющих импульсов имеется низкий уровень сигнала, на выходе блока 5 контроля кода — высокий уровень cêãíÿëà, на выходе элемента ИЛИ-НЕ 7 — низкий уровень сигнала, на выходе Готовность преобразователя — высокий уровень сигнала, соответствующий достоверной информации на выходах регистра 4, на первом и втором входах элементов ИЛИ 9 и на выходе "Запрет" преобразователя установлены низкие уровни сигналов.

Если в интервалах между появлением импульсов на выходе 29 формирователя 6 управляющих импульсов на выходе блока 5 контроля кода по какой-либо причине изменился уровень сигнала на низкий, то на выходе элемента ИЛИ-НЕ 7, соответственно и на R-входе D-триггера 8, устанавливается высокий уровень сигнала, в результате на выходе "Готовность" преобразователя устанавливается низкий уровень сигнала, соответствующий неготовности к работе преобразователя ввиду появления бшибки считывания. Одновременно на втором входе элемента ИЛИ 9 и на выходе "Запрет" преобразователя устанавливаются высокие уровни сигналов. Высокий уровень сигнала на выходе "Запретя преобразователя в этом случае запрещает считывание информации с выходов регистра 4 из-за недостоверности кода на выходе регистра 4, что определяется низким уровнем сигнала на выходе Готовность" преобразователя.

Изменение кода на выходе преобразователя 3 кода сопровождается переходными процессами в элементах преобразователя 3 кода и блока 5 контроля кода, причем при V-считывании этот процесс более продолжительный. Чтобы исключить запись сигнала с выхода блока 5 контроля кода в D-триггер 8 на время переходных процессов при смене кода, введен элемент ИЛИ-НЕ 7.

Импульс с выхода 29 формирователя

6 устанавливает на выходе элемента

ИЛИ-НЕ 7 низкий уровень сигнала независимо от уровня сигнала на втором

1287287 входе ИЛИ-НЕ 7. Таким образом, длительность сигнала и -, с выхода 29 формирователя 6 импульсов должна быть не менее времени протекания переходных процессов в элементах преобразователя 3 кода и блока 5 контроля.

Импульс с выхода 29 формирователя, 6 импульсов своим передним фронтом подтверждает или устанавливает на выходе "Готовность" преобразователя l0 высокий уровень сигнала, если на

R âõîäå D òðèããåðà 8 низкий уровень сигнала. Если на выходе блока 5 контроля кода имеется низкий уровень сигнала, соответственно на R âõîäå

D-Tðêããåðà 8 высокий уровень сигнала, то,установка высокого уровня сигнала на выходе Готовность" преобразователя не происходит по переднему фронту импульса с выхода 29 формиро- 20 вателя 6 импульсов, ввиду приоритетности R âõîäà D òðèããåðà 8 по отношению к остальным его входам. Низкий уровень сигнала на к-входе Р-триггера 8, устанавливаемый импульсом с выхода 29 формирователя 6 на время переходных процессов в преобразователе 3 кода и блока 5 контроля кода через элемент ИЛИ вЂ 7, задерживает— ся элементом ИЛИ-НЕ 7 на время пере- 30 ходных процессов в самом элементе

ИЛИ вЂ 7. Таким образом, передний фронт этого импульса поступает на

С-вход Р-триггера 8 несколько раньше изменения уровня сигнала на R âõîäå 35

D òðèããåðà 8 и в результате исключается возможность промигивания сигнала низкого уровня на выходе

"Готовность" преобразователя.

Импульс с выхода 30 формировате- 40 ля 6 в момент времени t (фиг. 2) осуществляет запись в регистр 4 кода, установившегося на его входах.

Длительность t -t этого импульса выбирается с учетом переходных про- 4g цессов в линиях связи и времени реакции системы потребителя информации, но не менее

Импульс с выхода 31 формирователя

6 импульсов поступает на первый вход элемента ИЛИ 9, на выходе которого формируется сигнал Запрет", запрещающий считывание кода с выходов регистра 4 на время t< -,. Длительность импульса выбирается из условия, что интервал времени t<-t> не меньше времени переходных процессов в линии связи, по которой передается код с выходов регистра 4, Ьлок 5 контроля када работает сле-дующим а бра э ом .

Если общее число разрядов кода перемещения и дополнительного разряда, на которых установился вь1сокий уровень сигнала, четное, то на выходе блока 5 контроля кода устанавливается высокий уровень сигнала.

Контроль на нечетность возможен при соответствующем кодировании дополнительного разряда Доп.р. с одновременным подключением к источнику низкого уровня сигнала (Общий Оп) . В этом случае при наличии достоверного кода íà его выходе устанавливается высокий уровень сигнала.

В результате нарушения функционирования преобразователя по любому из разрядов, включая-контрольный, на выходе блока 5 контроля кода устанавливается низкий уровень сигнала, соответствующий недостоверному коду на входах блока 5 контроля кода и регистра 4.

Формула и з о б р е т е н и я

l. Преобразователь перемещения в код, содержащий последовательно соединенные кодирующий элемент, блок чувствительных элементов и преобразователь кода, выходы которого соединены с входами регистра, выходы которого являются выходами преобразователя, элемент ИЛИ вЂ , о т л и ч а ю шийся тем, что, с целью повышения функциональной надежности преобразователя эа счет повышения достоверности выходного кода, в него введены блок контроля кода, формирователь управляющих импульсов, D òðèããåð и элемент ИЛИ, выходы преобразователя кода соединены с входами блока контроля кода, выход которого соединен с первым входом элемента ИЛИ-НЕ, выход которого соединен с R-входом D-триггера, первый выход которого является выходом "Готовность" преобразователя, второй выход соединен с первым входом,элемента ИЛИ, выход которого является выходом "Запрет преобразователя, выход младшего разряда преобразователя кода соединен с входом формирователя управляющих им— пульсов, первый выход которого соединен с вторым входом элемента ИЛИНЕ и С-входом D-триггера, второй выход — с вторым входам элемента ИЛ11, 1287287 третий выход — с входом записи регистра, D-вход D-триггера соединен с шиной сигнала логической единицы.

2. Преобразователь по п. 1, о т- 5 л и ч а ю шийся тем, что блок контроля кода содержит шесть элементов ИСКЛЮЧАЮЩЕЕ ИЛИ первой группы, три элемента ИСКЛЮЧАЮЩЕЕ ИЛИ второй группы, два элемента ИСКЛЮЧАЮЩЕЕ

ИЛИ третьей группы и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, ключ и токоограничивающий элемент, входы элементов ИСКЛЮ—

ЧАЮЩЕЕ ИЛИ первой группы являются входами блока контроля кода, выходы

15 каждой пары элементов ИСКЛЮЧАЮЩЕЕ

ИЛИ первой группы соединены с входами соответствующих элементов ИСКЛЮЧАЮЩЕЕ ИЛИ второй группы, выходы первого и второго элементов ИСКЛЮЧАЮЩЕЕ ИЛИ второй группы соединены с входами первого элемента ИСКЛЮЧАЮЩЕЕ

ИЛИ третьей группы; выход третьего элемента ИСКЛЮЧАК61ЕЕ ИЛИ второй группы соединен с первым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ третьей группы, второй вход которого соединен через токоограничивающий элемент с шиной питания и через ключ — с общей шиной, выходы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ третьей группы соединены с входами элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого является выходом блока контроля кода.

l287287

+ Qun.

Составитель Е. Бударина

Редактор E. Копча Текред Л.Сердюкова КорректорС. Иекмар

Заказ 7730/59 Тираж 899 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

ll3035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4