Устройство для воспроизведения зависимостей вида @

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (И) (д)) 4 G 06 F 7/50 15/30

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

5.1

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3846811/24-24 (22) 14.01.85 (46) 07.02.87. Бюл. В 5 (7 1) Институт проблем моделирования в энергетике АН УССР и Киевский институт инженеров гражданской авиации (72) А.И.Стасюк, Ф.Е.Лисник, Ю.П.Подковко и А.И.Гузенко (53) 681.325(088.8) (56) Авторское свидетельство СССР

У 717759, кл. G 06 F 7/38, 1978.

Авторское свидетельство СССР

)) 717765, кл. С 06 F 7/50, 1978. (54) УСТРОЙСТВО ДЛЯ ВОСПРОИЗВЕДЕНИЯ

ЗАВИСИМОСТЕЙ ВИДАZ:С; Z;Х; (57) Изобретение относится к вычислительной технике и может быть использовано для выполнения операций видаЕС;Е,Х; при оперативном выполнении групповых операций. Цель изобретения - повышение быстродействия.

Поставленная цель достигается тем, что устройство содержит с первого по третий вычислительные блоки 1.1-1.3 первой группы, первый и второй вычислительные блоки 2.1 и 2.2 второй группы, сумматор 3, с первого по третий входы 4.1-4,3 значения первой переменной устройства, с первого по третий входы 5.1-5.3 значения второй переменной устройства, с первого по третий входы 6.1-6.3 значения третьей переменной устройства, первый и второй входы 7.1 .и 7.2 вспомогательных значений устройства, выход 8 результата устройства, сумматоры по модулю два первой группы, сумматоры по модулю два второй группы. Повъппение быстродействия устройства обеспечивается благодаря параллельной структуре устройства, искомое решение получается за один такт, длительность которого равна задержке сигнала между входом и выходом устройства. 2 ил.

1288692

Х("

» j

35 ственно ((! = 2,32 г»

-3I-I -Ь Р и

2,= 2 СОХ,;

-5

2 СОХ

Ф (1)

Ю где С =

45 -0 ; I) <

+ 2 СЕХ;ь

50 где С®Z;= — матрицы бинарных элементов, составленные

О и

СО Х;= из разрядных векторов вида

» (, )

° .Z

» a ч

Изобретение относится к вычислительной технике и может быть использовано для выполнения операций вида

2С Е Х при оперативном выполнении

i 1 1

1 групповых операций.

Целью изобретения является, увеличение быстродействия.

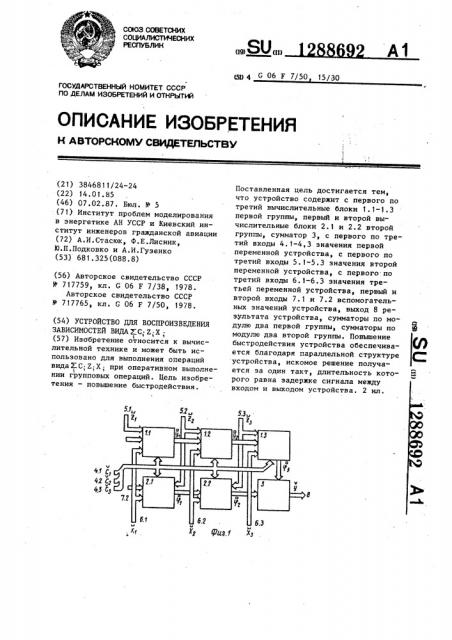

На фиг.1 приведена блок-схема устройства для случая, когда ш = 3, и =

= 3; на фиг.2 — схема вычислительного блока.

Устройство содержит первый 1,1, второй 1.2 и третий 1.3 вычислительные блоки первой группы, первый 2.1 и второй 2.2 вычислительные блоки второй группы, сумматор 3, первый

4.1, второй 4.2 и третий 4.3 входы устройства значения первой переменной, первый 5.1, второй 5.2 и третий

S.3 входы устройства значения второй переменной, первый 6.1, второй 6.2 и третий 6.3 входы устройства значения третьей переменной, первый 7.1 и второй 7.2 входы вспомогательных значений устройства, выход 8 результата устройства, сумматоры 9 по модулю два первой группы и сумматоры 10 по модулю два.второй Fp)iïïûа

Устройство для моделирования за-. висимости вида

Y =ЕС;Е;Х;

3 работает следующим образом.

Иоделируемая зависимость в разрядной форме представлена как (, ) и т» и

l i (=! представляющих собой разрядное иэоб10 ражение чисел соответственно;

V у — разрядный вектор вида у =

L1 1 1 И 1»1 1+!

Х;=,(Х,, Х,,..., Х„); Z,. (Z,, Z„, „) — векторы бинарных элементов, составленные из i компонентов ч

m-разрядных векторов Х,,...,Х и

Z, Z соответственно. и

-(i»i) Q O(,(Ll

Выражение 2 С Z Х; вычисляет1»! ся по разрядным рекуррентным зависимостям

25 и «1,-Яь -г О

=g, U u

30 + 2 С® .ь

1» ° ° ° »и»

II-1 а выражение, « 2 (" )(,()с 1((+ 1 соответ1=!

Операции, представляющие собой вазрядное изображение покомпонентно1288692 4

С =(С,,С2,..., решение у = 0,2351074. Значения Z

Х ), реали- и Х (! = 1,2,3) в разрядной форме имеют вид

ro умножения векторов с„) ; х;=(х,, Х,, ..., зуется как СХ; =(С,Х,, С„Х„) .

Конечный результат формируется как

125;

X< = и !5

Вычислительный процесс значений у.

2 о, = 2 СО» Z, =(0,140625; 0; О) и 1

1 э У = 2 g,О»Х, =(0,0,0) 2 = 2 са, + 2 СО» Zg=(0,0703125; 0,0234375; 0,019532) i=2 у, + 2 ос О» Х =(0,0703125; О; О)

3, 2 ос =2 ос + 2 CO Z =(0,0351526; 0,017578; 0,009766) У2

Уэ У2+ 2 осэO Xç= (О 0703125; О О) ф LI 1

2 м = 2 + 2 СЕ К, =(0,0175781; 0,0102538; 0,0061037), у = у»+ 2 ® X =(0,0878906; 0,0102538; 0,0061037) Вычислительный процесс значений Ч вЂ” 1, Су, = 2 Р O» Z, =(О; 0,046875; 0,0390625) 2 /3 = 2 СО» Х,=(О; 0,046875; 0,0390625) i = 2, 2 P» = 2 f5, + 2 СО» X2=(0»0175781; 0»02334375; 0»0105312) э

CP = Ч + 2 Рэ® Z э (0 0703125 - 0 0390625) i = 3, 2 Pg = 2 P + 2 СО" X =(0,008789; 0,0117187; 0,0097656) 2; 0,048828 1) l в схеме устройства протекает переходной процесс. После окончания переходного процесса в схеме в сумматоре 9 блоков 1.1 и 2.1 образуются значения

° -2о Эо матриц 2 ы, и 2 г соответственно.

Каждый j-й столбец (j = 1,...,m) мат-г о -q D

Рицы 2 М, и 2 В подается на второй вход j-го сумматора 10 соответственно блоков 1.1 и 2.1 и со сдвигом 2 на первый вход j ãî сумматора 9 блоков 1.2 и 2.2. В это же время на выходе каждого S-го (S = m + 1,...,2m) сумматора 9 блоков 1.1 и 2.1 образуются значения (m — S) = Х столбцов

v 0 u

y = у„х +q х, где Х =(1,1;...,1)

Рассмотрим пример для и = 4 и

m-- 3.

С,= 0,5625; С = 0,375; Сэ=о,з

Е,= 0,5; 2 = 0,4375; Е = 0,3125;

= 0,3125; Х = 0,5625; Х = 0,5625 (— — чг + 2 p Î Z =(О; 0,082031

Конечный результат определяет- . ся как у = Y„.Х + q,x = 0,0878906, +

+ 0,0102538 + 0,0061037 + 0,0820312 +

+ 0,0488281 = 0,2351074, где Х = (I 1, 1)

Устройство работает следующим образом.

После подачи на входы 4.1-4.3 соот-55 ветственно С, С2» Сэ, т.е. С. На входы 5.1, 5.2 и 5.3 — значений Z!, 72, Zэ соответственно, на входы 6.1, и и и

6.2, 6.3 — Х,, Х2, Х соответственно э

Z, = (1000); Z

Х, =(0101); Х,=(! и далее Z =(1,0,0)

1) х (1 00) 3 (1 1 1) 1 С (с

=(0111); Z,=(0101) » Ф

0O1); x,= (1OO1) Z, =(0,1,1) 0,1,1); x,=(o,1, х,=(О,О,О) ; x,=

1,c„c3) 1288б92 матриц у, и q, которые подаются на первые входы S-х сумматоров 10 блоков 1.2 и 2.2. Далее на выходе каждого j-ro сумматора 9 блоков 1.2 и 2.2 образуются значения j-x столбцов мат- 5

-з п -фО, риц 2 м 2 и 2 р,(, которые подаются на вторые входы (m + j)-х сумматоров

10 своих групп 1 и со сдвигом 2" на первые входы j-х сумматоров 9 блоков

1.3 и 2.3. На выходе каждого S-го сумматора 9 и 10 образуются значения (m — S)-х столбцов матриц у и q которые поступают на первые входы

S""х сумматоров 9 и 10 блоков 1.3 и

2,3. Аналогичным образом на выходах

j-x сумматоров 9 и 10 блоков 1.i u

2.i образуются значения j-х столбцов

-(111 > -(q+21A матриц 2 o(; и 2 ;„, которые поступают со сдвигом 2 на первые входы j-х сумматоров 9 и 10 блоков

1.i+1 и 2.i+1 и на вторые входы (n +

+ i)-х сумматоров 9 и 10 своих блоков

1. В это же время на выходах S-х сумматоров 9 и 10 блоков 1.i и 2 i абра- 25 зуются значения (m — S)-х столбцов ь и матриц у; и е2, которые подаются на первые входы S-х сумматоров 9 и 10 соответствующих групп. И, наконец, на выходах j-х сумматоров 9 и 10 блоков

1.m, 2.m-1 образуются значения j-x

-(и+11 D -(и-i1 О столбцов матриц 2 Я„ и 2 8, которые подаются на вторые входы (m+

+ i)-х сумматоров 9 и 10 своих блоков

1, на выходах которых образуются зна- 35 а О чения j x столбцов матриц q„, q „, которые поступают на входы сумматора

3, на выходе которого реализуется алгебраическая сумма столбцов матриц р П Щ ц и q>„,, благодаря чему на его выходе и соответственно на выходе 8 устройства образуется искомое решение.

Благодаря параллельной структуре устройства искомое решение получается

sa один такт, длительность которого равна задержке сигнала между входом и выходом устройства.

Например, в случае реализации устройства »а основе одной интегральной схемы 155 ИПЗ серии 155 совместно са схемой ускоренного переноса 155ИП4 при m = 10 и n = 16 время воспроизведения групповой операции равно

1,8 мкс.

Формула изобретения

Устройство для воспроизведения зависимостей вида С Е Х;, содержа1 щее сумматор, О т л и ч а ю щ е е с я тем, чта, с целью увеличения быстродействия, она содержит тп (ш- разрядность реализуемой величины) вычислительных блоков первой группы> (тп-1) вычислительных блоков второй группы, причем вход значения первой переменной устройства подключен к разрядам, начиная с 2>-га, первого информационного входа i-га вычислительнага блока (i =- 1,...,m) первой группы и к разрядам, начиная с (21+1) †, первого информационного входа j-га вычислительнога блока (j = 1,...,m-1) второй группы, первый вход значения второй переменной устройства подключен к второму информационному входу первого вычислительного блока первой группы, k-й вход (k = 2,...,;) значения второй переменной устройства подключен к вторым инфармациат|ньтм входам k-га вычн"лительн:".-o блока первой группы и (k — 1) †в.ьчислительНОГО 6JICKB ВТОРОЙ ГРУппгпq j Й т3хОД значения третьей переменной устройства подключен к третьим информациОнным входам Зт-х вычислительных блоков первой и второй групп, m-й вход значения третьей переменной устройства подключен к третьему информаци-" онному входу тп-го вычислительного блока первой группы, первый вход вспомогательных значений устройства подключен к четвертому информационному входу первого вычислитель ага блока первой группы, второй вход вспомогательных значений устройства подключен к четвертому информационному входу первого вычислительного блока второй группы, выход j-ro вычислительнага блока первой группы падкл.очен к разрядам, начиная с второго, четвертого информационного входа (j+1)-га вычислительнага блока первой группы, выход и-га (и= 1,...>ш-?) иычислительнага блока второй группы подключен к разрядам, начиная с второго, четвертого инфармационнага входа (и+1)-га вычислительного блока второй группы, выход тп-га вычислительного блока первой группы и выход

l тп-1)-га вычислительнага блока втc рай группы подключены соответственно к первому и второму информационным входам сумматора, выход которого подключен к выходу результата устройства, при этом вычислительный блок содержит первую группу нз ш сумматоров по модул|о два, вторую Iруппу тп

7 1288692 8 сумматоров по модулю два, -й разряд информационному входу 1-го сумматора первого информационного входа вычис-: по модулю два первой группы, f-й разлительного блока подключен к первому . ряд (Я = m+1, ° ..,2m) четвертого ининформационному входу i-го сумматора формационного входа вычислительного по модулю два первой группы, i-й раз- 5 блока подключен к первому информациряд второго информационного входа онному входу (8-m)-ro сумматора по вычислительного блока подключен к модулю два второй группы, выход i-ro тактовому входу i-ro сумматора по мо- сумматора по модулю два первой групдулю два первой. группы, i-й разряд пы подключен к второму информационнотретьего информационного входа вычис- 10 му входу i ãî сумматора по модулю лительного блока подключен к такто- два второй группы и к -му разряду вому вхоДУ i-ro сумматоРа по моДулю выхода вычислительного блока, выход два второй группы, i-й разряд четвер- i-го сумматора по модулю два второй того информационного входа вычисли- группы подключен к (i+m)-му разряду тельного блока подключен к второму 5 выхода вычислительного блока.

С С L

Z< Z>

А -1 1

Корректор В.Бутяга

Производственно-полиграфическое предприятие, г.ужгород, ул.Проектная, 4

V ii-1Я

v а-,1

Ус-fZ

v i-1 Л

Составитель В.Смирнов

Редактор О.Головач Техред В.Кадар

Заказ 7809/47 Тираж 694 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

6(у

Ус 1

V И

V С У