Устройство для вычисления корня третьей степени

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и предназначено для вычисления корня третьей степени в вычислительных машинах и устройствах с обработкой данных в формате с плавающей запятой. Целью изобретения является повышение быстродействия и расширение функциональных возможностей устройства за счет обработки данных в формате с плавающей запятой. Устройство содержит три триггера 1-3, семь регистров 3-6, 8-10, сумматор 7, четыре блока памяти 12-15, блок 16 сдвига и умножитель 17. На входы 20, 22, 18 подаются порядок, мантисса и знак мантиссы соответственно, на выходах 21,23,19 формируются значения I (Л г« .rs 00 о со ел

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (5ц 4 G 06 F 7/552

ОПИСАНИЕ ИЗОБРЕТЕНИЯ н двторСнсм свиДЕтельСтвм

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

flO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3923348/24-24 (22) 08.07.85 (46) 07.02.87.Бюл. Ф 5 (72) В.M.Крищишин (53) 681.325(088.8) (56) Авторское свидетельство СССР

Ф:903869, кл. С 06 F 7/552, 1980.

Белков М.С. и др. Разработка системы БИС для построения узлов ЦВМ.

Вопросы радиоэлектроники, Сер,ЭВТ, 1975, вып. 7, с. 79.

Уокерли Дж. Архитектура и программирование микро-3BN. — M.: Мир, книга I, с. 148.

Благовещенский Ю.В., Теслер Г.С, Вычисление элементарных функций на

3ВМ. 1977, Техника, с.105-106.

Авторское свидетельство СССР

Р 1084786, кл. С 06 F 7/552, 1980.

„„SU„„ A1 (54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ КОРНЯ

ТРЕТЬЕЙ СТЕПЕНИ (57) Изобретение относится к вычислительной технике и предназначено для вычисления корня третьей степени в вычислительных машинах и устройствах с обработкой данных в формате с плавающей запятой. Целью изобретения является повышение быстродействия и расширение функциональных возможностей устройства за счет обработки данных в формате с плавающей запятой.

Устройство содержит три триггера 1-3, семь регистров 3-6, 8-10, сумматор 7, четыре блока памяти 12-15, блок 16 сдвига и умножитель 17. На входы 20, 22, 18 подаются порядок, мантисса и знак мантиссы соответственно, на выходах 21,23,19 формируются значения

1288695 порядка мантиссы и знака мантиссы синхронизирующие сигналы, Устройство соответственно. На вход 24 поступают работает в конвейерном режиме. 1 ил. х,)э

4х, ° 2, если делится на 3 нацело, пэ

О, 5 х . 2 """, если делится на 3 с остат1 ком 2, З (х,+ г1)2

0,25 х, 2, если делится на 3 с остатком 1.

Формирование подкоренного выражения производится при помощи блока 16 сдвига. В зависимости от значения ,порядка аргумента х из блока 13 па1 мяти считывается управляющая информация и в блоке 16 сдвига производится сдвиг аргумента на один или два разряда вправо или значение аргумента передается на выход блока 16 сдвига без изменений.

Вычислеийе.мантиссы результата

z, = М7 (0.125 t 1) производится на .основе метода сегментной аппроксимации выражением у = А + Bz где константы А и В выбираются из условия

5 минимизации абсолютной погрешности.

Диапазон изменения аргумента (0,125 t 1) разбивается на интервалы, количество которых определяется требуемой точностью, причем границы интервалов определяются k старшими разрядами мантиссы аргу-. мента.

15

Устройство имеет вход 18 и выход

19 знака мантиссы, вход 20 и выход

21 порядка, вход 22 и выход 23 мантиссы и вход 24 синхронизации.

Блок сдвига легко построить при помощи селекторов-мультиплексоров.

Вычисление функции у = z производится на основе следующего алго-.. ритма. Аргумент х в формате с плаваю- 30 щей запятой представляется следующим образом: х=х, 2

35 где х, — мантисса аргумента (0,5 х, .ñ1); х — порядок аргумента (х — це2 2 лое число) . х,/з у =- х = x, ° 2

40 Так как величина х /3 не всегда является целой, то в необходимых слу,чаях производится сдвиг мантиссы

45 вправо с прибавлением необходимого количества единиц к порядку аргумента.

Изобретение относится к вычислительной .технике и предназначено для использования в вычислительных устройствах при обработке данных в форматах с фиксированной и плавающей запятой.

Целью изобретения является повышение быстродействия и расширение функциональных возможностей устройства за счет обработки чисел в формате с плавающей запятой»

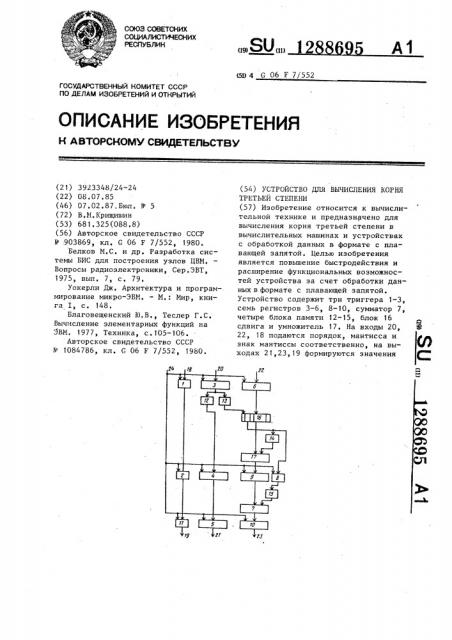

На чертеже представлена функциональная схема устройства.

Устройство содержит два триггера

1 и 2, четыре регистра 3-6, сумматор

7, пятый 8, шестой 9 и седьмой 1IO регистры, третий 11 триггер, четыре блока 12-15 памяти, блок 16 сдвига и умножитель 17.

На разных интервалах константы

А и В имеют различные значения, В блоке 14 памяти хранятся значения В, а в блоке 15 памяти — значения A+Ht„, где йк — значения начальной точки.

Устройство работает следующим образом.

В первом такте работы устройства в триггер 1 заносится значение знака мантиссы входного числа sign x,, в регистр 3 значение порядка входного числа х, В зависимости от значения порядка х в блоке 12 памяти осуществляется определение порядка результата z . Если используется представление порядка без смещения, то

1288695 хг/3, если хг делится на 3 нацело, (х,-5- 1)/3, если хг делится на 3 с остатком 2, (х + 2)/3, если хг делится г на 3 с остатком 1 °

Если же порядок имеет смещение р, то (x -p)/3+р, если хг-р делится на 3 на50 цело, хг= (хг-Р+1)/3+Р, если хг-р де- 1 лится йа 3 с остатком 2, (х -p+2)/3+р, если xz р делится на 3 с остатком 1.

Из блока 13 памяти происходит выборка информации управления S блоком

16 сдвига.

О, если делится на 3 нацело, $ = 1, если делится на 3 с остат- 25 ком 2, 2, если делится на 3 с остатком 1.

Если порядок хг имеет смещение р, то при определении $ принимается во 30 внимание величина хг — р, вместо хг, В зависимости от S в блоке 16 сдвига происходит сдвиг мантиссы х, S = 0 — сдвига нет (х,), $ = 1 — сдвиг на один разряд впра- 35 во (0,5 х,), S = 2 — сдвиг на два разряда вправо (0,25 ° х,).

По значению старших k разрядов с выхода блока 16 сдвига из блока 14 40 памяти выбирается константа В. В умножителе 17 происходит умножение константы В на значение n — - k младших разрядов на выходе блока 16 сдвига, .т.е. формируется одно из значений: 45

В (х4 t») 1

В (О 5 х,— Ек);

В (Оз25 х, — к)в где t — значение аргумента в начальной точке интервала аппроксимации, которому принадлежит точка х, (0,5 » х,или 0,25 х,).

Во втором такте работы устройства значение sign x, переписывается в триггер 2, а значение порядка результата zz — в регистр 4. Значение с выхода умножителя 17 записывается в регистр 9, а значение k старших разрядов с выхода блока 16 сдвига— в регистр 8. В триггер 1 и регистры

3 и 6 заносится новое значение аргумента со знаком. Из блока 15 памяти выбирается значение А + Bt„. На выходе сумматора 7 формируется значение мантиссы результата z .

А + ВТ„+ В(х, — t„)= А + Вх,=

= x, = z<, А + Bt„+ В(0,5x, — й„)= А + В»

А + Bt„+ В(0,25.х,— t„)= А + В ° з к0,25 х,= 0,25 х z,. если используется мантисса со скрытым старшим разрядом, где m — разрядность порядка;

n - разрядность мантиссы, По сравнению с известным устройством диапазон входных чисел расширен в

S 2

S 2"

Т=t„+ где, "рг раз.

При разрядности порядка m = 7

$q

128 раз. !

Такт работы устройства определяется временем задержки наиболее времяемкой ступени конвейера с "мну — время записи информации в регистр; — время задержки информации в блоке памяти, блоке сдвига и умножителе соответственно. л ц В

В третьем такте в триггер 11 заносится значение знака мантиссы результата sign х,, в регистр 5 — значение порядка результатах, в регистр 10— ! значение мантиссы результата z . Одновременно в триггер 1, регистры 3 и

6 заносится новый операнд, а в триггер 2 и регистры 4,9 и 8 — результаты промежуточных вычислений над вторым операндом, Устройство работает по конвейерному принципу. В каждом такте в него вводится новый операнд, В предлагаемом устройстве диапазон входных чисел значительно расширен.

Количество различных чисел, обрабатываемых устройством, равно

$1 = 2". 2"

При обработке 16-разрядных чисел быстродействие увеличено в 29 pas.

Составитель Н.Захаревич

Техред В,Кадар Корректор В.Бутяга

Редактор О.Головач

Заказ 7809/47 Тираж 694 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб,, д, 4/5

Производственно-полиграфическое предприятие, г,Ужгород, ул.Проектная, 4

5 12886

При использовании микросхем серии

133, 556 и 1802 = 35 нс, t„=80 нс, сдь нс мн 130 нс.

Формула изобретения

Устройство для вычисления корня третьей степени, содержащее два триггера, четыре регистра и сумматор, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия и расширения функциональных возможностей за счет обработки чисел в формате с плавающей запятой, устройство содержит пятый, шестой и седьмой регистры, третий триггер, четыре блока памяти, блок сдвига и умножитель, 20 причем информационный вход первого триггера соединен с входом знака мантиссы устройства, выход первого триггера соединен с информационным входом второго триггера-, выход которого соединен с информационным входом третьего триггера, выход которого является выходом знака мантиссы устройства, информационный вход первого регистра является входом порядка устройства, а выход первого регистра соединен с входами адреса первого и второго блоков памяти, выход первого блока памяти соединен с информационным входом второго регистра, выход которого

95 6 соединен с информационным входом третьего регистра, выход которого соеди-нен с выходом порядка устройства, выход второго блока памяти соединен с управляющим входом блока сдвига, информационный вход которого соединен с выходом четвертого регистра, информационный вход которого является входом мантиссы устройства, выход k старших разрядов блока сдвига (k =)log, Р(," где P — количество интервалов аппроксимации, ) j — символ наименьшего целого не меньшего) соединен с входом адреса третьего блока памяти и с информационным входом пятого регистра, выход третьего блока памяти соединен с входом первого сомножителя умножителя, вход второго сомножителя которого соединен с выходом (n — k) младших разрядов блока сдвига (п — разрядность мантиссы операнда), выход умножителя соединен с информационным входом шестого регистра, выход которого соединен с входом первого слагаемого сумматора,, вход второго слагаемого которого соединен с выходом четвертого блока памяти, вход адреса которого соединен с выходом пятого регистра, выход сумматора соединен с информационным входом седьмого регистра, выход которого является выходом мантиссы устройства, входы синхронизации всех регистров и триггеров подключены к входу синхронизации устройства.