Устройство для управления трехфазным транзисторным инвертором

Иллюстрации

Показать всеРеферат

Изобретение относится к электротехнике и может быть использовано для управления инверторами с широтноимпульсной модуляцией выходного напряжения . Целью изобретения является повышение надежности. На выходах дешифратора форми руются импульсы, продолжительность каждого из которых соответствует интервалу модуляции. Трехканальный коммутатор осуществляет распределение сформированных импульсов . В блоке осуществляется формирование низкочастотных и высокочастотных импульсов управления для транзисторов каждой фазы инвертора. Последовательности симметричных низкочастотных импульсов вырабатываются тремя Т-триггерами. Последовательности высокочастотных импульсов, модулированные по синусоидальному закону, вырабатываются тремя R-S-триггерами. 2 ил. О) ю ос 00 30

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (И) (Ю 4 Н 02 М 7/48

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМ,Ф СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТМРЫТИЙ

I (21) 3933011/24 — 07 (22) 19.07.85 (46) 07.02.87. Бюл. Ф 5 (72) В.И.Борцов, F..Ô.Ìàð÷åíêoâ, Л.Н.Морозов, А.В.Карелин,, С.И.Харин и Л.В.Демина (53) 621.314.27(088.8) (56) Патент США У 3487288, кл. Н 02 M 7/48, 1969.

Авторское свидетельство СССР и 1032592, кл. Н 02 M 7/48, 1981. (54) УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ТРЕХФАЗНЫМ ТРАНЗИСТОРНЫМ ИНВЕРТОРОМ (57) .Изобретение относится к электротехнике и может быть использовано для управления инверторами с широтноимпульсной модуляцией выходного напряжения. Целью изобретения является повышение надежности. На выходах дешифратора формируются импульсы, продолжительность каждого из которых соответствует интервалу модуляции.

Трехканальный коммутатор осуществляет распределение сформированных импульсов. В блоке осуществляется формирование низкочастотных и высокочастотных импульсов управления для транзисторов каждой фазы инвертора. Последовательности симметричных низкочастотных импульсов вырабатываются тремя Т-триггерами. Последовательности высокочастотных импульсов, модулированные по синусоидальному закону, вырабатываются тремя R-S-триггерами. 2 ил, 1288867

Изобретение относится к электротехнике и может быть использовано для управления трехфазными инверторами с широтно-импульсной модуляцией выходного напряжения, выполненными на основе трех однофазных инверторов, Цель изобретения — повышение надежности устройства.

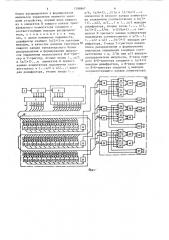

На фиг. 1 представлена функци— ональная схема устройства для управления трехфазным инвертором для n=72; на фиг. 2 — временные диаграммы сигналов, иллюстрирующие его работу, Устройство содержит генератор 1 15 импульсов, пятиразрядный счетчик 2 импульсов, 12-канальный распределитель 3 импульсов, состоящий из после довательно включенных четырехразрядного счетчика 4 и дешифратора 5 с 20 двенадцатью выходами 6.1-6.12, являющимися одновременно выходами всего распределителя 3, дешифратор 7 с выходами 8 и 9. 1-9 ° 6, трехканальный коммутатор 10, содержащий в каналах элементы И 11, 1-71. 12, 12. 1 — 12. 12,, 13.1-13,12 и элементы ИЛИ 14-16, блок 17 распределения и формирования импульсов управления с входными триггерами 18-23, причем триггеры 18, 20 3Q и 22 - R-S-типа, а триггеры 19, 21 и 23 — Т-типа, элементами И 24-35, элементами ИЛИ 36-41 и усилителями

42-47 мощности, выходы которых являются выходами блока 17. Генератор 7 счетчик 2 и распределитель 3 включены последовательно. Входы дешифратора 7 соединены с выходами счетчика 2, Первые входы элементов И трехканального коммутатора подключены к выходам 40

6, 1-6. 12 распределителя 3. Вторые входы элементов 11.1- 11.6 и 11.717.72 ïoäêëþ÷åíû соответственно к выходам 9.1-9.6 и 9.6-9.1.дешифратора 7. Вторые входы элементов 12.7 и

12.2, 12.3-12.8, 12.9-12.12 подключе" ны соответственно к выходам 9.5 и 9.6, 9 ° 6-9,1 .и 9.1-9." дешифратора 7. Вторые входы элементов 13.1-13.4, 13.513 ° 10, 13.11 и 13.12 подключены к выходам 9.4-9.1, 9.1-9,6 и 9.6 и 9.5 дешифратора 7. Входы элементов 14-16 соединены с выходами элементов И соответственно. T-входы триггеров 19, 21 и 23 соединены соответственно с выходами 6.12, 6.8 и 6.4 распределителя 3. S-входы триггеров 18, 20 и 22 соединены с (и/2+1)-м входом 8 дешифратора 7, а R-входы этих триггеров— с выходами элементов 14-16. Первые входы элементов 23, 27 и 25, 26 подключены соответственно к первому и второму выходам триггера 18, первые входы элементов 28, 31 и 29, 30 соответственно к первому и второму выходам триггера 20, первые входы элементов 32, 35 и 33, 34 — соответственно к первому и второму выходам триггера 22. Вторые входы элементов

24, 26 и 25, 27 соединены соответственно с первым и вторым выходами триггера 19, вторые входы элементов

28, 30 и 29, 31 - соответственно с первым и вторым выходами триггера 21, вторые входы элементов 32, 34 и 33, 35 — соответственно с первым и вторым выходами триггера 23. Входы элементов 36 подключены к выходам элементов

24, 25, входы элемента 37 — к выходам элементов 26 и 27, входы элемента

38 — к выходам элементов 28 и 29, входы элемента 39 — к выходам элементов 30 и 31, входы элемента 40 — к выходам элементов 32.и 33, входы элемента 41 — к выходам элементов 34 и

35. Входы усилителей 42, 44 и 46 соединены с выходами соответственно элементов 36 и 37, 38 и 39 и 40 и 47.

Входы усилителей 43, 45 и 47 подклю-, чены к выходам соответственно триггеров 19, 21 и 23. Выходы усилителей

42 и 47 мощности соединены с базовыми цепями транзисторов инвертора.

Устройство работает следующим образом.

Генератор 1 вырабатывает на своем. выходе последовательность импульсов с частотой f, кратной частоте Й синусоидального напряжения на выходе инвертора. Счетчик 2 в процессе свое-!

ro функционирования осуществляет деление частоты f на 32. Счетчик 4 имеет коэффициент счета, равный 12. На выходах 6.1-6.12 дешифратора 5 распределителя 3 последовательно формируются импульсы UC -776, (фиг. 2q), продолжительность каждого из которых соответствует интервалу модуляции Т .

Общая продолжительность двенадцати интервалов о соответствует полупериоду Т /2 выходного напряжения инверЦ тора.

Счетчик 2 делит интервал, на

32 части. Дешифратор ? в принципе имеет 32 выхода, однако для процесса формирования импульсов управления используются (и/2+1)-й тактовый вы1288867 ход 8, сигнал на котором совпадает с началом интервала 3, и шесть модуляционных (промежуточных) выходов

9.1-9.6. Определение номеров дешифрации последних производится путем подбора шести натуральных чисел, отличающихся друг от друга в порядке следования по синусоидальному закону.

В частности, если амплитуду выходного синусоидального напряжения харак- 10 теризует число "32", соответствующее емкости счетчика 2, то номера выходов 9.1-9.6 дешифратора 7 должны быть

Выбраны в следующем порядке: 4, 12, 19, 25, 29, 31. Использование в дешифраторе 7 модуляционных выходов

9.1-9.6 с такими порядковыми номерами обеспечивает возможность формирования в течение каждого из двенадцати интервалов Т шести интервалов от начала . 0 интервала с до моментов появления импульсов на соответствующих выходах дешифратора 7, длительности которых соотносятся между собой по синусоидальному закону (фиг. 2о). С помощью25 коммутатора 10 осуществляется распределение импульсов, сформированных дешифратором 7, по интервалам о, формируемым на выходах распределителя 3. При этом синусоидальный харак- 30 тер приобретает уже изменение длительностей от начала интервала до импульса дешифратора 7 от интервала к интервалу в течение полупериода каждой из трех фаз выходного напРяжения 35 инвертора.

Такая модуляция. сигналов обеспечивается описанным подключением входов элементов И трехканального коммутатора к выходам распределителя 3 40 и дешифратора 7.

В блоке,17 осуществляется формирование низкочастотных и высокочас,тотных импульсов управления для тран. зисторов каждой из фаз инвертора.

Последовательности симметричных низкочастотных импульсов U<<, U«, Uz> . (фиг.2 6„, y) вырабатываются триггерами 19, 21, 23, на Т-входы которых поступают сигналы соответственно с выхо-50 дов 6.12, 6.8 и 6.4 распределителя 3, чем обеспечивается 120 -ный фазовый сдвиг между фазами. Длительность каждого из низкочастотных импульсов управления соответствует полупериоду 55

Т г/2 выходного напряжения инвертора.

Последовательности высокочастотных импульсов U«, Пд,, U<,(фиг.2е,ж,y), модулированные по синусоидальному закону, вырабатываются триггерами

18, 20, 22, уста авливаемые в сигналами с тактового выхода 8 дешифратора 7 (первого по номеру дешифратора), сброс триггеров 18, 20 и 22 обеспечивается сигналами с выходов соответственно элементов 14-16. С помощью элементов 24-35 и 36-41 производится распределение фазных последовательностей высокочастотных импульсов Плз, U o, U< по полупериодам низкочастотных импульсов U„,,U

U > с образованием в конечном счете двухполупериодных псевдосинусоидальных сигналов. Усилители 42-47 помимо усиления сигналов управления обеспечивают гальваническую развязку всех управляющих цепей.

Усиленные низкочастотные сигналы с выходов усилителей 43, 45 и 47 используются для управления транзисторами инвертора, формирующими полуволны выходного напряжения. Усиленные высокочастотные сигналы с выходов усилителей 42, 44 и 46 обеспечивают управление транзисторами, обеспечивающими модуляцию выходного напряжения.

Предлагаемое устройство отличается сравнительно простой конструкцией, выполняется на типовых логических элементах, обеспечивает автоматическую фазировку при включении, что повышает его надежность при эксплуатации, и, кроме того, позволяет осуществлять пофазную стабилизацию выходного напряжения.

Формула из обре те ния

Устройство для управления трехфазным транзисторным инвертором, содержащее последовательно включенные генератор импульсов, счетчик импульсов и и-канальный распределитель импульсов, где n = 6К, К = 1, 2, 3 дешифратор с n/2 выходами, входы которого соединены с выходами счетчика импульсов, трехканальный коммутатор, каждый канал которого содержит и элементов И, входы которых являются входами трехканального коммутатора, выходы всех элементов И в каждом канале соединены с входами элемента

ИЛИ, выходы элементов ИЛИ являются выходами трехканального коммутатора, трехканальный блок распределения и формирования импульсЬв управления с шестью входными триггерами, выходы

5 1288867 6 блока распределения и формирования n/6Ä (n/6+1)...2/3n и (2/Зп+1)...n импульсов управления являются выхо- элементов И второго канала коммутатодами устройства, первый вход каждого ра подключены соответственно к (n/3+ из и элементов И каждого канала трех- +1)...п/2, и/2... 1 и 1... и/3 выходам канального коммутатора соединен с 5 дешифратора, вторые входы 1..., п/3, соответствующим выходом распредели- (n/3+1)...5/6n и (5/6n+1) ...п элетеля, о т л и ч а ю щ е е с я тем, ментов И третьего канала коммутатора что, с целью повышения надежности, подключены соответственно к n/3...1, дешифратор снабжен (n/2+1)-м тактовым 1...n/2 и п/2 ...(п/3+1) выходам девыходом, в качестве входных триггеров "О шифратора, T-вход T-триггера канала каждого канала трехканального блока блока распределения и формирования распределения и формирования импуль- импульсов управления соединен соотcoB n n eHH H no b 0 c R-Б-триг- ветственно с и, 2/3n n/3 выходом гер и T-триггер, вторые входы 1...n/2 распределителя импульсов, S-вход кажи (n/2+1)...n элементов И первого 15 дого К-S-триггера соединен с (n/2+1) канала коммутатора подключены соот- выходом дешифратора, а К-вход каждо ветственно к 1...n/2 и n/2...1 выхо- ro R-S-триггера соединен с, выходом дам дешифратора, вторые входы 1... соответствующего канала коммутатора.

1288867

Составитель В. Миронов

Техред А.Кравчук Корректор Е. Сирохман

Редактор А. Козориз

Тираж 683

Заказ 7822/56

Подписное

ВНИИПИ Государственного .комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб;, д. 4/5

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4