Устройство фазовой автоподстройки частоты

Иллюстрации

Показать всеРеферат

Изобретение относится к радиотехнике и обеспечивает расширение полосы удержания, Цифровой фазовый детектор 1 определяет фазовое рассогласование между входным синусоидальным сигналом и сигналом с делителя частоты (ДЧ) 4. Цифровой код, соотв. фазовому рассогласованию, проходит через усреднитель 3 и управляет частотой цифрового генератора, состоящего из цифрового сумматора (ЦС) 7, цифрового регистра (ЦР) 9, блока 6 добавления-вычитания импульсов, инвертора 2, D-триггера 5, элементов И 10, 12, ИЛИ 13. С приходом на ЦР 9 тактового импульса, прошедшего с источника 8 опорных импульсов через ДЧ 11, в него записывается цифровой код с ЦС 7. При переполнении ЦР 9 на выходе ДС 7 формируется сигнал переноса, поступающий на D-триггер 5, а в ЦР 9 заносится остаток. D-триггер 5 разрешает прохождение тактовых импульсов на блок 6. При поступлении 1 с выхода элемента ИЛИ 13 блок 6 изменяет свое состояс ние на 1. При этом фаза выходного сигнала на выходе ДЧ 4 скачком изменяется на величину qi t (D - коэф. деления ДЧ 4). Направление изменения фазы определяется знаком кода на выходе усреднителя 3. Введение D-триггера 5, элементов И 10,12, ИЛИ 13 и ДЧ 11 позволяет за счет повьш1ения тактовой частоты ЦР 9 расширить полосу удержания устр-ва.1 ил. (§ (Л ю эо эо

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (19) (11) А1 (504Н03 L 7 00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСКОМЪ(СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3866576/24-09 (22) 06.02.85 (46) 07,02.87.Бюл. № 5 (72) Н.И.Козленко, А.Р.Попов и Л.И.Алгазинова (53) 621. 396. 662 (088. 8) (56) Системы фазовой автоподстройки частоты с элементами дискретизации. Под ред. В. В.Шахгильдяна. M.:

Связь, 1979, с. 152.

Авторское свидетельство СССР

¹ 1116545, кл. Н 03 Ь ?/00,28.11.83, (54) УСТРОЙСТВО ФАЗОВОЙ АВТОПОДСТРОЙКИ ЧАСТОТЫ (57) Изобретение относится к радиотехнике и обеспечивает расширение полосы удержания. Цифровой фазовый детектор 1 определяет фазовое рассогласование между входным синусоидальным сигналом и сигналом с делителя частоты (ДЧ) 4. Цифровой код, соотв. фазовому рассогласованию, проходит через усреднитель 3 и управляет частотой цифрового генератора, состоящего из цифрового сумматора (ЦС) 7, цифрового регистра (ЦР) 9, блока 6 добавления-вычитания импульсов, инвертора 2, D-триггера 5, элементов

И10,,12, ИЛИ 13. С приходом на

ЦР 9 тактового импульса, прошедшего с источника 8 опорных импульсов через ДЧ 11, в него записывается цифровой код с ЦС 7. При переполнении

ЦР 9 на выходе IIC 7 формируется сигнал переноса, поступающий на D-триггер 5, а в ЦР 9 заносится остаток..

D-триггер 5 разрешает прохождение тактовых импульсов на блок 6. При поступлении "1" с выхода элемента

ИЛИ 13 блок 6 изменяет свое состояние на "1". При этом фаза выходного сигнала на выходе ДЧ 4 скачком изменяется на величину (g = t 2 й/D (D— коэф, деления ДЧ 4), Направление изменения фазы определяется знаком кода на выходе усреднителя 3. Введение В-триггера 5, элементов И 10,12

ИЛИ 13 и ДЧ 11 позволяет за счет повьппения тактовой частоты ЦР 9 расширить полосу удержания устр-ва.l ил.

1288907

Изобретение относится к области радиотехники и может использоваться в системах передачи цифровой информации °

Целью изобретения является ра.сширение полосы удержания.

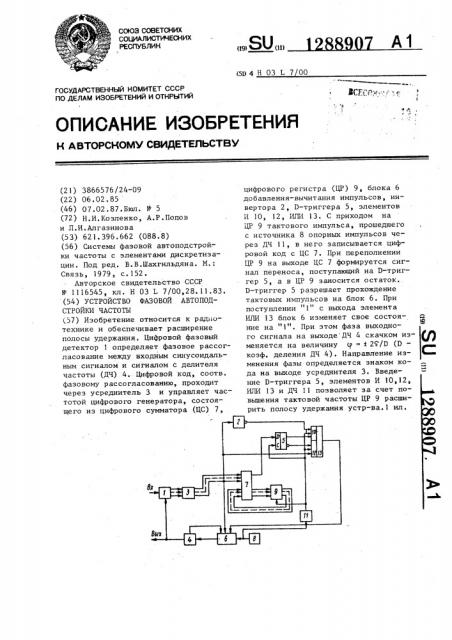

На чертеже представлена структурная электрическая схема устройства .Фазовой автоподстройки частоты.

Устройство фазовой автоподстройки частоты содержит цифровой фазовый детектор 1, инвертор 2, усреднитель

3, делитель 4 частоты, D-триггер 5, блок добавления вычитания 6 импуль.сов цифровой сумматор 7, источник 8 опорных импульсов, цифровой регистр

9, первый элемент И 10 дополнительный делитель 11 частоты, второй элемент И 12 и элемент KIH 13.

Устройство работает следующим образом.

Входной синусоидальный сигнал поступает на вход цифрового фазового детектора 1, представляющего собой, например, последовательно соединен— ные перемножитель, фильтр нижних частот, аналого-цифровой преобразователь. На второй вход цифрового фазового детектора 1 поступает сигнал с выхода делителя 4 частоты.

Код с выхода аналого-цифрового преобразователя, входящего в состав цифрового фазового детектора 1, поступает на усреднитель 3, который предназначен для уменьшения действия помех на точность подстройки фазы, а также для получения требуемых динамических характеристик. При отсутст— вии фазового рассогласования с выхода цифрового фазового детектора 1 на вход усреднителя 3 поступает нулевой код.

Выходной код усреднителя 3 управляет частотой цифрового генератора, состоящего из цифрового сумматора 7, цифрового регистра 9, блока добавления-вычитания 6, инвертора 2, Dтриггера 5, элементов И 10,12 и элемента ИЛИ 13.

Выходной код усреднителя 3 складывается в цифровом сумматоре 7 с содержимым цифрового регистра 9, Выходной код цифрового сумматора 7 с приходом тактового импульса, поступающего с выхода дополнительного делителя ll частоты на тактовый вход цифрового регистра 9, переписывается в него. Если код с усреднителя 3 рагде k — разрядность цифрового сумматора 7 и цифрового регистра 9;

U — код на выходе усреднителя 3.

Таким образом, код цифрового регистра 9 для произвольного момента времени определяется уравнением х (и+1) = х (n) + U-2 S (xtn), Uj, sign U Z+U! ъ 2 к (1) о !к+а

1, U)0

signU=U=О

35 — 1, П(0, Выходные импульсы переноса цифрового сумматора 7 переписываются в D-триггер 5, разрешающий в зависи40 мости от знака выходного кода усреднителя 3 прохождение тактовых импульсов на блок добавления-вычитания 6.

В момент появления единицы на

45 входе элемента ИЛИ 13 блок добавления — вычитания 6 изменит на единицу количество импульсов на входе делителя частоты 4.

При добавлении-вычитании одного

50 импульса фаза выходного сигнала на выходе делителя 4 частоты скачком

2т изменится на величину

55 где D — коэффициент деления делителя 4 частоты.

Направление изменения фазы определяется знаком кода на выходе усреднителя 3. вен 0...0, то с цифрового сумматора

7 в цифровой регистр 9 будет переписываться постоянный код, а сигнал переноса в цифровом сумматоре 7 фор5 мироваться не будет ° Если с выхода усреднителя 3 поступает код, отличный от О, то, с приходом тактового импульса. к содержимому цифрового регистра 9 будет добавляться (вычитаться) этот код. Когда содержимое цифрового регистра 9 достигнет максимального по модулю значения, равного 2, то на выходе переноса циф— !

5 рового сумматора 7 сформируется сигнал переноса, а в цифровой регистр

9 с приходом следующего тактового импульса перепишется остаток х!и+ 1) =х (и)+Б — 2

20 (g(n + 1) — q (n) 20

2)) fgt, (4) 3

ВНИИПИ Заказ 7823/58 Тираж 922 Подписное

Произв.-полигр. пр-тие, г. Ужгород, ул. Проектная, 4

3 1 889

При приращении фазы на выходе делителя 4 частоты можно записать

= Vp Б(х (и), U), (2)

Код в цифровом регистре 9 повто-, ряется через время, не превышающее к 2 T p, где Т вЂ” период тактовых импульсов на выходе делителя частоты. 10

Поэтому х(п) является периодической функцией.

Обозначим через р период функо ции x(n):

tn + р.) =- (и).

Суммируя левую и правую часть уравнений (1) и (2) в пределах от

n = k po n = k + р — 1 и подставо ляя значение суммы от S (х (n), U) на уравнения (1) в уравнение (2), получим выражение для приращения фазы выходного сигнала за время 6 t

= р,т.:

1 где f = — -- — частота тактовых

О импульсов на выходе дополнительного делителя 11 частоты.

Таким образом, частота выходного сигнала связана линейной зависимбстью с кодом усреднителя 3, т.е, выходным кодом цифрового фазового детектора

1. Изменение кода на выходе цифрово07 4 го фазового детектора 1 меняет частоту на выходе делителя 4 и подстраивает фазу выходного сигнала под входной сигнал.

Таким образом, введение D-триггера 5, элементов И и ИЛИ, дополнительного делителя 11 частоты позволяет за счет повышения тактовой частоты цифрового регистра 9 расширить полосу удержания устройства, равную

fo ьт.

Формул а изобретения

Устройство фазовой автоподстройки частоты, содержащее последовательно соединенные источник опорных импульсов, блок добавления-вычитания импульсов, делитель частоты, выход которого является выходом устройства, а дополнительный выход соединен с входом добавления-вычитания блока добавления-вычитания, цифровой фазовый детектор, второй вход которого является входом устройства, усреднитель, цифровой сумматор и цифровой регистр, выходы которого соединены с вторыми входами цифрового сумматооа, а также инвертор, о т л и ч а ющ е е с я тем, что, с целью расширения полосы удержания, между выходом переноса цифрового сумматора и входом управления блока добавлениявь.читания включены последовательно соединенные D-триггер, первый элемент И, первый вход которого соединен с выходом инвертора, и элемент

11ЛИ, между инвертирующим выходом

D-триггера и вторым входом элемента ИЛИ включен второй элемент И,между выходом источника опорных импульсов и вторыми входами первого и второго элементов И включен дополнительный делитель частоты, выход которого подключен также к входу синхронизации и тактовому входу D-триггера, при этом выход знака усреднителя соединен с входом инвертора, входом знака блока добавления-вычитания и третьим входом второго элемента И.