Аналого-цифровой преобразователь

Иллюстрации

Показать всеРеферат

Изобретение относится к области измерительной и вычислительной техники и может быть использовано для преобразования аналоговых величин в цифровые. Аналого-цифровой преобразователь содержит блок 1 сравнения , цифроаналоговый преобразователь 2, блок 3 управления, блок 4 постоянной памяти, блок 5 суммирования , регистр 6, блок 7 счетчиков, шину 8 запуск, входную шину 9, блок 10 мультиплексоров, выходные шины 11. Введенный блок 10 мультиплексоров обеспечивает последовательно-параллельное преобразование избыточного измерительного кода, получаемого на информационных выходах блока управления, в выходной двоичный код, что обеспечивает повышение д быстродействия аналого-.цифрового преобразователя. 2 з.п. ф-лы, 3 нл. (Л (Pl/2.f

СОЮЗ СО8ЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

А1 (19) (11) (51) 4 H 03 M 1/26

1. Ц

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТ8ЕНКЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

Н А BTOPCHOMV СВИДЕТЕЛЬСТВУ (21) 3925661/24-24 (22) 08.07.85 (46) 07.02.87. Бюл, У .5 (72) А.П.Стахов, А.Д.Азаров, В.П.11арценюк, В.Я.Стейскал и В.Я.Майстришин (53) 681.325(088.8) (56) Авторское свидетельство СССР

Р 788372, кл. H 03 M 1/26, 1978.

Авторское свидетельство СССР

У 1221750, кл. Н 03 M 1/26, !986. (54) АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ (57) Изобретение относится к области измерительной и вычислительной техники и может быть использовано для преобразования аналоговых величин в цифровые. Аналого-цифровой преобразователь содержит блок 1 сравнения, цифроаналоговый преобразователь 2, блок 3 управления, блок 4 постоянной памяти, блок 5 суммирования, регистр 6, блок 7 счетчиков, шину 8 "запуск", входную шину 9, блок 10 мультиплексоров, выходные шины 11. Введенный блок 10 мультиплексоров обеспечивает последовательно-параллельное преобразование избыточного измерительного кода, получаемого на информационных выходах блока управления, в выходной двоичный код, что обеспечивает повышение быстродействия аналого-цифрового пре-образователя. 2 з.п. ф-лы, 3 ил.

m и нии и. и

N=,7 а; м

С = OC М, 1, если А„- А„

О, если A„ A„; .

1! 12889

Изобретение относится к области вычислительной и цифровой измерительной техники и может быть использовано для преобразования аналоговых величин в цифровые. 5

Цель изобретения — повышение быстродействия аналого-цифрового преобразователя.

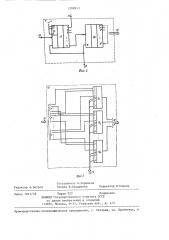

На, фиг.! приведена функциональная схема аналого-цифрового преобразователя; на фиг.2 — функциональная схема блока счетчиков; на фиг.3 — функциональная схема блока мультиплексоров.

Аналого-цифровой преобразователь (фиг.1) содержит блок 1 сравнения, цифроаналоговый преобразователь 2 (ЦАП), блок 3 управления, блок 4 постоянной памяти, блок 5 суммирования, регистр 6, блок 7 счетчиков, шину 8

Запуск", входную шину 9, блок 10 мультиплексоров, выходные шины 11.

Блок 7 счетчиков содержит счетный вход 12, группу выходов 13 и выход

14. Блок 10 мультиплексоров содержит информационные входы 15 и выходы !6, Блок 7 счетчиков (фиг.2) выполнен на первом счетчике 17 и втором счетчике 18. Блок 10 мультиплексоров

30 (фиг. 3) выполнен на п мультиплексорах 19< — 19„. ЦАП 2 должен быть выполнен на основе избыточного измерительного кода (ИИК).

Любое действительное число в ИИК можно представить в виде где а E (0,11 — двоичная цифра в -м разряде кода; — вес i-го разряда кода, причем 1 к < 2, ОДним из избыточных измерительных 4 кодов является код Фибоначчи.

Предлагаемое устройство функционирует в режиме аналого-цифрового преобразователя по методу поразрядного кодирования и осуществляет два преобразования: аналог — рабочий код (K1, ь) и рабочий кОД (К ) — ДВОичный кОД (Кд) ..

В результате первого преобразования происходит компенсация входного аналогового сигнала А „ компенсирующим сигналом А „ ЦАП 2 и формирование кода К рс,е В результате второго пре образования для получения требуемой точности происходит коррекция кода

К путем его преобразования в двоичный код К

Осуществляют групповую обработку разрядов при коррекции кода К

Для этого при изготовлении устройства определяются коды реальных значений весов разрядов ЦАП 2, ток и коды, соответствующие некоторым суммам кодов реальных значений весов разрядов.

Причем разряды ЦАП 2 разбиваются на

III группы по и разрядов таким образом, чтобы где К вЂ” количество разрядов ЦАП 2. и

При этом анализируется 2 возможных комбинаций для каждой группы разрядов ° Данные комбинации определяются как суммы кодов реальных весов единичных. разрядов каждой группы и записываются в БПП4.

Устройство работает следующим образом.

По шине 8 "Запуск" поступает импульс запуска, устанавливающий блок

3 управления в исходное состояние, обнуляющий регистр 6, второй счетчик

18 в блоке 7 и устанавливающий первый счетчик 17 в блоке 7 в состояВ процессе преобразования входного аналогового сигнала A„ в выходной код К„ производится уравновешивание

А„ выходным компенсирующим сигналом

ЦАП 2 А, Процесс уравновешивания производится блоком 3 управления последовательно от старших разрядов к младшим по методу поразрядного кодирования. При этом на каждом i-м такте на выходе ЦАП 2 формируется аналоговый сигнал А

С помощью блока 1 сравнения производится сравнение А„ с А„; . Выходной сигнал Y блока 1 сравнения удовлетворяет следующему условию:

С помощью блока 1, ЦАП 2 и блока

3 на информационных выходах последнего формируются разряды кода К

Причем, на (n + 1)-м такте аналогоцифрового преобразователя после того, как на выходе блока 3 сформируется п разрядов кода К„ Б, происходит ком3 12889 мутация последних на вторую адресную шину блока 4. На первую адресную шину блока 4 при этом поступает код с первых выходов блока 7. На выходах блока 4 появляется кодовая комбинация, соответствующая сумме кодов реальных весов единичных разрядов выделенной группы кода К Б .

Полученная кодовая комбинация подается на накапливающий сумма- 10 тор, выполненный на базе блока

5 и регистра 6, и суммируется с

его содержимым (нулевым). На после— дующих тактах преобразование происходит аналогично. В результате на 15 выходной шине ll устройства сформируется код К„, соответствующий входной величине А„, с точностью до младшего кванта.

Формула изобретения

1. Аналого-цифровой преобразователь, содержащий блок сравнения, первьй вход которого является вход- 25 ной шиной устройства, второй вход подключен к выходу цифроаналогового преобразователя, а выход подключен к информационному входу блока управления, установочный вход которого объединен с установочными входами блока счетчиков и регистра и является шиной "Запуск", информационные выходы блока управления подключены к соответствующим входам цифроана- 35 логового преобразователя, выход тактовых импульсов подключен к счетному входу блока счетчиков, группа выходов которого подключена к соответствующим первым адресным входам 40 блока постоянной памяти, выходы которого подключены к соответствующим первым входам блока суммирования, выходы которого подключены к соответствующим информационным входам ре- 45 гистра, выходы которого подключены

1З 4 к соответствующим вторым входам блока суммирования и являются выходными шинами устройства, о т л и ч а ю— шийся тем, что, с целью повышения быстродействия, введен блок мультиплексоров, информационные входы которого подключены к соответствующим информационным выходам блока управления, выходы подключены к соответствующим вторым адресным входам блока постоянной памяти, адресные входы подключены к соответствующим выходам группы блока счетчиков, выход которого подключен к тактовому входу регистра.

2. Преобразователь по п.l, о т— л и ч а ю шийся тем, что блок счетчиков выполнен на первом счетчике и на втором счетчике, выходы которого являются группой выходов блока счетчиков, счетный вход подключен к выходу старшего разряда первого счетчика, вход установки в нулевое состояние объединен с входом предварительной установки первого счетчика и является установочным входом блока счетчиков, информационные входы первого счетчика объединены и подключены к шине логической единицы, счетный вход первого счетчика является счетным входом блока счетчиков, а выход младшего разряда является выходом блока счетчиков.

3. Преобразователь по п.l, о т— л и ч а ю шийся тем, что блок мультиплексоров содержит и мультиплексоров с m информационными входами каждый, где m.п = К вЂ” число разрядов цифроаналогового преобразователя, одноименные информационные входы и мультиплексоров объединены в соответствующие m групп входов, которые являются соответствующими информационными входами блока мультиплексоров, выходы мультиплексоров являются выходами блока мультиплексоров.

1288913

Составитель В.Першиков

Техред JI.Cåðäþêoâà Корректор Н.Король

Редактор А.Петров

Заказ 7823/58

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Тираж 922 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

l

I is