Универсальный логический модуль

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике и предназначено для использования в качестве универсального логического элемента при синтезе нерегулярных структур дискретных устройств. Цель изобретения - упрощение модуля. Устройство содержит информационные входы , настроечные входы, пороговый элемент, элемент РАВНОЗНАЧНОСТЬ, выход модуля. Универсальный логический модуль реализует при соответствующей настройке типовые булевы функции относительно группы К„ преобразований . Настройка модуля состоит в подаче на настроечные входы модуля соответствующих сигналов из множества (О, 1, Х„, ХДпри этом на выходе модуля формируется булева функция с заданным рангом и индексом. 1 ил. U-jcX к ю 00

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„SU „„1290289 д5р 4 G 06 F 7 00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3894981/24-24 (22) 08.05.85 (46) 15.02.87. Бюл. № 6 (71) Харьковский авиационный институт им. Н. Е. Жуковского (72) В. А. Дергачев, С. А. Губка, В. А. Балалаев и А. Н. Аникии (53) 681,3 (088.8) (56) Авторское свидетельство СССР № 813410, кл. G 06 F 7/00, 1978.

Авторское свидетельство СССР № 1242931, кл. G 06 F 7/00, 1984. (54) УНИВЕРСАЛЬНЫЙ ЛОГИЧЕСКИЙ

МОДУЛЬ (57) Изобретение относится к автоматике и вычислительной технике и предназначено для использования в качестве универсального логического элемента при синтезе нерегулярных структур дискретных устройств.

Цель изобретения — упрощение модуля.

Устройство содержит информационные входы, настроечные входы, пороговый элемент, элемент РАВНОЗНАЧНОСТЬ, выход модуля.

Универсальный логический модуль реализует при соответствующей настройке типовые булевы функции относительно группы К„преобразований. Настройка модуля состоит в подаче на настроечные входы модуля соответствующих сигналов из множества(0, 1, Х„, X„),при этом на выходе модуля формируется булева функция с заданным рангом и индексом 1 ил

1290289

Изобретение относится к автоматике и вычислительной технике и предназначено для использования в качестве универсального логического элемента при синтезе нерегулярных структур дискретных устройств.

Цель изобретения — упрощение модуля.

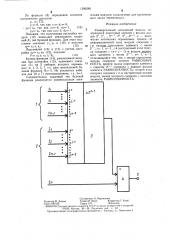

На чертеже приведена схема универсального логического модуля.

Модуль содержит информационные входы 1, настроечные входы 2, пороговый элемент 3, элемент РАВНОЗНАЧНОСТЬ 4, выход 5 модуля.

Пороговый элемент 3 и элемент РАВНОЗНАЧНОСТЬ 4 являются стандартными элементами вычислительной техники и могут быть выполнены по любой известной схеме.

Нумерация входов порогового элемента

3 ведется последовательно сверху вниз, т.е. вес первого (сверху на чертеже) входа порогового элемента 2, второго 2 и т.д.,(n — 1)го 2", (п)-го 20,..., 2" (возле каждого входа порогового элемента 3 указан его вес) .

Информационные входы 1 имеют п — 1 разряд. Настроечные входы 2 имеют п разрядов. Элементы схемы универсального логического модуля соединены следующим образом: i-й информационный вход 1; соединен с i-м (сверху) входом порогового элемента 3 с весом входа 2, (i 1, и — 1);

1-й настроечный вход 2; соединен с (и+)— — 1)-м входом порогового элемента 3 с весом входа 2, (j=1, п — 1); и-й настроечный вход 2„соединен с первым входом элемента РАВНОЗНАЧНОСТЬ 4, выход порогового элемента 3 соединен с вторым входом элемента РАВНОЗНАЧНОСТЬ 4, выход которого соединен с выходом 5 универсального логического модуля.

При описании работы использованы следующие обозначения:

V; — вес i-ro входа порогового элемента 3;

Т вЂ” порог; х; — значение сигнала на i-м информационном входе 1„(i=1, п — 1); у; — значение сигнала íà j-м настроечном входе 2j, (j=1, и);

У вЂ” значение сигнала на выходе порового элемента 3;

F — значение сигнала на выходе 5 модуля;

n — количество переменных, для которого модуль является универсальным относительно группы К„преобразований.

Рассмотрим работу модуля.

В общем случае сигнал на выходе m-входового порогового элемента с весами входов Vь Vz,..., V и порогом Т определяется следующим образом:

1, если Й V;x;) Т

У= * (1)

О, в п рот и вн ом случ ае.

Для конкретного вида порогового элемента 3, применяемого в данном универсальном логическом модуле, с учетом весов с;при с;=d; х„при с;= О, d;= 1 (8) х„при с;= 1, d;= О.

Пример. Пусть n=3, необходимо настроить модуль на реализацию типа булевой функции с рангом R=- 5 и индексом I= 1.

4р Для и= 3 выражение (1) имеет вид

1, если Х х;2 + Х у;2 ) 2, j (9)

О, в противном случае.

Выражению (9) соответствует булева функция

45 ср= у1у х1х / у у х1 / у1у (х1 \/ х ), (10)

Для и== 3 выражение (2) имеет вид

F= уз V у 9 (1 1)

Определяем значения настроечных сигналов по выражениям (4) и (8) для реа50 лизации типовой булевой функции с R= 5, 1= 1:

А=2 (2З вЂ” 5 + 1)= О;

В == 2.1+ 1= 3;

C= мин (0,3) = О;

55 Р=: макс (0 3) == 3.

Десятичным значениям C= О и D= 3 соответствуют двоичные коды, соответственно равные 000,011.

его входов, обозначением входных переменных и указанным порогом, выражение (1) имеет следуюший вид:

1, если Ъ х;2 + Z у;2 ) 2" ь (2)

О, в противном случае.

Булева функция на выходе элемента

РАВНОЗНАЧНОСТЬ 4 имеет вид

F= рДу.= «V у„V 9.у.. (3)

Предлагаемый универсальный логический модуль, как и прототип, предназначен для реализации К„типов булевых функций. Типовые булевы функции относительно группы К„ преобразования однозначно определяются двумя параметрами: рангом и индексом. Рангом булевой функции называется количество конституент единицы в ее совершенной дизъюнктивной нормальной форме (СДНФ). Индексом называется количество пар противоположных конституент единицы в ее СДНФ. Две булевы функции относятся к одному К„ типу, если их ранги и индексы совпадают.

Для реализации универсальным логическим модулем типа булевой функции с рангом R и индексом 1 необходимо подать на настроечные входы 2 модуля соответствую25 щие сигналы из множества (О, 1, х, х j..

Вычислян тся следующие значения:

А== 2(2" — R+ I); (4)

В== 2.1+1; (5)

С== мин (А, В); (6)

В==макс (А; В). (7)

Десятичные числа С и 0 представляются в виде двоичных чисел соответственно CIC2...

С„и did ...d,. Значения настроечных сигналов у,...,у„определяются следующим об разом:

1290289

Формул а изо б ретения

Составитель О. Березикова

Редактор М. Дылын Техред И. Верес Корректор Т. Колб

Заказ 7901 45 Тираж 673 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

По формуле (8) определяем значения настроечных сигналов: у„,1 — 1,3, у) —— О, так как с)= d)= О; ур= хз, так как ср= О, с1 = 1; (12) уз= хз, так как сз — О С13 — 1.

Покажем, что полученная настройка модуля (12) позволяет реализовать заданный К„тип булевой функции. Для этого подставим значения у), у2 в (10) и получим

ГР= ХЗ Х! Х2. (13)

Подставляя (13) в (11) с учетом настройки уз= хз из (12), получим

F= ХЗ Х Хд д/ ХЗ, (14)

Булева функция (14), реализуемая модулем при настройке (12), принимает значение «1» на 5 наборах входных переменных: О, 1, 2, 3, 7, т.е. ранг реализуемой булевой функции R= 5. Из указанных наборов два (О и 7) противоположны, т.е. 1=1.

Следовательно, заданный тип булевой функции реализуется универсальным логическим модулем (аналогично для произвольного числа переменных).

Универсальный логический модуль, содержащий пороговый элемент с весами входов 2о 2) 2" 2о, 2 2", п — количество логических переменных, причем i-й информационный вход модуля соединен с

10 i-м входом порогового элемента с весом

2, i= 1, n — 1, j-й настроечный вход модуля соединен с (n+ j — !)-м входом порогового элемента с весом 2, j= 1, п--1, отличающийся тем, что, с целью упрощения, модуль содержит элемент РАВНОЗНАЧНОСТЬ, причем выход порогового элемента с порогом 2 соединен с первым входом элемента РАВНОЗНАЧНОСТЬ, второй вход которого соединен с п-м настроечным входом модуля, выход которого соединен с выходом элемента РАВНОЗНАЧНОСТЬ.