Ячейка матричного коммутатора

Иллюстрации

Показать всеРеферат

Изобретение относится к области вычислительной техники и может быть использовано в качестве базового элемента при построении коммутационных систем многопроцессорных вычислительных структур. Цель изобретения - расширение функциональных возможностей за счет обеспечения двунаправленной коммутации. Ячейка матричного коммутатора (ЯМК) обеспечивает настройку двунаправленного канала связи по совпадению символических имен соединяемых устройств. ЯМК содержит схему сравнения , триггер, элемент И, шинный формирователь , первую и вторую информационные шины, вход синхронизации, вход сброса, настроечный вход, вход задания направления. При настройке ЯМК происходит сравнение последовательно-параллельных кодов символических имен устройств. При совпадении символических имен между устройствами образуется канал связи, обеспечивающий двунаправленный обмен информацией . В случае несовпадения символических имен подобный канал не образуется. 1 ил. ГО со о to х

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (so 4 G 06 F 7 00

t

1д (;и 1

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А ВТОРСКОМ,Ф СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3938743/24-24 (22) 01.08.85 (46) 15.02.87. Бюл. № 6 (72) А. Г. Накалюжный, В. П. Тарасенко, Я. И. Торошанко и Е. М. Швец (53) 681.3 (088.8) (56) Авторское свидетельство СССР № 602937, кл. G 06 F 7/00, 1975.

Авторское свидетельство СССР

¹ 928340, кл. G 06 F 7/00, 1980.

Авторское свидетельство СССР № 1121778, кл. G 06 F 7/00,,1983. (54) ЯЧЕЙКА МАТРИЧНОГО КОММУТАТОРА (57) Изобретение относится к области вычислительной техники и может быть использовано в качестве базового элемента при построении коммутационных систем многопроцессорных вычислительных структур.

„,Я0„„1290291

Цель изобретения — расширение функциональных возможностей за счет обеспечения двунаправленной коммутации. Ячейка матричного коммутатора (ЯМК) обеспечивает настройку двунаправленного канала связи по совпадению символических имен соединяемых устройств. ЯМК содержит схему сравнения, триггер, элемент И, шинный формирователь, первую и вторую информационные шины, вход синхронизации, вход сброса, настроечный вход, вход задания направления.

При настройке ЯМК происходит сравнение последовательно-параллельных кодов символических имен устройств. При совпадении символических имен между устройствами образуется канал связи, обеспечивающий двунаправленный обмен информа- а цией. В случае несовпадения символических имен подобный канал не образуется. ф

1 ил.

129029

Изобретение относится к вычислительной технике и может быть использовано в качестве базового элемента при построении коммутационных систем многопроцессорных вычислительных структур.

Цель изобретения — расширение функ5 циональных возможностей ячейки матричного коммутатора путем обеспечения двунаправленной коммутации.

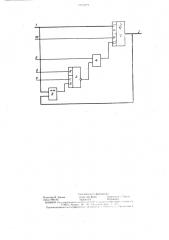

На чертеже изображена структурная схема ячейки матричного коммутатора. 10

Ячейка матричного коммутатора содержит первую и вторую и-разрядные информационные шины 1 и 2, RS-триггер 3, элемент И 4, настроечный вход 5, вход 6 сброса, шинный формирователь 7, схему 8 сравнения, вход 9 синхронизации, вход 10 задания направления. Значение и выбирается в соответствии с длиной слов, которыми производится обмен информацией в матричном коммутаторе.

Ячейка матричного коммутатора работает следующим образом.

Сигнал, подаваемый на вход 6 сброса, устанавливает триггер 3 в нулевое состояние. При этом с его инверсного выхода единичный сигнал через элемент И 4 поступает на первый управляющий вход шинно- 25 го формирователя 7, обеспечивая обмен информацией через шинный формирователь 7 между первой и второй информационными шинами при единичном сигнале на настроечном входе 5. Единичный сигнал на входе 10 задания направления разрешает передачу информации с первой 1 информационной шины во вторую 2, а нулевой потенциал на входе 10 задания направления разрешает передачу информации с второй 2 информационной шины в первую 1. Во время. настройки каналов связи в матричном коммутаторе на настроечный вход 5 поступает нулевой потенциал, который действует на протяжении всего времени настройки, и через элемент И 4 подается на первый управляющий вход шинного формирователя 7. 40

Под воздействием этого сигнала выходы шинного формирователя 7 переводятся в высокоимпедансное состояние, при этом запрещается обмен информацией между первой и второй информационными шинами. Коды, поступающие по первой 1 и второй 2 инфор- 4> мационным шинам и несущие информацию о символических именах коммутируемых каналов связи, подаются на схему 8 сравнения.

Причем при количестве разрядов k в символическом ымени оно выдается на схему 8

2 сравнения в течение ) k/è (тактов сравнения, задаваемых синхроимпульсами по входу 9 синхронизации.

При неравенстве разрядов в символических именах сигнал неравенства, формируемый на выходе схемы 8 сравнения, поступает на единичный вход триггера 3 и устанавливает его в единичное состояние по тактовому сигналу, подаваемому с входа 9 синхронизации. По окончании настройки на настроечнсм входе 5 устанавливается единичный сигнал. Если во время настройки на триггер 3 подан сигнал неравенства, то с его инверсного выхода нулевой уровень через элемент И 4 выдается на первый управляющий вход шинного формирователя 7, запрещая обмен информацией между первой 1 и второй 2 информационными-шинами. Если за время настройки сигнал неравенства не вырабатывался ; то триггер 3 остается в исходном состоянии и единичный потенциал с его инверсного выхода через элемент И 4 поступает на первый управляющй вход шинного формирователя 7, разрешая двунаправленный обмен информацией между первой 1 и второй 2 информационными шинами.

Формула изобретения

Ячейка матричного коммутатора, содержащая схему сравнения, RS-триггер и элемент И., причем первый и второй входы схемы сравнения соединены с первой и второй информационными шинами ячейки, вход сброса ячейки соединен с R-входом RS-триггера, первый вход элемента И соединен с настроечным входом ячейки, отличающаяся тем, что, с целью расширения функциональных возможностей путем обеспечения двунаправленной коммутации, ячейка содержит шинный формирователь, причем выход «Не равно» схемы сравнения соединен с S-входом RS-триггера, тактовый вход которого соединен с входом си нхронизации ячейки, вход задания направления ячейки соединен с первым управляющим входом шинного формирователя, второй управляющий вход которого соединен с выходом элемента И, второй вход которого соединен с инверсным выходом К8-триггера, первая информационная шина ячейки соединена с информационными входами шинного формирователя, выходы которого соединены с второй информационной шиной ячейки. (:ост;!ви !ель О. 13ерези кои;!

Редактор М. Дылын Текр»i И. Верее Корректор. 1. 11агии

Зак аз 7901/45 Тираж 6,3 1!одиисно

ВНИИПИ Госсдарствеигииго кочигг ги i. .(.(.! :и iå.i;i .. !си!!зрг !еиии и о!,n „;;, :, 11:3035, Моска;!, Ж 3;и ;i; ьив и;ю...;. -1 5

Производственио-llo.!!!Ã!12ôi!÷(c кое рс и !".1:в! |!е. . У,кi ооо.i. !. . 11роеi ll:!ÿ. 4