Устройство для выделения многоразрядного кода

Иллюстрации

Показать всеРеферат

Изобретение относится к области автоматики и вычислительной техники . Цель изобретения - расширение области применения за счет обеспечения возможности вьщеления средйего из п кодов, где п - нечетное. Устройство содержит п дешифраторов,где п - количество анализируемых кодов, блоков выделения минимального кода, блок выделения максимального к&да и шифратор. Поступающие коды преобразуются дешифраторами в унитарный код, затем среди всех возможn-t-1 ных сочетаний по из п кодов блоками вьщеления минимального кода осуществляется поиск минимального кода в каждом сочетании, а затем среди выделенньк g минимальных кодов блоком вьщеления максимального кода вьщеляется максимальный код, который шифратором преобразуется из унитарного кода в двоичный. 1 з.п. ф-лы, 1 ил. Q (Л С

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (11) (51)4 G06F 7 02

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А ВТОРСИОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3869462/24-24 (22) 19.03.85 (46) 15.02.87. Бюл. 1(6 (71) Институт технической кибернетики АН БССР (72) Г.А.Буткин и А.Г.Ярусов (53) 681.325.66(088.8) (56) Авторское свидетельство СССР

1(746501, кл. G 06 F 7/02, 1978.

Авторское свидетельство СССР

Ф 981987, кл. G 06 Р 7/02, 1981. (54) УСТРОЙСТВО ДЛЯ ВЫДЕЛЕНИЯ МНОГОРАЗРЯДНОГО КОДА (57) Изобретение относится к области автоматики и вычислительной техники. Цель изобретения " расширение . области применения за счет обеспечения возможности вьщеления средйего из и кодов, где n — нечетное. Устройство содержит и дешифраторов,где и — количество анализируемых кодов, g=C блоков вьщеления минимального и кода, блок вьщеления максимального кода и шифратор. Поступающие коды преобразуются дешифраторами в унитарный код, затем среди всех возможи+1 ных сочетаний по — — из и кодов

2 блоками выделения минимального кода осуществляется поиск минимального кода в каждом сочетании, а затем среди вьщеленных g минимальных кодов блоком вьщеления максимального кода выделяется максимальный код, который шифратором преобразуется из унитарного кода в двоичный. 1 з.п. ф-лы, 1 ил.

94 2 е с я тем, что, с целью расширения области применения за счет обеспечения возможности выделения среднего иэ и кодов, где п — нечетное, в него введены С блоков выделения минимального кода, блок выделения максимального кода и шифратор, причем

i-й вход j-ro дешифратора, где

=1,2,...,m, m — количество разрядов анализируемых кодов, 1=1,2,...,n является входом i-ro разряда j-ro ана-. лизируемого кода. устройства, k-й вход 1-Й группы входов первого блока выделения минимального числа, где

«ъ1 n+1

k=1,2»...,2, 1=1,2,..., соединен с k-м выходом 1-ro дешифратора, k-й вход 1-й группы входов P-го блока выделения минимального числа соединен с k-м выходом g р дешифратора, ( где (Р 1

8у- -«-( (-

P»P„+t

«»«ам

tl+ (=1,2 . g

1 при

1

1s(P(1 з при при при

1 r, ), t р, (1+

Pp= (S

z=Maxcfу»»уд» ° ° »y }

9 у, =минах,х,...,х„,,х, !; г г у ™ин 1Х»+»» «-i »+a+gl » 30 т -Р

У -МИН(х»Х, ° ° .,Х,Х

h г г

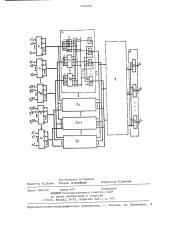

Анализируемые коды поступают по

1 l» входам 5, -5 и преобразуются дешифраторами 1, -l„ в унитарные коды.

В блоках выделения минимального кода 2,-2 формируются коды у,у ! 2

y> . При этом k-е диоды всех групп диодов, где k=1 2...,2, представляют собой элементы ИЛИ, которые выде- 40 ляют ненулевые разряды, а цепочка иэ элементов ИЛИ-НЕ 8, -8 выделяет самый младший из ненулевых разрядов, который устанавливает на выходах более старших элементов ИЛИ-НЕ 8 -8 45 г» » 45 нулевой потенциал. и-1 и-1

0 при g 1+ и-й выход v ro блока выделения минимального кода, где n=l,2,...,(2 — 1), v=1,2,...,С"„+ соединен с v-и входом и-й группы входов блока выделения максимального кода, и-й выход которого соединен с и-м входом шифратора, х-й выход которого является выходом i-го разряда выделенного кода устройства.

Формула изобретения

55! 12902

Изобретение,относится к автома1 тике и вычислительной технике.

Цель изобретения — расширение области применения за счет обеспече— .ния возможности выделения среднего из и кодов, где n - -нечетное.

На чертеже приведена схема устройства.

Устройство содержит и дешифраторов 1,-1, Сь блоков выделения ми- >0 нимального кода ?,-2, где р,=С

n+1 число сочетаний из n no, блок выделения максимального кода 3, шифратор 4, входы сравниваемых кодов

««

5, -5, где m — количество разрядов сравйиваемых кодов, выходы 6,-6

Блок выделения минимального кода п+1 (ы1 содержит — — групп диодов 7 -7 по 20

1

«П . 2 диодов в каждой группе и 2 элементов ИЛИ-НЕ 8 -8 а шифратор -

1 ll «««» элементы ИЛИ 9, -9

Выделение среднего z по и кодов выполняется следующим образом

Блок 3 выделяет из вектора (! у,, у,...,у } максимальный: код, которйй после преобразования его шифратором 4 иэ унитарного в двоичный является средним из (анализируемых кодов.! . Устройство для выделения многоразрядного кода, содержащее и дешифраторов, где п — количество анализируемых кодов, о т л и ч а ю щ е2. Устройство по п. 1, о т л ич а ю щ е е с я тем, что блок выделения минимального кода содержит п+1

«»» »« групп по 2 диодов каждый,2 элементов ИЛИ-НЕ, причем анод k-го диода 1-й группы является k-м входом 1--й группы входов блока, катоды

k-x диодов всех групп объединены и соединены с первым входом k-ro элемента ИЛИ-НЕ, выход первого элемента ИЛИ-НЕ соединен с вторыми входами f-х элементов ИЛИ-НЕ, где f=

М

=2,3,...,2, выход Е-го элемента

ИЛИ-НЕ является (f-1)-м выходом блока и соединен с (f+1)-м входом h-ro элемента ИЛИ-НЕ, где h=(f+l),(f+2$

» «Т«

° 4 ° » °

1290294 г

«Ф

Ь фР

Щ

Составитель B.Ãîðîõîâ

Редактор M.Äü ëûí Техред Л.Олейник Корректор M.Äåì÷èê

Заказ 7902/46 Тираж б73 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, R-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул, Проектная, 4