Арифметическое устройство

Иллюстрации

Показать всеРеферат

Изобретение относится к области вычислительной техники и может быть использовано при построении процессоров ЭВМ и устройств обработки цифровой информации. Целью изобретения 9 i-(H является расширение области применения устройства за счет реализации сложения и вычитания чисел со знаками и операции сравнения. Устройство содержит узел 1 формирования суммы и разности, сумматор 2 по модулю два, схему 3 сравнения, управляющий дешифратор 4, узел 5 формирования знака, группы сумматоров 6 и 7 по модулю два, узел 8 формирования переноса, входы 9 и 10 разрядов первого и второго операндов, входы 11 и 12 знаков первого и второго операндов, вход 13 кода операции, выходы 14 разрядов результата, выход 15 знака, выход 16 результата сравнения, вход 17 переноса , выход 18 переноса. 3 ил. ) П (Л С Фиг.1

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (51) 4 С 06 Р 7/38, ?/50

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3711920/24-24 (22) 20.03.84 (46) 15.02.87. Бкл. Ф 6 (72) С.В.Быков, Л.Н.Корягин и О.И.Гусаков (53) 681.325.5(088.8) (56) Мейзда Ф.- Интегральные схемы,—

M.: Мир, 1981, с. 100, рис. 4.25.

Микропроцессорные БИС и микроЭВМ/

Под ред. А.А.Васенкова, M. Сов. ра. дио, .1980, с. 112, рис. 3.20. (54) АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО (57) Изобретение относится к области вычислительной техники и может быть использовано при построении процессоров ЭВМ и устройств обработки цифровой информации. Целью изобретения

ÄÄSUÄÄ 1290298 является расширение области применения устройства за счет реализации сложения и вычитания чисел со знаками и операции сравнения. Устройство содержит узел 1 формирования суммы и разности, сумматор 2 по модулю два, схему 3 сравнения, управляющий дешифратор 4, узел 5 формирования знака, группы сумматоров 6 и 7 по модулю два, узел 8 формирования переноса, входы 9 и 10 разрядов первого и второго операндов, входы 11 и 12 знаков первого и второго операндов, вход

13 кода операции, выходы 14 разрядов результата, выход 15 знака, выход 16 результата сравнения, вход 17 переноса, выход 18 переноса. 3 ил.

1 12902

Изобретение относится к вычисли тельной технике и может быть использовано при построении процессоров

ЗВМ и устройств обработки цифровой информации.

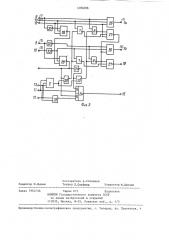

Цель изобретения — расширение области применения устройства за счет реализации сложения и вычитания чисел со знаками и операции сравнения, Иа фиг.l представлена структурная Ю схема арифметического устройства; на фиг.2 - функциональная схема узла формирования знака, на фиг.3 " вариант конкретного выполнения функциональной схемы двухраэрядного арифметического устройства.

Устройство содержит узел 1 формирования суммы и разности, сумматор

2 по модулю два, схему 3 сравнения, управляющий дешифратор 4, узел 5 фор-20 .мирования знака, группы сумматоров б и 7 по модулю два, узел 8 формирования переноса, входы 9 и 10 разрядов первого и второго операндов, 11 и 12 знаков первогo H BTQ

25 рого операндов, вход 13 кода операции, выходы 14 разрядов результата,,выход 15 знака, выход 16 результата сравнения, а также вход 17 и выход

18 переноса.

Узел 5 имеет входы 19-23 и содержит элемент И-ИЛИ 24 и сумматор 25 по модулю два.

Конкретный вариант построения устройства содержит сумматоры 26 по мо- 35 дулю два, образующие узел l формирования суммы и разности, мажоритарные элементы 27, образующие узел 8 формирования переноса, мажоритар««ые элементы 28, образующие схему 3 сравнения, сумматоры 6 и 7 по модулю два, сумматор 2 по модулю два, элементы

И-НЕ 29 и 30, образующие управляющий дешифратор 4, сумматор 25 по модулю два и элемент И-ИЛИ 24, входящие в узел 5 формирования знака, а также

1элементы НЕ 31-34.

Устройство работает следующим об|разом. 50

Логика работы узла 1 не зависит от операции сложения и вычитания, изменяется в этом плане только логика формирования сигналов разрядных переносов: при суммировании Yl = ABG +

+ АВС + АВС + АВС, при вычитании числа В из числа А У2 АВС + АВС +

+ АВС + АВС, при вычитании числа А из числа В 73 = АВС.+ АВС + АВС +

98 2

+ АВС, где С вЂ” входной перенос (заем) .

Формирование данных функций осуществляется следующим образом.

На сумматор 2 по модулю два подаются знак числа А и знак числа В; если код операции нулевой, что соответствует сложению, то при равенстве знаков чисел А и В на выходе сумматора 2 по модулю два присутствует сигнал, запрещающий прохождение сигналов со схемы 3 сравнения к группам сумматоров по модулю два 6 и 7. Сумматоры 6 и 7 по модулю два в этом случае не инвертируют входные числа

А и В, а так как нх знаки одинаковы, то на выходе узла 5 получим знак числа В. Если число А положительно, а число B отрицательно или наоборот и присутствует единичный код операции (вычитание), то на выходе сумматора

2 по модулю два будет сигнал, запрещающий прохождение сигналов с выходов схемы 3 сравнения на группы сумматоров 6 и 7 по модулю два. В узле ! выполняется операция сложения чисел А и В по модулю два. Схема 3 сравнения определяет большее по модулю число, знак которого передается на выход 15, а узел 8 осуществляет функцию Yl.

При одинаковых знаках чисел А и

В и операции вычитания сумматор 2 па модулю два дает разрешение на вход дешифратора 4, при этом знак большего по модулю числа проходит на выход 15, знак числа В проинвертирован, а большее по модулю число проинвертируется на сумматорах 6 или

7 по модулю два. Узел 8 выдает в этом случае сйгналы переноса в соответствии с логической функцией У2 или У3. На вход 17 подается сигнал входного переноса. На выходах 14 получим разность двух чисел, а на выходе 18 — сигнал выходного переноса.

Таким образом, результат операции не зависит от вариации поступления чисел на входы А и В, знаки чисел и их величины анализируются самим устройством, операции сложения и вычитания выполняются без применения дополнительного кода. В каждой операции вместе с результатом сложения или вычитания выдается результат сравнения чисел по модулюа

Устройство, представленное на фиг.3 осуществляет выдачу прямого

12902 кода суммы или разности в нечетных разрядах выхода и инверсного кода в четных разрядах.

Формула изобретения

Арифметическое устройство, содержащее узел формирования суммы и разности, узел формирования переноса и первую группу сумматоров по модулю два, причем входы первой группы узла 0 формирования суммы и разности соединены с входами разрядов первого операнда устройства и подключены к первым входам соответствующих сумматоров по модулю два первой группы, выходы которых соединены с соответствующими входами первой группы узла формирования переноса, входы второй группы узла формирования суммы и разности соединены с входами разрядов 20 второго операнда устройства, а входы третьей группы узла формирования суммы и разности соединены с соответствующими выходами узла формирования переноса, выходы узла формирования суммы и разности соединены с выходами разрядов результата устройства, вход переноса узла формирования переноса соединен с входом переноса устройства, о т л и ч а ю щ е е с я тем, что, с целью расширения области применения за счет реализации сложения и вычитания чисел со знаками и операции сравнения, устройство дополнительно содержит схему сравнения, 35 сумматор по модулю два, узел формирования знака, вторую группу сумматоров по модулю два и управляющий дешифратор, причем узел формирования знака содержит сумматор по модулю

98 4 два и элемент И-ИЛИ, первые входы сумматоров по модулю два второй группы соединены с соответствующими входами разрядов второго операнда устройства, а выходы подключены к соответствующим входам второй группы узла формирования переноса, вторые входы сумматоров по модулю два первой и второй групп соединены соответственно с первым и вторым выходами управляющего дешифратора, первый и второй информационные входы которого подключены к выходам Больше" и "Не больше" схемы сравнения, а стробирующий вход соединен с выходом сумматора по модулю два, первый и второй входы которого соединены с вхо. дами знаков первого и второго операндов устройства и подключены соответственно к первому входу элемента ИИЛИ и к первому входу сумматора по модулю два узла формирования знака, третий вход сумматора по модулю два соединен с вторым входом сумматора по модулю два узла формирования знака и подключен к входу кода операции устройства, выход сумматора по модулю два узла формирования знака соединен с вторым входом элемента И-ИЛИ, третий и четвертый входы которого соединены соответственно с выходами

"Больше" и "Не больше" схемы сравнения, а выход подключен к выходу знака устройства, входы первой и второй групп схемы сравнения соединены соответственно с входами разрядов первого и входами инверсных разрядов второго операндов устройства, а выход

"Больше" подключен к выходу результата сравнения устройства.

1290298

О 19 (г) 78

Редактор M.Äûëûí

Заказ 7902/46

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 р (rj

Составитель А.Степанов

Техред Л.Олейник Корректор M.Демчик

Тираж 673 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д, 4/5