Устройство для решения линейных интегральных уравнений вольтерры

Иллюстрации

Показать всеРеферат

Изобретение относится к области цифровой вычислительной техники , к устройствам для решения интегральных уравнений и может быть использовано как специализированное вычислительное устройство в измерительно-управлякнцих системах. Целью изобретения является повышение точности за счет устранения низкочастотной помехи. Устройство содержит два регистра коэффициента, два умножителя , сумматор, выходной и входной регистры, регистр промежуточной переменной и блок синхронизации с соответствующими связями между ними , что позволяет достигнуть цели изобретения. 1 ил. о (Л

е 9

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (11) (51) 4 G 06 F 7/64 15 32

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А BTOPGHOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОЕРЕТЕНИЙ И OTHPblTHA (21) 3861601/24-24 (22) 22.02.85 (46) 15.02.87. Бюл. У 6 (71) Институт проблем моделирования в энергетике AH УССР и Киевский политехнический институт им. 50-летия Великой Октябрьской социалистической революции (72) А.Ф.Верлань, Н.А.Максимович и А.Е.Коваленко (53) 681.32(088.8) . (56) Авторское свидетельство СССР

Ф 1099755, кл. G 06 F 15/32, 1981.

Авторское свидетельство СССР

9 1124322, кл. G 06 F.15/32, 1982. (54) УСТРОЙСТВО ДЛЯ РЕШЕНИЯ ЛИНЕЙНЫХ

ИНТЕГРАЛЬНЫХ УРАВНЕНИЙ ВОЛЬТЕРРЫ (57) Изобретение относится к области цифровой вычислительной техники, к устройствам для решения интегральных уравнений и может быть использовано как специализированное вычислительное устройство в измерительно-управляющих системах. Целью изобретения является повышение точности за счет устранения низкочастотной помехи. Устройство содержит два регистра коэффициента, два умножителя, сумматор, выходной и входной регистры, регистр промежуточной переменной и блок синхронизации с соответствующими связями между ними, что позволяет достигнуть цели изобретения. 1 ил.

Для линейных стационарных преобразователей ядро является разностным k(t,s)=k(t-s) и практическ . часто экспоненциальным

1 t

k(t)= = ехр(- =), < L (2) 40 где t — постоянная времени экспоненты.

Работа устройства основывается на следующих математических соотношениях и описывается этими соотношения- 45 ми. Представим (1) в дискретной форме, учитывая (2), получим выражение к

Е::—

s-О

=y(nh) kh-nh ехр(- - ††-)x(nh)h=

1 ,n =1,k; (3) 50 применим к (3) г-преобразование:

h 1 — — ", x(z)=y(z)

Т 1-pz (4)

55 где h - -период квантования импульсного устройства;

h Fexp(т) — константа.

1 12903

Изобретение относится к цифровой вычислительной технике, к устройствам для решения интегральных уравнений и может быть использовано как специализированное вычислительное устройство в измерительно-управляющих системах.

Цель изобретения — повышение точности sR счет устранения низкочастотной помехи. t0

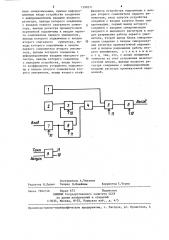

На чертеже схематично представлено предлагаемое устройство.

Устройство состоит из первого регистра 1 коэффициента, второго регистра 2 коэффициента, первого умножителя 3, сумматора 4, второго умножителя 5, выходного регистра 6, входного регистра 7, регистра 8 промежуточной переменной и блока 9 синхронизации, который имеет выходы 1О 20 и 11.

Устройство решает линейное интегральное уравнение Вольтерры первого рода

jk(t рs)x(s)ds=y(t) (1) о где x(t) — искомый исходный сигнал, y(t) — регистрируемый сигнал;

1 (,з) — ядро уравнения, представляющее собой весовую 30 функцию преобразователя; — время.

После проведения эквивалентных алгебраических преобразований (4) имеет вид . х{г)= - (y(z)-yz y(z)) (5)

Применим к (5) обратное z-преобразование: хл= (Ул Ууд.,) з (6) где х =x(nh); у =y(nh); у =yt.h (n-1) ) .

Соотношение 6 описывает алгоритм функционирования устройства.

Устройство работает следующим образом.

Перед началом работы устройства в регистр 1 заносится величина вЂ, в

h регистр 2- величина у=ехр(- ), в регистр 7 — величина у(0) .

Рассмотрим -й цикл работы устройства, который начинается по поступлении сигнала "Запуск" на соответствующий вход блока 9 синхронизации

В пер:вом такте по сигналу управления с выхода !1 блока 9 синхронизации осущес вляется операция приема кода в регистр 8 и умножения в умножителе 5. Перед вторым тактом работы устройства на выходе регистра 8 устанавливается величина у;,, на выхо((ди де умножителя 5 — величина -(у,, -gy )

На втором такте по сигналу управления с выхода 10 блока 9 осуществляются операции умножения в умножителе 3 и приема кода во входной 7 и выходной 6 регистры. По окончании второго такта работы на выходах входного 7 н выходного 6 регистров устанавливается соответственно значение у,, х., а на выходе умножи1 теля 3 — величина у.у, (-1

В конце i-ro цикла на выходе сумматора 4 устанавливается величина (у. — у,,) и устройство переходит в состояние ожидания очередного (i+1)-го импульса запуска, по приходе которого процесс повторяется, Формула изобретения

Устройство для решения линейных интегральных уравнений Вольтерры, содержащее входной регистр, регистр промежуточной переменной, выходной регистр, два умножителя, сумматор и

Л

Составитель А.Чеканов

Редактор М.Дылын Техред Л.Олейник Корректор С.Черни

Заказ 7902/46 Тираж 673 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4

3 12903 блок синхронизации, причем информационные входы устройства соединены с информационными входами входного регистра, выходы которого соединены с входами первого слагаемого сумма.тора, выходы регистра промежуточной переменной подключены к входам первого сомножителя первого умиожителя, выходы которого подключены к входам второго слагаемого сумматора, вы- 10 ходы которого подключены к входам первого сомножителя второго умножителя, выходы которого соединены с информационными входами выходного регистра, выходы которого соединены 15 с выходами устройства, входы первого коэффициента устройства подключены к входам второго сомножителя второго умножителя, входы второго коэффициента устройства подключены к входам второго сомножителя первого ум- ножителя, вход запуска устройства соединен с входом запуска блока син. хронизации, первый выход которого соединен с входами синхронизации входного и выходного регистров и входом разрешения работы первого умножителя, второй выход блока синхронизации соединен с входом синхронизации регистра промежуточной переменной и входом разрешения работы второго умножителя, о т л и ч а ю щ ее с я тем, что, с целью повышения точности за счет устранения низкочастотной помехи, выходы входного регистра соединены с информационными входами регистра промежуточной переменной.