Адаптивное устройство микропрограммного управления

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике и может быть использовано в качестве управляющего устройства специализированных ЦВМ, применяемых в системах автоматизированного управления. Цель изобретения - повышение быстродействия устройства. Устройство содержит регистр 1 адреса, первый дешифратор 2, первый блок 3 памяти микрокоманд , регистр 4 логических условий, первую группу 5 элементов И, буферньш регистр 6, вторую группу 7 элементов И, регистр 8 фиксации выполнения автономных микропрограмм, третью группу 9 элементов И, элемент 10 ИЛИ-НЕ, генератор 11 тактовых импульсов , второй элемент 12 задержки, второй счетчик 13 адресов, второй дешифратор 20, второй блок 21 памяти микрокоманд, схему 16 сравнения,сумматор 17, четвертую 24 группу элементов И, первый счетчик 19 адресов, третий дешифратор 14, третий блок 13 памяти микрокоманд, третий элемент 22 НЕ, пятый элемент 23 И, пятую группу 18 элементов И, шифратор 25, счетчик 26 микрокоманд, третий элемент 27 И, первый элемент 28 И,пер- .вый элемент 29 НЕ, четвертый элемент 30, второй элемент 31 НЕ, первый элемент 32 задержки, второй элемент 33 И. Поставленная цель достигается посредством сокращения времени выполнения микропрограмм на линейных участках. 1 ил. Л

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„Я0„„1290317 А1 (51) 4 0 06 Р 9/22

ОПИСАНИЕ ИЗОБРЕТЕНИЯ к авторском свидет льстам

ГОСУДАРСТ8ЕННЫЙ КОМИТЕТ СССР пО делАм изОБч=тений и ОткРытий (21) 3824070/24-24 (22) 17. 12. 84 (46) 15.02.87. Бюл. Ф 6 (72) В. А.Панюшкин и В.А.Харитонов (53) 681.32(088.8) (56) Авторское свидетельство СССР

Р 934471, кл. G 06 F 9/22, 1979.

Прангишвилли Н.В. Микропроцессо— ры и микроЭВМ. — M. Энергия, 1978, (54) АДАПТИВНОЕ УСТРОЙСТВО МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ (57) Изобретение относится к автоматике и вычислительной технике и может быть использовано в качестве управляющего устройства специализированных ЦВМ, применяемых в системах автоматизированного управления. Цель изобретения — повышение быстродействия устройства. Устройство содержит регистр 1 адреса, первый дешифратор 2, первый блок 3 памяти микрокоманд, регистр 4 логических условий, первую группу 5 элементов И, буферный регистр 6, вторую группу 7 элементов И, регистр 8 фиксации выполнения автономных микропрограмм, тре" тью группу 9 элементов И, элемент

10 ИЛИ-НЕ, генератор 11 тактовых импульсов, второй элемент 12 задержки, второй счетчик 13 адресов, второй дешифратор 20, второй блок 21 памяти микрокоманд, схему 16 сравнения,сумматор 17, четвертую 24 группу элементов И, первый счетчик 19 адресов, третий дешифратор 14, третий блок 15 памяти микрокоманд, третий элемент

22 НЕ, пятый элемент 23 И, пятую группу 18 элементов И, шифратор 25, счетчик 26 микрокоманд, третий элемент 27 И, первый элемент 28 И,первый элемент 29 НЕ, четвертый элемент 30, второй элемент 31 НЕ, первый элемент 32 задержки, второй элемент 33 И. Поставленная цель достигается посредством сокращения времени выполнения микропрограмм на линейных участках. 1 ил.

1 12903

Изобретение относится к автоматике и вычислительной технике и может быть использовано в качестве управляющего устройства специализированных 3ВМ, применяемых для управления сложными системами.

Цель изобретения — повышение быстродействия устройства.

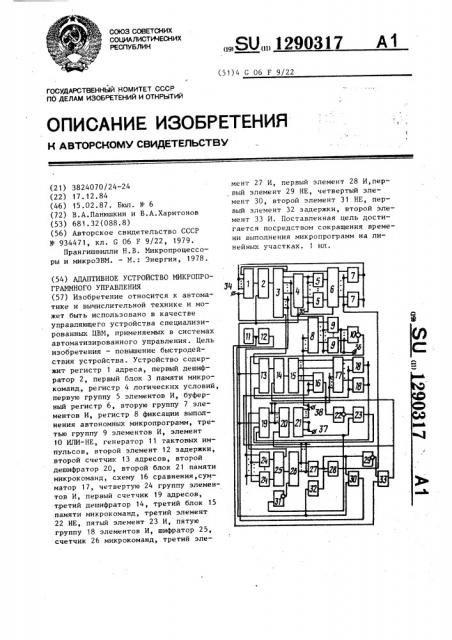

На чертеже представлена функциональная схема адаптивного микропро- !0 граммного устройства управления.

Устройство содержит регистр 1 адреса, первый дешифратор 2, первый блок 3 памяти микрокоманд, регистр

4 логических условий, первую группу 5 !5 элемен гов И, буферный регистр 6, вторую группу 7 элементов И, регистр 8 фиксации выполнения микропрограмм, третью группу 9 элементов И, элемент

10 ИЛИ-НЕ, генератор !1 тактовых им- 20 пульсов, второй элемент t2 задержки, второй счетчик 13 адресов, третий дешифратор 14, третий блок 15 памяти микрокоманд, схему 16 сравнения, сумматор 17, пятую группу 18 элементов И, первый счетчик 19 адресов, второй дешифратор 20, второй блок 21

Памяти микрокоманд, третий элемент

22 НЕ, пятый элемент 23 И, четвертую группу 24 элементов И, шифратор 25, счетчик 26 микрокоманд, третий элемент 27 И, первый элемент 28 И, первый элемент 29 НЕ, четвертый элемент

30 И, второй элемент 31 НЕ, первый элемент 32 задержки, второй элемент 35

33 И, первый вход 34 устройства,второй вход 35 устройства, первый 36, второй 37 и третий 38 выходы устройства.

Первый вход регистра 1 адреса 40 предназначен для записи в регистр адреса первой команды, с которой начинает работать устройство, второй вход — для установки в "0" регистра адреса, третий вход — для записи в регистр адреса очередной команды из буферного регистра 6, выход — для задания адреса в блоке 3.

Вход третьего запоминающего блока

15 предназначен для задания адреса очередной микрокоманды, для задания смещения относительно адреса выполняемой микрокоманды, считанной из второго запоминающего блока 21, задания номеров микрокоманд относительно начала выполняемой микропрограммы, при выполнении которой необходимо

50 изменить адрес очередной микрокоманды вторсго блока 21.

Первый вход первого счетчика 19 адресов предназначен для установки его в "0", второй вход — для записи адреса очередной микрокоманды из комбинационного сумматора, третий вход — для записи адреса первой микрокоманды при выполнении очередной команды устройством, четвертый вход— для увеличения адреса на единицу при естественном выполнении очередной

17 2 микрокс манды. Выход обеспечивает за— дание адреса очередной микрокоманды во втором запоминающем блоке 21 и подачу его на вход комбинационного сумматсра 17.

Первый вход второго счетчика 13 адресов предназначен для записи в него адреса первой микрокоманды при выполнении микропрограммы линейного участка программы, второй вход — для увеличения его содержимого на единицу при срабатывании схемы 16 сравнения, третий вход — для установки его в "0". Выход обеспечивает задание адреса очередной микрокоманды, хранящейся в блоке 15 °

Вход блока-3 предназначен для задания адреса очередной микрокоманды, выходы — для задания косвенного адреса очередной команды в буферном ре( истре 6, задания кода установки в 0" регистра 1 адреса, задания кода проверяемых логических условий в регистре 4 логических условий, задания признака автономности текущей микрокоманды, задания номера текущей микропрограммы, задания начального адреса .в третьем блоке 15.

Вход второго блока 21 памяти пред° Р назначен для задания адреса очередной микрокоманды, для задания сигналов микроопераций очередной микрокоманды, задания кода, управляющего вычитанием единицы из содержимого счетчика 26 микрокоманд и йрибавлением единицы к содержимому первого счетчика 19 адресов,выдачи информации в регистр 8 фиксации выполнения автономных микропрограмм.

Вход шифратора 25 предназначен для приема номера текущей микропрограммы, первый выход — для задания в счетчике микрокоманд кода длины текущей микропрограммы, второй выход— для задания адреса первой микрокоманды текущей микропрограммы.

3 12903

Первый вход комбинационного сумматора 17 предназначен для приема кода смещения из третьего блока 15, второй вход — для приема кода адреса очередной микрокоманды из первого счетчика 19 адреса, выход — для задания адреса, очередной микрокоманды во втором запоминающем блоке 21 при срабатывании схемы 16 сравнения.

Третий элемент 27 И предназначен 10 для выдачи единичного управляющего сигнала на первый элемент 28 И и первый элемент 29 НЕ при нулевом содержимом счетчика 26 микрокоманд, Единичное значение управляющий сигнал на 15 выходе третьего элемента 27 И может иметь в двух случаях (при нулевом содержимом счетчика 26 микрокоманд}: прямые входы элемента 27 И соединены с нулевыми выходами каждого из разря- 20 дов счетчика 26 микрокоманд, инверсные входы элемента 27 И соединены с единичными выходами каждого из разрядов счетчика 26 микрокоманд.

Устройство работает следующим образом.

В исходном состоянии все триггеры и регистры кроме блоков памяти находятся в нулевом состоянии.

Работа устройства начинается с записи в регистр 1 адреса с входа

34 устройства адреса первой команды. Генератор 11 тактовых импульсов через второй элемент 12 задержки и четвертый элемент 30 И при получении разрешающего сигнала с выхода третьего элемента 27 И, соответствующего нулевому содержимому счетчика

26 микрокоманд, производит установку 4О в "О" первого счетчика 19 адресов, второго счетчика 13 адресов, регистра 4 логических условий и буферного регистра 6, а также осуществляет пуск первого дешифратора 2. По сиг- 45 налу первого дешифратора 2 с первого блока 3 памяти микрокоманд считывается слово, соответствующее первой, выполняемой микропрограмме команды или первой выполняемой микропрограм.ме объединенной микропрограммы линейного участка программы. Сигналом с первого выхода первого блока 3 памяти микрокоманд регистр 1 адреса устанавливается в нулевое состояние.

Сигналом с второго выхода блока 3 памяти микрокоманд в буферный регистр 6 записывается косвенный адрес номера следующей микропрограммы. С третьего выхода первого блока 3 памяти микрокоманд в регистр 4 логических условий записывается код проверяемых логических условий.

Одновременно сигнал, соответствующий номеру текущей микропрограммы либо номеру первой микропрограммы объединенной микропрограммы при выполнении программы линейного участка, с четвертого выхода первого блока 3 памяти микрокоманд поступает через четвертую группу 24 элементов И, открытую разрешающим сигналом с выхода элементов 10 ИЛИ-НЕ вследствие нулевого состояния всех выходов третьей группы 9 элементов И, на вход шифратора 25. С выходов шифратора 25 в счетчик 26 микрокоманд записывается признак длины текущей микропрограммы, а в первый счетчик

19 адресов — адрес с первой микрокоманды текущей микропрограммы.

Одновременно с пятого выхода первого блока 3 памяти микрокоманд во второй счетчик 13 адресов записывается первый адрес массива, хранящего информацию об изменении микропрограмм, входящих в объединенную микропрограмму линейного участка программы.

После считывания информации из первого блока 3 памяти микрокоманд импульс генератора 11 через элементы задержки 12 и 32, первый элемент 28

И открывает вторую группу 7 элементов И и разрешает перезапись информации с буферного регистра 6 на регистр

1 адреса.

После считывания информации из первого блока 3 памяти микрокоманд и записи в счетчик 26 микрокоманд кода длины текущей микропрограммы либо кода длины объединенной микропрограммы его показания отличны от нуля, поэтому сигнал на выходе третьего элемента 27 И принимает нулевое значение и через первый элемент

29 НЕ открывает второй элемент 33 И, через который следующий тактовый импульс генератора 11 запускает второй дешифратор 20 и третий дешифратор 14. Далее по каждому тактовому импульсу генератора 11 в соответствии с адресом, записанным в первом счетчике 19 адресов из второго блока

3 памяти микрокоманд считываются микрокоманды выполняемой микропро- граммы, а в соответствии с адресом, 129031 записанным во втором счетчике 13 адресов из третьего блока 15 памяти микрокоманд считываются слова. С выхода 37 второго блока 21 памяти микрокоманд считываются сигналы микро- 5 операций, сигнал с второго выхода второго блока 21 памяти микрокоманд при открытом элементе 23 И увеличивает содержимое первого счетчика 19 адресов на единицу, кроме того, он 10 уменьшает содержимое счетчика 26 микрокоманд на единицу. Сигналы с первого выхода третьего блока 15 памяти микрокоманд поступают на первые входы сумматора 17, на вторые 15 входы которого поступает код адреса с первого счетчика 19 адресов, в результате суммирования этих кодов в сумматоре 17 формируется исполнительный адрес очередной микрокоманды.Сиг- 20 налы с вторых выходов третьего блока 15 памяти микрокоманд поступают на первые входы схемы 16 сравнения, на вторые входы которой поступает код с выхода счетчика 26 микрокоманд. 2

При совпадении этих кодов на выходе схемы 16 сравнения формируется управляющий сигнал на входы пятой группы 18 элементов И и исполнительный адрес микрокоманды через пятую груп- 30 пу 18 элементов И с выхода сумматора

17 записывается в первый счетчик 19 адресов. Кроме того, управляющий сигнал с выхода схемы 16 сравнения увел.почивает содержимое второго счетчика 13 адресов на единицу и через третий элемент 22 HE запрещает пересылку единицы с второго выхода второго блока 21 памяти микрокоманд через пятый элемент 23 И на вход пер- 40 вого счетчика 19 адресов. С приходом очередного тактового импульса с генератора 11 из второго блока памяти микрокоманд считывается микрокоманда по адРесу, переписанному в первый 45 счетчик 19 адресов из сумматора 17, а из третьего блока l5 памяти микрокоманд считывается командное слово из ячейки с номером, на единицу большим, чем предыдущая. При несовпадении кодов, считываемых с второго выхода третьего блока 15 памяти микрокоманд и первого счетчика 19 адресов, элементы 18 И закрыты, вследствие чего исполнительный адрес выхода суммато- 5> ра 17 в первый сче чик 19 адресов не переписывается, третий элемент 22 HE открывает пятый элемент 23 И и управляющий сигнал с второго вь1хода вто7 6 рого блока 21 памяти микрокоманд увеличивает содержимое первого счетчика 19 адресов на единицу. При показаниях счетчика 26 микрокоманд, отличных от нуля, следующий тактовый импульс аналогично описанному осуществляет считывание микрокоманд из второго блока 21 памяти микрокоманд.

В процессе работы адаптивного микРопрограммного устройства управления при получении на втором входе 35 устройства соответствующего сигнала с выходов элементов И первой группы 5 возможно изменение показаний буферного регистра 6.

После окончания выполнения очередной микропрограммы показание счетчика 26 микрокоманд равно нулю. При этом импульс генератора 11 через элементы 12 и 32 задержки, первый элемент 28 И и вторую группу 7 элементов

И передает адрес номера следующей микрокоманды, соответствующий следующей микропрограмме или группе объединенных микропрограмм линейного участка программы с буферного регистра

6 на регистр 1 адреса.

Следующий импульс генератора 11 через второй элемент 12 задержки и четвертый элемент 30 И устанавливает в исходное состояние первый и второй счетчики 19 и 13 адресов соответственно, регистр 4 логических условий и буферный регистр 6. Кроме того, осуществляется запуск дешифратора 2, считывается очередное слово из первого запоминающего блока 3 и работа устройства осуществляется аналогично описанному.

В случае считывания иэ первого запоминающего блока 3 слова, содержащего код автономной микропрограммы либо код объединенной автономной микропрограммы, с четверных выходов первого блока памяти микрокоманд поступает код, соответствующий этой микропрограмме, на входы элементов 9 И.

Однако эти элементы остаются в закры,том состоянии„ так как в регистре 8 фиксации выполнения автономных микропрограмм ке записан код этой микропрограммы. Поэтому работа устройства продолжается аналогично описанному. При выдаче из второго блока 21 памяти микрокоманд кода последней микрокоманды автономной микропрограммы на третьих выходах второго . блока 21 памяти микрокоманд появляется сигнал и в регистр 8 фиксации

1290317

55 выполнения автономных микропрограмм . записывается соответствующий код.

При необходимости повторного выполнения этой микропрограммы управляющий сигнал с выхода регистра

8 фиксации выполнения автономных микропрограмм и сигнал с четвертых выходов первого блока 3 памяти микрокоманд откроют третью группу 9 элементов И и выдадут сигнал на третий выход устройства, обеспечивающий считывание из памяти результата выполненной автономной микропрограммы.

Кроме того, этот сигнал через первый элемент 10 ИЛИ-НЕ закрывает входы элементов 24 И четвертой группы,запрещая запись информации в шифратор

25. Так как счетчик 26 микрокоманд остается в нулевом состоянии, то следующий тактовый импульс генератора 11 через элементы 12 и 32 задержки, первый элемент 28 И и вторую группу 7 элементов И передает косвенный номер следующего слова первого блока 3 памяти микрокоманд в регистр 1 адреса. Дальше устройство работает аналогично описанному. формула изобретения

Адаптивное устройство микропрограммного управления, содержащее регистр адреса, первый дешифратор, первый блок памяти микрокоманд,регистр логических условий, первую группу элементов И, буферный регистр, вторую группу элементов И, регистр фиксации микропрограмм, третью группу элементов И, элемент ИЛИ-НЕ, генератор импульсов, первый элемент задержки, первый счетчик адресов, второй дешифратор, второй блок памяти микрокоманд, четвертую группу элементов И, шифратор, счетчик микрокоманд, с первого по четвертый элементы И, второй элемент задержки, первый и второй элементы НЕ, причем входы кода команды и признака начала команды устройства подключены соответственно к первой группе информационных входов регистра адреса и входу установки в "0" регистра фиксации микропрограммы, выход регистра адреса соединен с информаци,онным входом первого дешифратора, выход которого соединен с адресным

l входом первого блока памяти микрокоманд, выход признака сброса кото5

30 рого соединен с входом установки в

"0 регистра адреса, выходы поля косвенного адреса первого блока памяти микрокоманд соединены с первой группой информационных входов буферного регистра, выход поля логических условий первого блока памяти микрокоманд соединен с информационным входом регистра логических условий, выходы которого поразрядно подключены к первым входам элементов И первой группы, выходы которых подключены к второй группе информационных входов буферного регистра, вторые входы элементов И первой группы соединены с входами внешних условий устройства, выходы буферного регистра поразрядно подключены к первым входам элементов

И второй группы, выходы которых подключены к второй группе информационных входов регистра адреса, выходы поля микропрограммы первого блока памяти микрокоманд соединены с вторыми входами элементов И третьей группы, выходы поля адреса микропрограммы первого блока памяти микропрограмм соединены с первыми входами элементов И четвертой группы, вторые входы которых подключены к выходу элементов ИЛИ-НЕ, выходы элементов И четвертой группы соединены с входами шифратора, первый выход которого подключен к первому информационному входу первого счетчика адреса, второй выход шифратора соединен с информационным входом счетчика микрокоманд, информационные выходы которого подключены к входам третьего элемента

И, выход которого соединен с первыми входами первого и четвертого элементов И и с входом первого элемента НЕ, выход второго элемента задержки подключен к второму входу первого элемента И, выход которого соединен с вторыми входами элементов И второй группы, второй вход четвертого элемента И подключен к выходу первого и входу второго элементов задержки, выход четвертого элемента И соединен с входами сброса первого счетчика адреса, регистра логических условий буферного регистра и стробирующим входом первого дешифратора, выход первого элемента НЕ подключен к первому входу второго элемента И, второй вход которого соединен с входом первого элемента задержки и выходом генератора импульсов, выход второго элемента

0317 I0 элемента И, информационные выходы второго счетчика адресов соединены с информационным входом третьего.дешифратора, стробирующий вход которого. соединен с выходом второго элемента И, выход третьего дешифратора — с адресным входом третьего блока памяти микрокоманд, выход поля смещения которого соединен с первым

10 входом сумматора, второй вход которого соединен с информационным выходом первого счетчика адреса, выход поля относительного адреса третьего блока памяти микрокоманд соединен с первым входом схемы сравнения, второй вход которой соединен с информационньпк вйходом счетчика микрокоманд, выход схемы сравнения подключен к счетному входу второго счетчика ад20 реса, к вторым входам элементов И пятой группы и входу третьего элемента НЕ, выход сумматора соединен поразрядно с первыми входами элементов И пятой группы, выходы которых соединены с вторыми информационными входами первого счетчика адреса,выход третьего элемента НЕ соединен с первым входом пятого элемента И, второй вход которого соединен с выходом признака модификации второго блока памяти микрокоманд, выход пятого элемента И соединен со счетным входом первого счетчика адреса.

9 129

И подключен к стробирующему входу второго дешифратора, информационный вход которого подключен к информационному выходу первого счетчика адреса, выход второго дешифратора подключен к адресному входу второго блока памяти микрокоманд, выход поля микропрограмм которого подключен к информационному входу регистра фиксации микропрограмм, выходы которого поразряцно подключены к первым входам элементов И третьей группы, выходы которых подключены к входам элемента ИЛИ и соединены с выходами индикации выполняемых микропрограмм устройства, выход поля операций второго. блока памяти микрокоманд является управляющим выходом устройства, выход признака модификации второго блока памяти микрокоманд соединен с входом второго элемента НЕ, выход которого подключен к счетному входу счетчика микрокоманд, о т л и ч а ю щ ее с я тем, что, с целью повышения быстродействия, оно содержит второй счетчик адресов, третий дешифратор, третий блок памяти микрокоманд, схему сравнения, сумматор, пятую группу элементов И, третий элемент НЕ, пятый элемент И, причем выход поля адреса первого блока микрокоманд соединен с информационным входом второго счетчика адреса, вход сброса которого соединен с выходом четвертого I

Составитель А.Сашкин

Техред А,Кравчук Корректор Т.Колб

Редактор М.Бандура

Заказ 7903/47 Тираж 673.

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб„, д. 4/5

Подписное

Производственно-полиграфическое предприятие, г.ужгороц, ул.Проектная, 4