Устройство для преобразования выражений в польскую инверсную запись

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике. Целью изобретения является повьппение достоверности работы за счет обеспечения контроля парности открывающей и закрывающей скобок, принадлежности символов / входного выражения множеству лексических единиц баланса операторов и операций, обеспечения классификации ошибок и повьппения быстродействия. .Устройство содержит регистр 1, депгафратор 2 лексических единиц, блок 3 памяти, дешифратор 4, блок 5 микропрограммного управления, реверсивный регистр 6 сдвига, коммутатор 7, ретгистр 8. 6 ил. нтт W со ел 00 gjuf.t

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

А1 ()9) SU (I() (д1) 4 G 06 F 15/38 9/44

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3950536/24-.24 (22) 30. 08. 85 (46) 15. 02. 87. Бюл. У 6 (72) В.К. Водопьянов, В. Н, Завьялов и В.Н. Цымбал (53) 681. 322. 01 (088. 8) (56) Авторское свидетельство СССР

Ф 890403, кл. G 06 F 15/38, 1980.

Авторское свидетельство СССР

В 1130879, кл. G 06 F 15/38, 1982. (54) УСТРОЙСТВО ДНЯ ПРЕОБРАЗОВАНИЯ

Г>ЫРАЖЕНИЙ В ПОЛЬСКУЮ ИНВЕРСНУЮ ЗАПИСЬ (57) Изобретение относится к вычислительной технике. Целью иэобретения является повьппение достоверности работы за счет обеспечения контроля парности открывающей и эакрывающей скобок, принадлежности символов . входного выражения множеству лексических единиц баланса операторов и операций, обеспечения классификации ошибок и повьппения быстродействия. ,Устройство содержит регистр 1, дешифратор 2 лексических единиц, блок 3 памяти, дешифратор 4, блок 5 микропрограммного управления, реверсивный регистр 6 сдвига, коммутатор 7, регистр 8. 6 ил.

1 1290358 2

Изобретение относится к вычисли- нирование описано блок-схемой микротельной технике и может быть исполь- программного .Управления (фиг.6), где зовано в автоматизированных системах входные сигналы х<, х, х> формирует обработки данных н производства про- дешифратор 4, с х4 по х8 — дешифраграмм для электронных вычислитель- 5 тор 2 лексических единиц, х, х„„ ных машин (ЭВМ).,хн — блок 6 контроля, сигналы микро-!

Целью изобретения является повы- команд с У4 по у, формиРУет блок 5 шение достоверности работы путем микропрограммного управления. Содеробеспечения контроля парности откры- жательный смысл входных сигналов и вающей и закрывающей скобок, принад- микрокоманд следующий: лежности символов входного выраже1, если ход операции, занесенный в старшие разряды ре.гистров сдвига блока 3 памяти, имеет больший приоритет, чем код операции, занесенный в предшествующие старшим разряды регистров, 0 — в противном случае. ния множеству лексических единиц, баланса операторов и операций, обеспечения классификации ошибок и повы15 шения быстродействия.

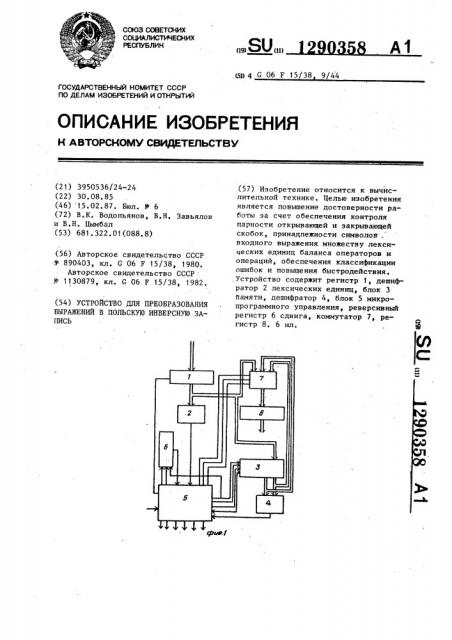

На фиг.1 представлена структурная схема устройства на фиг.2 — структурная схема блока памяти, на фиг,3структурная схема блока микропрограммного управления, на фиг.4 — схема, 20 реверсивного регистра сдвига, на фиг. 5 — схема реверсивного регистра сдвига блока памяти на фиг.6 — блоксхема микропрограммного управления устройством.

Устройство содержит регистр 1, дешифратор 2 лексических единиц, блок 3 памяти, дешифратор 4, блок 5 микропрограммного управления, реверснвный регистр 6 сдвига, коммутатор 7, регистр 8 реверсивные регистры 9 сдвига, программируемая логическая матрица И 10, программируемая логическая матрица ИЛИ 11, узел 12 памяти, элемент ИЛИ 13, гене- 35 ратор 14 тактовых импульсов, триггер 15, элемент 16 задержки, элемент И 17, группу 18 триггеров, группу 19 элементов ИЛИ, группу 20 элементов И, группу 21 триггеров, груп- 0 пу 22 элементов ИЛИ, группу 23 элементов И, элемент НЕ 24, узел 25 за:писи разряда. х =

1, если содержимое старших разрядов регистров сдвига блока 3 памяти равно значению кода "Пустой символ", 0 - в противном случае. х =

z если содержимое старших разрядов регистров сдвига блока 3 памяти равно значению кода открывающей скобки — в противном случае

1, если очередная лексическая единица исходного выражения есть открывающая скобка

0 — в противном случае.

1, если очередная лексическая единица исходного выражения есть операнд

0 — в противном случае. х =

4 х =

1, если очередная лексическая единица исходного выражения х = есть oIIepaHp9

0 — в противном случае.

Регистр 1 используется для хране- 45 ния очередной лексической единицы исходного выражения, дешифратор 2 лексических единиц разделяет лексические единицы на операнды, операции, скобки.

Блок 3 памяти — это память с последовательным безадресным принципом записи и чтения. Дешифратор 4 совместно с блоком памяти реализуют логическую функцию выработки и сравнения приоритетов. 55 если очередная лексическая единица исходного выражения есть закрывающаяся скобка, — в противном случае. х = т если очередная лексическая единица исходного выражения есть конец выражения — в противном случае.

1, если содержимое третьего разряда реверсивного регистра 6 сдвига есть единица, 0 — в противном случае.

Блок 5 микропрограммного управления организует взйимодействие всех элементов устройства и его функциох =

1290358 к =

О х =

» у

У4

7 у, у» у

12 у (4

У

16 если содержимое первого разряда реверсивного регистра 6 сдвига есть единица, — в противном случае. если содержимое четвертого разряда реверсивного регистра 6 сдвига есть единица, — в противном случае. разблокировать/заблокировать 50 регистр 1, записать содержимое регист-. ра 1 в N-e (старшие) разряды регистров сдвига блока памяти; 55 сдвинуть влево содержимое регистров сдвига блока памяти, переключить коммутатор 7 на запись из регистра 1, установить начальные значени 20 регистра 6 (значение кода

0100) и регистров сдвига блока 3 памяти (значение кода "О" в (N-1) разрядах), выдать сигнал ошибки "Отсутствует закрывающая скобка", переключить коммутатор 7 на запись из (N-1) разрядов регистров сдвига блока 3 памяти, 30 сдвинуть вправо на один разряд содержимое сдвига блока 3 памяти, переключить коммутатор 7 на запись из N разрядов регист- 35 ров сдвига блока 3 памяти, выдать сигнал ошибки "Отсутствует открывающая скобка" выдать сигнал ошибки "Лексическая единица не принадле- 40 жит алфавиту лексических единиц"; выдать сигнал ошибки "Число операндов равно числу операций. Пропущен операнд" 45, сдвинуть вправо на один разряд содержимое регистра 6 сдвинуть влево на один разряд

/ со 1ержимое регистра 6; выдать сигнал ошибки "Число 50 операций больше числа операндов. Пропущен операнд", выдать сигнал ошибки "Число операндов превышает число операций больше чем на единицу. 55

Пропущена операция".

Регистр 6 проверяет наличие и по рядок следования лексических единиц в исходном выражении и совместно с блоком микропрограммного управления осуществляет классификацию ошибок, Коммутатор 7 управляет передачами лексических единиц, а регистр 8 предназначен для хранения очередной лексической единицы в форме польской инверсной записи. Реверсивные регистры сдвига блока 3 памяти поразрядно сдвигают код операций и совместно с дешифратором 4 осуществляют сравнение приоритетов. Программируемая логическая матрица И 10 совместно с программируемой логической матрицей ИЛИ 11 и узлом 12 памяти организуют работу блока микропрограммного управления. Элемент ИЛИ 13 вырабаты вает сигнал Останов" устройства.

Генератор 14 тактовых импульсов совместно с триггером 15 и элементом И 17 организуют сигналы запуска устройства. Элемент 16 задержки предназначен для начальной установки узла памяти блока перед пуском устройства.

Группа 18 триггеров блока контроля образует четыре разряда реверсивного сдвигающего регистра, каждый из которых соответствует определенному клас5.у ошибок блока контроля. Группы 19 элементов ИЛИ совместно с группами элементов И организуют входные цепи реверсивного сдвигающего регистра таким образом, что начальная установка соответствует установке второго триггера (фиг.4) в единичное состояние, а остальных в нулевое.

Группа 21 триггеров реверсивного регистра сдвига блока памяти образует разряды реверсивного сдвигающего регистра. Группа 22 элементов ИЛИ совместно с группой 23 элементов И и элементом НЕ 24 организуют входные цепи .реверсивного сдвигающего регистра блока памяти таким образом, что начальная установка соответствует установке разряда, предшествующего старшему (фиг.5), в "О™. При этом элемент НЕ и связанные с ним элементы И образуют узел 25 записи разряда регистра 1, предназначенный для организации информационного входа реверсивного регистра сдвига блока памяти.

Устройство работает следующим образоМ.

Лексические единицы исходного выражения-последовательно поступают на

1290358

5 регистр 1, а затем на дешифратор 2 и на старший разряд блока 3 памяти, причем дешифратор разделяет их на операнды, операции, скобки открывающие, скобки закрывающие и конец выражения

Если очередная лексическая единица есть операнд, то дешифратор 2 запускает блок 5 микропрограммного управления, управляющие сигналы которого (микрокоманды у4, у, ) переключают коммутатор 7 на запись лексической единицы из регистра 1 в регистр 8, а также осуществляют сдвиг вправо на один разряд содержимого регистра 6.

Если содержимое четвертого разряда регистра 6 есть ноль, что означает отсутствие ошибки "Число операндов превышает число операций больше, чем на единицу", происходит переход к анализу следующей лексической единицы, Если же содержимое четвертого разряда регистра 6 есть единица, что соответствует наличию ошибки "Число операндов превышает число операций

25 больше, чем на единицу, Пропущена операция", блок 5 микропрограммного управления вырабатывает микрокоманды блокировки регистра 1 (у ) и выдачи сигнала ошибки (у, ) "Число операндов превышает число операций больше, чем на единицу. Пропущена операция", затем формируется "Останов", и процесс перевода прекращается.

Если очередная лексическая единица 35 есть открывающая скобка, дешифратор 2 лексических единиц запускает блок 5 микропрограммного управления, управляющие сигналы которого (микрокоманды у, у, ) записывают открывающую скобку из регистра 1 в старшие разряды регистров сдвига блока 3 памяти и блокируют регистр 1. Затем блок 5 микропрограммного управления вырабатывает управляющий сигнал (микроко- 45 манду у ), сдвигающий влево, содержимое регистров сдвига блока 3 памяти, а вслед за этим вырабатывается управляющий сигнал (микрокоманда у, ), раэблокирующий регистр 1, происходит пе- 50 реход к анализу следующей лексической единицы.

Если очередная лексическая единица есть операция, дешифратор 2 лексичес- 55 ких единиц запускает блок 5 микропрограммного управления, управляющие сигналы которого (микрокоманды у, y,, у<) записывают лексическую единицу (в данном случае операцию) из регистра 1 в. отаршие разряды регистров сдвига блока 3 памяти, сдвигают влево на один разряд содержимое регистра 6 сдвига, блокируют регистр 1.

Если содержимое первого разряда регистра 6 сдвига равно единице, блок 5 микропрограммного управления вырабатывает сигнал ошибки "Число операций больше числа операндов. Пропущен операнд", формируется "Останов", и процесс перевода прекращается. Если содержимое первого разряда регистра 6 сдвига равно нулю, дешифратор 4, на который поступает содержимое старших и предшествующих старшим разрядов регистров сдвига блока 3 памяти, формирует логический сигнал отношения приоритетов текущей и предшествующей операций. Если код операции, занесенный в старшие разряды регистров сдвига блока 3 памяти, имеет больший приоритет, чем код операции, занесенной в разряды, предшествующие старшим, дешифратор 4 запускает блок 5 микропрограммного управления, управляющий, сигнал которого сдвигает влево на один разряд содержимое ре-., гистров сдвига блока 3 памяти, затем разблокируется регистр 1, и происходит переход к анализу следующей лексической единицы. Если код операции, занесенный в старшие разряды регистров сдвига блока 3 памяти, меньше или равен коду операции, за несенной в предшествующие старшим разряды регистров сдвига блока 3 памяти, дешифратор 4 запускает блок 5 микропрограммного управления, управляющий сигнал которого (микрокоманда у ) переключает коммутатор 7 на запись содержимого из предшествующих старшим разрядов регистров сдвига блока 3 памяти в регистр 8. Затем блок 5 микропрограммного управления сдвигает на один разряд вправо (микрокоманды у8 ) содержимое регистров сдвига блока 3 памяти. Процедура разрешения переключения коммутатора 7 на запись содержимого предшествующих старшим разрядов регистров сдвига блока 3 памяти в регистр 8 и разрешения сдвига вправо содержимого регистров сдвига блока 3 памяти выполняется до тех пор, пока в предшествующих старшим разрядах регистров сдвига блока 3 памяти не будет находиться код операции с приоритетом меньшим, чем приоритет текущей операции.

1290358

Если очередная лексическая единица есть закрывающая скобка, дешифратор 2 запускает блок 5 микропрограммного управления, управляющие сигналы которого (микрокоманды у, у,) сдвигают вправо на один разряд содержимое регистров сдвига блока 3 памяти и блокируют регистр 1. Значение содер-. жимого старших разрядов регистров сдвигов блока 3 памяти. поступает на дешифратор 4. Если содержимое старших разрядов регистров сдвига блока 3 памяти есть код открывающей скобки, то дешифратор 4 запускает блок 5 микропрограммноro управления, управляющий сигнал которого (микрокоманды у ) сдвигает вправо содерВ жимое регистров сдвига блока 3 памяти, происходит разблокирование регистра 1 и переход к анализу следующей лексической единицы, т.е. закрывающая и первая из встретившихся открывающих скобок в регистр 8 не попадают. Если содержимое старших разрядов регистров сдвига блока 3 памяти не является кодом открывающей скобки, дешифратор 4 запускает блок 5 микропрограммного управления, управляющий сигнал которого (микрокоманда у ) переключает коммутатор 7 на запись содержимого старших разрядов регистров сдвига блока 3 памяти в регистр 8, сдвигает на один разряд вправо содержимое регистров сдвига блока 3 памяти. Дешифратор 4 определяет значение кода старших разрядов регистров сдвига блока 3 памяти.

Если зто значение есть код пустого символа, что означает отсутствие в исходном выражении символа открываю-. щей скобки, дешифратор 4 запускает блок 5 микропрограммного управления, управляющий сигнал которого (микрокоманда ущ ) формирует сигнал ошибки

"Отсутствует открывающая скобка", формирует "Останов, и процесс перевода прекращается. Если значение кода старших разрядов регистров сдвига .блока 3 памяти не является кодом пустого символа, дешифратор 4 определяет значение кода старших разрядов регистров сдвига блока 3 памяти, и процесс анализа на наличие в блоке памяти открывающей скобки продолжается до тех пор, пока не будет найдена открывающая скобка (что соответствует правильности исходного выражения), или обнаружен код пустого символа (что соответствует ошибке).

50

55 ших разрядов.регистров сдвига блока 3 памяти и запускает блок 5; Процесс повторяется до тех пор, пока не будет обнаружен код пустого символа или не будет обнаружен код открывающей скобки (что свидетельствует о наличии ( ошибки в исходном выражении) в старших разрядах регистров сдвига блока 3 памяти, определяемых дешифратором 4.

Если очередная лексическая единица не является ни операндом, ни опеЕсли очередная лексическая единица есть символ "Конец выражения", то дешифратор 2 запускает блок 5, управляющий сигнал которого (микрокоман5 да у,) блокирует регистр 1. Дешифратор 4 определяет значение кода стар- ших разрядов сдвига блока 3 памяти.

Если значение кода старших разрядов регистров сдвига блока 3 памяти есть

1р .код пустого символа, блок 5 анализирует значение содержимого третьего разряда регистра 6 сдвига. Если это значение равно единице, то блок 5 переключает коммутатор 7 на запись содержимого регистра 1 в регистр 8 (микрокоманда у ). Процесс перевода нормально завершен. Устройство готово к переводу следующего выражения. Если значение третьего разряда регистра

2р 6 сдвига равно нулю, то регистр 6 запускает блок 5 микропрограммного уп-, равления, формирует сигнал у, ошибки "Число операндов равно числу операций. Отсутствует операнд", выраба25 тывается "Останов", и процесс перевода прекращается. Если значение кода старших разрядов регистров сдвига блока 3 памяти отлично от кода пустого символа, дешифратор 4 запускает блок 5

3р микропрограммного управления, который анализирует значение выходного сигнала дешифратора 4. Если в старших разрядах регистров сдвига блока 3 памяти находится лексическая единица (скобка открывающая), то блок 5 микропрограммного управления вырабатывает сигнал у ошибки "Отсутствует закрывающая скобка" и осуществляет останов работы устройства. Если ошибка отсут4р ствует, то дешифратор 4 запускает блок 5, управляющий сигнал которого (микрокоманда у ) переключает коммутатор 7 на запись из старших разрядов регистров сдвига блока 3 памяти в ре45 гистр 8, и происходит сдвиг вправо на один разряд содержимого регистров сдвига блока 3 памяти. Затем дешифратор 4 определяет значение кода стар9 1290358 рацией, ни открывающей скобкой, ни к закрывающей скобкой, ни символом кон- с, ца выражения, то дешифратор 2 запус- к кает блок 5 микропрограммного управ- и ления, который формирует сигнал ошиб- 5 р ки Лексическая единица не принадлежит б алфавиту лексических единиц", блоки- р руется регистр 1, вырабатывается "Останов", и процесс перевода прекраэ щается, l0 с

Пример 1. Пусть входное! вы- к ражение имеет вид АхВ+С/ (D-Е), где и

";" используется как лексическая еди- ц ница "Конец выражения". в

Процесс перевода исходного выраже- 15 н ния в польскую инверсную запись заклю,чается в следующем. Производится начальная установка значений регистра 6 и блока 3 памяти, т.е. в регистр 6 заносится код 0100, в разря- 20 .э ды, предшествующие старшим разрядам регистров сдвига блока 3 памяти, заносится значение кода пустого симво- с ла. На регистр 1 поступает лексическая единица "А", которая определяет- 5 P ся дешифратором 2 как операнд, и с помощью блока 5 микропрограммного управления производится подключение входа коммутатора 7 на запись лексической единицы "А" из регистра 1 в 30 регистр 8, а также сдвиг вправо на один разряд содержимого регистра 6 (на регистре образуется код 0010).

Блок 5 микропрограммного управления анализирует значение четвертого разряда регистра 6. Так как оно равно нулю, производится переход к следующей лексической единице.

На регистр 1 поступает следующая лексическая единица "х", которая фиксируется дешифратором 2 как знак операции. Производится блокировка регистра 1. Из регистра 1 код "х" записывается в старшие разряды регистров сдвига блока 3 памяти. Осуществляется сдвиг влево на один разряд содержимого регистра 6, т,е. на указанном регистре образуется код

0100. При этом дешифратор 4 формирует значение отсутствия ошибки, так как значение первого разряда регистра 6 равно нулю. Значение кода "х", занесенное в старшие разряды регистров сдвига блока 3 памяти, и значение кода пустого символа„ которое находится в предшествующих старшим разрядах регистром сдвига блока 3 памяти, поступают на дешифратор 4, оторый формирует значение выходного игнала, по которому с помощью блоа 5 микропрограммного управления роизводится сдвиг влево на один разяд содержимого регистров сдвига лока 3 памяти. После этого регистр 1 азблокируется.

Следующая лексическая единица "В" аписывается в регистр 1 и дешифруетя как операнд. С помощью блока 5 оммутатор 7 подключается на запись з регистра 1, и лексическая единиа ."В" переписывается из регистра 1 регистр 8, происходит сдвиг вправо а один разряд содержимого региста 6 (на регистре образуется код

010). Производится переход к следующей лексической единице.

Очередная лексическая единица "+" аписывается в регистр 1 и определятся дешифратором 2 как операция, локируется регистр 1, осуществляется двиг на один разряд влево содержимого регистра 6, т.е. на укаэанном егистре образуетея код 0100. Так как значение первого разряда регист-. ра б сдвига равно нулю, дешифратор 4 формирует значение х„= О.

Из регистра 1 код "+" записывается в старшие разряды регистров сдвига блока 3 памяти. Значение кода "+", занесенное в старшие разряды регистров сдвига блока 3 памяти, и значение кода "х", занесенного в предшествующие старшим разряды регистров сдвига блока 3 памяти, поступают на дешифратор 4, который формирует значение выходного сигнала х = O так как приоритет предыдущей операции больше, рр чем последующей. С помощью блока 5 коммутатор 7 переключается на запись иэ предшествующих старшим разрядов регистров сдвига блока 3 памяти и производится запись содержимого этих 5 разрядов в регистр 8 (в данном случае лексической единицы "х"). Затем осуществляется сдвиг на один разряд вправо содержимого регистров сдвига блока 3 памяти и осуществляется заgp пись в старшие разряды регистров сдвига блока 3 памяти лексической единицы "+" с регистра 1. Значения старших и предшествующих старшим разрядов сдвига блока 3 памяти поступают на

55 дешифратор 4, который формирует вы ходной сигнал х,= 1, так как приоритет операции "+!!э код которой хранится в старших разрядах, больше приоритета пустого символа, хранимого в

1290358

l2 предшествующих старшим разрядах регистров блока 3 памяти. С помощью блока 5 производится сдвиг влево на один разряд содержимого регистров сдвига блока 3 памяти. После этого ре-5 гистр 1 разблокируется.

Следующая лексическая единица "С" записывается в регистр 1, определяется дешифратором 2 как операнд, и с помощью блока 5 производится переклю- 10 чение входа коммутатора 7 на запись операнда "С" в регистр 8, а также сдвиг вправо на один разряд содержимого регистра 6 (на регистре образуется код 0010). Так как значение четвер- 5 того разряда регистра 6 равно нулю, блок 5 переходит к управлению работой устройства к анализу следующей лексической единицы.

Очередная лексическая единица "/" 20 определяется дешифратором 2 как операция. Производится блокировка регистра 1. Из регистра 1 с помощью блока 5 код "/" записывается в старшие разряды регистров сдвига блока 3 памяти.

Осуществляется сдвиг влево на один разряд содержимого регистра 6 .(на регистре образуется код 0100). При этом дешифратор 4 формирует сигнал отсутствия ошибки. Значение кода "/", за- 30 несенного в старшие разряды регистров сдвига блока 3 памяти, и значение ко- да "+", занесенное ранее и находящееся в предшествующих старшим разрядах регистров сдвига блока 3 памяти, пос- 35 тупают на дешифратор 4, который формирует значение выходного сигнала х, = 1, по которому с помощью блока 5 производится сдвиг влево на один разряд содержимого регистров сдвига бло- 40 ка 3 памяти, после чего регистр 1 разблокируется.

Очередная логическая единица "С" записывается в регистр 1 и определяется дешифратором 2 как скобка от- 45 крывающая. С помощью блока 5 блокируется регистр 1, и значение кода "С" переписывается из регистра 1 в старшие разряды регистров сдвига блока 3 памяти. После этого осуществляется 50 сдвиг влево на один разряд содержимого регистров сдвига блока 3 памяти, регистр 1 разблокируется.

И tl

ОчеРедная лексическая единица Э принимается на регистр 1. Она является операндом. На регистре 6 образуется код 0010, и код Ъ" записывается в регистр 8, На регистр 1 принимается очередная лексическая единица "-", которая определяется дешифратором 2 как операция. Производится блокировка регистра 1, Код "-" из регистра 1 записывается в старшие разряды регистров сдвига блока 3 памяти. Осуществляется сдвиг влево на один разряд содержимого регистра 6 (на регистре образуется код 0100). При этом дешифратор 4 формирует сигнал отсутствия ошибки, а дешифратор .2, на который поступают значения старших разрядов (код "-") и предшествующих старшим разрядов (код "С") регистров сдвига блока 3 памяти, формирует выходной сигнал х,= 1, по которому с помощью блока 5 производится сдвиг влево на один разряд содержимого регистров сдвига блока 3 памяти. После этого регистр 1 разблокируется.

Очередная лексическая единица "Е" принимается на регистр 1. Она является операндом. На регистре 6 образуется код 0010, и код "Е" записывается в регистр 8.

На регистр 1 принимается следующая лексическая единица ")". Дешифратором 2 она определяется как скобка закрывающая. С помощью блока 5 осуществляется сдвиг на один разряд вправо содержимого регистров сдвига блока 3 памяти и блокируется ре-, гистр 1. Дешифратор формирует значение выходного сигнала х = О, так как в старших разрядах регистров сдвига блока 3 памяти находится код лексической единицы -" (т.е. код, отличный от открывающей скобки). С помощью блока 5 осуществляется переключение коммутатора 7 на запись из старших разрядов сдвига блока 3 памяти, и код лексической единицы "-," переписывается в регистр 8. Затем осуществляется сдвиг вправо на один разряд содержимого регистров сдвига блока 3 памяти.

Дешифратор 4 формирует значение выходного сигнала х = О, так как значения старших разрядов регистров сдвига блока 3 памяти не равны значению кода "Пустой символ", что означает наличие в блоке 3 памяти кодов операций и скобок, т.е. необходимость дальнейшего перевода с целью обнаружения окружающей скобки в блоке 3 памяти. Сигнал с выходом дешифратора 4 запускает блок 5 микропрограммного управления, который анализирует значение выходного сигнала и, так как

1290358 ния символов соответствует польской инверсной записи входного выражения.

Пример 2. Пусть входное выражение имеет вид А + В/ ;, т.е. содержит ошибку — отсутствие открывающей скобки.

Процесс перевода входного выражения и обнаружения ошибки заключается в следующем. На регистр 1 поступает лексическая единица "А", которая является операндом и переписывается в регистр 8. Очередная лексическая единица "+" поступает на регистр 1, дешифрируется как операция и записывается в старшие разряды регистров сдвига блока 3 памяти, после чего осуществляется сдвиг содержимого регистров блока 3 памяти на один разряд влево, так как значение выходного сигнала х дешифратора 4 равно

Разблокируется регистр 1.

На регистр 1 поступает лексическая единица "В", которая является операндом и переписывается в регистр 8.

Очередная лексическая единица ")" поступает на регистр 1, дешифрируется как скобка закрывающая. Блокируется регистр 1, и осуществляется сдвиг вправо на один разряд содержимого регистров сдвига блока 3 памяти. Дешифратор 4 формирует выходной сигнал х = О, так как в старших разрядах регистров сдвига блока 3 памяти не находится код открывающей скобки (там находится код лексической единицы "+") и запускает блок 5, который разрешает запись кода "+" из старших разрядов сдвига блока 3 памяти через коммутатор 7 в регистр 8, а затем разрешает сдвиг вправо на один разряд содержимого регистров сдвига блока 3 памяти. В старших разрядах регистров сдвига блока 3 памяти образуется код пустого символа. Дешифратор 4 формирует выходной сигнал х = 1, так как значение старших разрядов регистров сдвига блока 3 памяти равно коду пустого символа и запускает блок 5, который формирует сигнал ошибки "Отсутствует открывающая скобка" и формирует останов работы устройства.

Пример 3. Пусть входное выражение имеет вид АВ + ;, т.е. содержит ошибку — подряд идущие операнды с пропущенным знаком операции между ними. х = 1 (в старших разрядах регистров э сдвига блока 3 памяти находится код .открывающей скобки), блок 5 разрешает сдвиг вправо на один разряд содержимого регистров сдвига блока памяти. 5

При этом значение кода открывающей скобки, находившееся до сдвига в старших разрядах регистров сдвига блока

3 памяти, после сдвига теряется и в регистр 8 не попадает. Разблокирует - 10 ся регистр 1.

Таким образом, на регистр 1 посту- 55 пило выражение А х В + С / (D - E); а через регистр 8 на выход устройства выражение поступило в виде АВ х CDE— / + ; . Полученный порядок следоваПроцесс обнаружения ошибки заключается в следующем. Первая лексичесОчередная лексическая единица ";" записывается на регистр 1 и дешифри, руется как код конца выражения. Дешифратор 2 запускает блок 5, который блокирует регистр 1. Дешифратор 4 формирует значение выходного сигнала х = О, так как значение старших разрядов регистров сдвига блока 3 памяти 20 не равно коду пустого символа, а равно коду операции "/", и значение выходного сигнала х = О, так как значе8 ние старших разрядов регистров сдвига блока 3 памяти не равно значению кода 25 открывающей скобки, и запускает блок 5, который переключает коммутатор 7 на запись со старших разрядов регистров сдвига блока 3 памяти (лексическая единица "/" переписывается в регистр 8), а затем разрешает сдвиг вправо на один разряд содержимого регистров сдвига блока 3 памяти, и в . старшие разряды регистра сдвига блока 3 памяти попадает лексическая еди- 35 ница "+". Так как дешифратор 4 формирует значения выходных сигналов x =- 2

= О, x = О, аналогичным образом лекси;ческая единица "+" переписывается в регистр 8, и после сдвига в старших, <О разрядах регистров сдвига блока памяти образуется код пустого символа. В этом случае дешифратор 4 формирует значение выходного сигнала х = 1 и я запускает блок 5, который анализирует 45 значение третьего разряда регистра 6, а, так как значение последнего равно единице (отсутствие ошибки), блок 5 разрешает переключение коммутатора 7 на запись лексической единицы ";" иэ 50 регистра 1 в регистр 8. Устройство закончило перевод выражения и готово к приему следующего выражения.

1290358 15 кая единица "А" поступает на регистр 1. Дешифрируется как операнд.

Дешифратор 2 запускает блок 5, который записывает лексическую единицу

"А" регистра 1 в регистр 8 через коммутатор 7 и разрешает сдвиг вправо на один разряд содержимого-регистра 6, где после сдвига образуется код 0010 (при начальной установке был код

0100). Блок 5 анализирует значение IO старшего разряда регистра 6 и, так как зто значение равно нулю, производит переход к следующей лексической единице.

Очередная лексическая единица "В" 15 поступает на регистр 1. Она является операндом, с помощью блока 5 "В" переписывается в регистр 8, осуществляется сдвиг вправо на один разряд содержимого регистра 6, где образуется 20 код 0001. Блок 5 микропрограммного управления анализирует значение старшего разряда регистра 6 и, так как оно равно единице, выдает сигнал у, ошибки "Число операндов превышает 25 число операций больше чем на единицу.

Пропущена операция, блокирует регистр 1 и формирует останов работы устройства.

Пример 4. Пусть входное выра-30 жение имеет вид А + ХВ, т.е. содержит ошибку — пропущен операнд.

Процесс перевода и обнаружения ошибки заключается в следующем. Первая лексическая единица "A" есть. one- 35 ранд. Она переписывается,в регистр 8, на регистре 6 формируется код 0010.

Следующая лексическая единица "+" есть операция. Она записывается в блок 3 памяти, на регистре 6 форми- 40 руется код 0100. Очередная лексическая единица "х" есть операция. Она записывается в блок 3 памяти, блокируется регистр 1, и после сдвига влево на один разряд содержимого регист- 45 ра 6 на нем образуется код 1000.

Блок 5 анализирует значение первого разряда регистра 6 и, так как оно равно единице, выдает сигнал у< ошибки

"Число операций больше числа операн- 50 дов. Пропущен операнд" и формирует останов работы устройства.

16

Лексическая единица "А" переписывается в регистр 8. Лексическая единица "+" записывается в регистры сдвига блока 3 памяти, осуществляется сдвиг на один разряд вправо содержимого регистров сдвига блока 3 памяти.

Очередная лексическая единица дешифрируется как скобка закрывающая.

С помощью блока 5 блокируется регистр 1.и осуществляется сдвиг вправо на один разряд содержимого регистров сдвига блока 3 памяти, в результате чего в старших разрядах регистров сдвига блока 3 памяти образуется лексическая единица "+", которая записывается в регистр 8, и осуществляется сдвиг на один разряд вправо содержимого регистров сдвига блока 3 памяти, так как в старших разрядах регистров сдвига блока 3 памяти образуется код лексической единицы "(", и так как х = 1, осуществляется сдвиг вправо на один разряд содержимого регистров сдвига блока 3 памяти (значение кода "(" теряется) и производится переход к следующей лексической единице исходного выражения. .Очередная лексическая единица ";" дешифрируется как конец выражения.

Дешифратор 2 запускает блок 5, который блокирует регистр 1. Так как в старших разрядах регистров сдвига блока 3 памяти находится код лексической единицы "(" (вторая из скобок потеряна, так как была встречена закрывающая скобка, а первая из открывающих скобок присутствует в блоке 3 памяти), дешифратор 4 формирует значение выходного сигнала х = 0

2 и запускает блок 5, который анализирует значение выходного сигнала, формируемого дешифратором 4, а так как х = 1, блок 5 формирует сигнал у ошибки "Отсутствует закрывающая скобка" и формирует останов работы устройства.

Пропущенныи операнд будет обнаружен после исправления ошибки, связанной с отсутствием закрывающей скобки, при повторном переводе выражения в польскую инверсную запись.

Пример 5. Пусть исходное выражение имеет вид ((А +) ;, т.е.

:пропущена закрывающая скобка и операнд. Лексические единицы "(", "(" заносятся в регистры сдвига блока 3 па- мяти.

Формула изобретения

1. Устройство для преобразования выражений в польскую инверсную запись, содержащее дешифратор, первый регистр, 17 1290358 18 информационный вход которого является выход дешифратора соединен с входом информационным входом устройства, а признаков отношений приоритетов блока выход соединен с первым информацион- микропрограммного управления, выходы ным входом коммутатора, с информацион- микрокоманд которого, начиная с четным входом блока памя ти и с входом 5 вертого. соединены соответственно с

9 дешифратора лексических единиц, выход вторым и третьим управляющими входами которого соединен с входом признаков коммутатора, с входами сдвига влево лексических единиц блока микропрограм- и сдвига вправо блока памяти, с вхомного управления, первый выход микро- дами сдвига влево и сдвига вправо команд которого сое и единен с входом за- 10 реверсивного регистра сдвига и с устаписи первого регистра, второй выход новочными входами и блока памяти и ремикрокоманд соединен с первым управ- версивчого регистра сдвига, выходы ляю им входом коммутатора, третий вы- разрядов которого соединены с входом ход микрокоманд со единен с входом эа- признаков ошибки блока микропрограмписи блока памяти, второй регистР, много управления, выходы сигналов выход которого является информацион- ошибок которого являются соответственным выходом устроиства, в ход пуска но выходами сигналов ошибок устройстблока микропрограммного управления ва. является входом пуска устройства, отличающееся тем, что, 20

2 ° Устройство по п.1, о т л и— с целью повышения быстродействия и ч а ю щ е е с я тем, что блок памяти остоверности работы путем обеспечедосто р р содержит р ев ер сив ные р е гист ры сдв и га, ния контроля парности открывающей и входы сдвига влево, сдвига вправо, зазакрывающей скобок, принадлежности ия множест- писи и установочные входы которых явсимволов входного, выражения множестб ланса опера- ляются соответственно входами сдвига ву лексических единиц, аланса опер— торов и операц, о еспечения ий б спечения клас- влево, сдвига вправо, записи и установочным входом блока, входы старших сификации ошибок, в него введен реа причем ин- Разрядов регистров сдвига соединены версивный регистр сдвига, причем и— формационный выход и выход стар

ыход старшего ЗО с информационным входом блока, выходы разряда блока памяти соедине ь единены соот- старших разрядов регистров сдвига и инфор- выходы разрядов, предшествующих старветственно с вторым и третьим ин оршим являются соответственно выходом мационными входами коммутатора и с

r старшего разряда и инАормационным входами дешифратора„ выход коммутатора подключен к входу второго регистра,35 д

5 выходом блока.

1290358

Уф Уу ЯуУпУфу ®я kb

1290358

puz 5

Ф 6 ВНИИПИ Заказ 7905/49 Тираж 673 . Подписное

Произв.-полигр. пр-тие, г. Ужгород, ул. Проектная, 4