Динамическое запоминающее устройство с автономным контролем

Иллюстрации

Показать всеРеферат

Изобретение относится ..к области вычислительной техники и может быть использовано при создании оперативных запоминающих устройств в интегральном исполнении. Целью изобретения является повышение надежности устройства за счет обеспечения возможности автоматического поиска и замены неисправных элементов накопители средствами внутреннего тестирования. Устройство со ,держит накопитель 1, блок ассоциативной памяти 2, мультиплексоры 3,4,5,6, блок синхронизации 7, счетчики 8,9, триггер 10, блок кодирования 11, элемент И 12, блок коррекции 13, дешифратор 14, блок декодирования 15, элемент ИЛИ 16, таймер 17. Достоинством устройства является автоматический поиск и замена неисправных элементов накопителя при подключении питания к устройству . Это позволяет подключать к потребителю только те устройства, в которых нет деффектных элементов памяти . 1 ил. i (У) X л г

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (191 (И) (50 4 G 11 С 11 00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н A BTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3754981/24 — 24 (22) 18.06.84 (46) 15.02.87. Бюл. К - 6 (71) Московский инженерно-физический институт (72) A.Ñ.Áåðåçèí, Е.M.Îíèùåíêî и С.В.Сушко (53) 68 1.327.6 (088.8) (56) Патент ClllA У 4216541, кл. 371-38, опублик. 1982.

Патент США № 4380812, кл. 371-38, опублик. 1983. (54) ДИНАМИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОИСТВО С АВТОНОМНЫМ КОНТРОЛЕМ (57) Изобретение относится..к области .вычислительной техники и может быть использовано при создании оперативных запоминающих устройств в интегральном исполнении. Целью изобретения является повышение надежности устройства за счет обеспечения воэможности автоматического поиска и замены неисправных элементов накопителй средствами внутреннего тестирования. Устройство со,держит накопитель 1, блок ассоциативной памяти 2, мультиплексоры 3,4,5,6, блок синхронизации 7, счетчики 8,9, триггер 10, блок кодирования 1 1, элемент И 12, блок коррекции 13, дешифра-.ор 14, блок декодирования 15, элемент

ИЛИ 16, таймер 17. Достоинством устройства является автоматический поиск и замена неисправных элементов накопителя при подключении питания к устройству. Это позволяет подключать к потребителю только те устройства, в которых нет деффектных элементов памяти. 1 ил.

1290418

Изобретение относится к вычислительной технике, а именно к полупроводниковым запоминающим устройствам, и может быть использовано при изготовлении последних в интегральном испол- 5 нении.

Целью изобретения является повышение надежности работы запоминающего устройства.

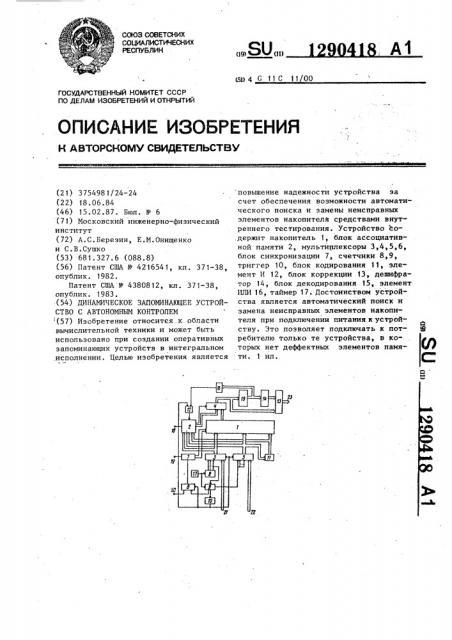

На чертеже показана блок-схема устройства.

Устройство содержит накопитель 1, блок 2 ассоциативной памяти, первый

3, второй 4, третий 5 и четвертый 6 мультиплексоры, блок 7 синхронизации, 15 основной счетчик 8, дополнительный счетчик 9, триггер-защелку 10, блок

11 кодирования, элемент И 12, блок

13 коррекции, дешифратор 14, блок 15 декодирования, элемент ИЛИ 16 таймер 20

17, управляющий выход 18, вход 19 выборки кристалла, вход 20 режима, адресные входы 21, информационные входы

22 и информационные выходы 23.

25 .Устройство работает следующим образом.

При подключении питания к устройству основной и дополнительный счетчики 8 и 9 устанавливаются в нулевые состояния, а триггер-защелка 10 — в

30 состояние " 1" (цепи начальной установки не показаны). Нахождение триггера-защелки 10 в состоянии " 1" ука-. зывает на работу запоминающего устройства с коррекцией ошибок в режиме 35 самотестирования, при котором цроисходит проверка работоспособности элементов памяти накопителя 1 тестом

"Последовательные запись/считывание

"0" и "1" 40

С второго выхода дополнительного счетчика -9.через третий мультиплексор

5 на входы информационных разрядов накопителя 1 поступают тестовые комбинации сигналов 00...0 или 11...1. 45

Если для блока 11 кодирования выбрать матрицу формирования контрольных раз-, рядов такую, что каждый контрольный разряд будет равен сумме по модулю 2, например, нечетного числа информаци" онных разрядов, то при указанных те стовых комбинациях информационных разрядов для контрольных разрядов также будет иметь место перебор значений "0" и " 1" . 55

В режиме, самотестирования основной счетчик 8 обеспечивает последовательный перебор слов накопителя 1, а дополнительный счетчик 9 — смену режимов записи и считывания и задание тестовой комбинации. Если в ходе самотестирования обнаружена ошибка (предполагается, что она вызвана дефектным элементом памяти накопителя 1), т.е. на выходах блока 15 декодирования присутствует ненулевая комбинация сигналов, текущий адрес слова запоминается в признаковой части блока 2 ассоциативной памяти. Занесение адресов дефектных элементов памяти в блок 2 ассоциативной памяти разрешается сигналом с элемента И 12 только в режиме самстестирования. В режиме внешних обращений совпадение внешнего адреса 21 и адреса, хранимого в признаковой части блока 2 ассоциативной памяти, инициирует запись (в режиме внешней записи) или считывание (в режиме внешнего считывания) из числовой части блока 2 ассоциативной памяти соответствующих информационных и контрольных разрядов.

Управляющий выход блока 2 ассоциа— тивной памяти используется для регистрации переполнения признаковой части; в этом случае запоминающее устройство признается негодным.

Цикл самотестирования завершается после проверки всех элементов памяти накопителя 1. При этом сигнал с выхода дополнительного счетчика 9 перебрасывает триггер-защелку 10 в состоf1 I I якие 0., которое переключает мультиплексоры .3, 5 и 6 на пропуск сигналов с внешних входов устройства.

Формула и з обретения

Динамическое запоминающее устройство с автономным контролем, содержащее накопитель, адресные и управляющие входы которого подключены соответственно к выходам первого мультиплексора и блока синхронизации, а входы контрольных разрядов соединены с выходами блока кодирования, таймер, выход которого подключен к входу основного счетчика, выходы которого соединены с входами первой группы первого мультиплексора, входы второй группы которого являются адресными входами устройства, дешифратор, входы которого подключены к выходам блока декодирования, а выходы соединены с ,входами первой группы блока коррекции, выходы которого являются инфор1290418

Составитель С.Сушко

Техред Л.Олейник Корректор А.Обручар

Редактор К.Волощук

Заказ 7910/52 Тираж 6ll Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 мационными выходами, а первый вход блока синхронизации — входом выборки кристалла устройства, о т л и ч а ю— щ е е с я тем, что, с целью повышения надежности устройства, в него введены блок ассоциативной памяти, второй, третий и четвертый мультиплексоры, дополнительный счетчик, триггер, элемент ИЛИ и элемент И, причем .входы элемента ИЛИ подключены к выхо- 10 дам блока декодирования., а выход соединен с первым входом элемента И, второй вход которого подключен к управляющим входам первого, третьего и четвертого мультиплексоров и к вы- 15 ходу триггера, вход которого соединен с третьим выходом дополнительного счетчика, первый и второй выходы которого подключены соответственно к первому информационному входу четвер- 20 того мультиплексора и к входам первой .группы третьего мультиплексора, а входы соединены соответственно с выходом таймера и одним из выходов основного счетчика, второй информационный вход четвертого мультиплексора является входом режима устройства, а выход подключен к второму входу блока синхронизации, выходы третьего мультиплексора соединены с входами информационных разрядов накопителя и с входами блока кодирования, а входы второй группы являются информацонными входами устройства, информационные входы первой, второй и третьей групп блока ассоциативной памяти подключены соответственно к выходам первого и третьего мультиплексоров и блока кодирования, управляющий вход соединен с выходом элемента И, первый управляющий выход является управляющим выходом устройства, а второй управляющий выход и информационные выходы блока ассоциативной памяти подключены соответственно к управляющему и к информационным входам первой группы второго мультиплексора, информационные входы второй группы которого соединены с выходами накопителя, а выходы йодключены к входам блока кодирования и к входам второй группы блока коррекции.