Буферное запоминающее устройство

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике, в частности к устройствам буферизации данных, и может быть использовано в системах обработки данных и в системах накопления и передачи информации. Цель изобретения - повьшение надежности буферного запоминающего устройства. Устройство содержит управляющий вход ,1, блок 2 управления, счетчик 3 адресов , блок 4 управления, счетчик 5 адресов, накопитель 6, блок 7 ввода данных, блок 8 вывода данных Устройство работает в двух режимах ;. зада ваемых блоком 2. Первый режим Обеспечивает приоритетную запись данных в накопитель 6 и многократное считывание в разрешенные моменты времени . Второй режим обеспечивает приоритетную запись данных в накопитель 6 и однократное считывание массива данньрс, объем которого определяется значениями счетчиков 3 и 5 адресов, Блок 4 управления организует работу, накопителя 6 в режиме записи и считывания и синхронизирует работу блоков 7 и 8 ввода и вывода данных и счетчиков 3 и 5 адресов. Кроме того, блок 4 осуществляет подключение выходо счетчиков 3 и 5 к адресным входам накопителя 6. 3 ил. i W ю со

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН

А1 (19) (11) цд 4 G 11 С 19/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

M А BTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТ8ЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3917221/24-24 (22) 25.06.85, (46) 15.02.87. Бюл. Р 6 (72) С.В.Тюрин (53) 681.327.6(ОР8.8) (56) Авторское свидетельство СССР

Р 624231, кл. С 06 F 13/02, 1977.

Патент Японии Р 51-30982, кл. G 06 F 13/00, 1976. (54) БУФЕРНОЕ ЗАПОИИНАЮЩЕЕ УСТРОЙСТВО (57) Изобретение относится к вычислительной технике, в частности к устройствам буферизации данных, и может быть использовано в системах обработки данных и в системах накопления и передачи информации. Цель изобретения.- повышение надежности буферного запоминающего устройства.

Устройство содержит управляющий вход ,1, блок 2 управления, счетчик 3 адресов, блок 4 управления, счетчик 5 адресов, накопитель 6, блок 7 ввода данных, блок 8 вывода данных. Устройство работает в двух режимах ..задаваемых блоком 2. Первый режим обеспечивает приоритетную запись данных в накопитель 6 и многократное считывание в разрешенные моменты времени. Второй режим обеспечивает приоритетную запись данных в накопитель 6 и однократное считывание массива данных, объем которого определяется

"значениями счетчиков 3 и 5 адресов.

Блок 4 управления организует работу, накопителя 6 в режиме записи и считывания и синхронизирует работу бло- m ков 7 и 8 ввода и вывода данных и счетчиков 3 и 5 адресов. Кроме того, блок 4 осуществляет подключение выходов счетчиков 3 и 5 к адресным вхо- ъ дам накопителя 6. 3 ил.

1290423

Изобретение относится к вычислительной технике, в частности к устройствам буферизации данных, и может быть использовано в системах обработки. данных, а также в системах накопления и передачи информации.

Цель изобретения — повышение надежности устройства.

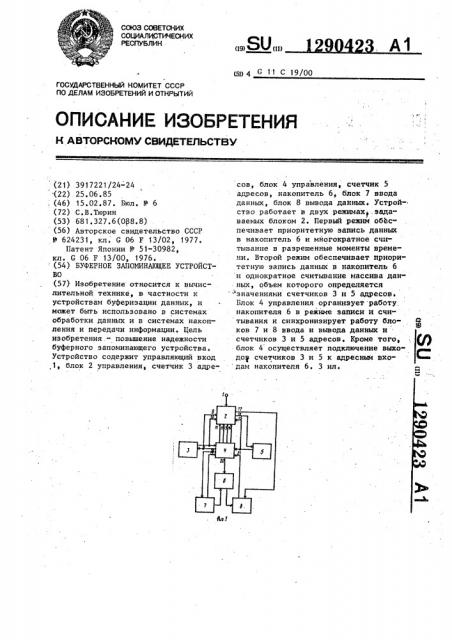

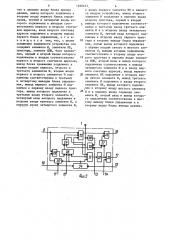

На фиг. 1 приведена структурная схема устройства; на фиг. 2 и 3 структурные схемы блоков управления.

Буферное запоминающее устройство содержит управляющий вход 1, блок 2 управления, счетчик 3 адресов, блок

4 управления, счетчик 5 адресов, накопитель 6, блок 7 ввода данных, блок 8 вывода данных, входы 9 — 15 блока 2 управления, выходы 16 и 17 блока 2 управления, выход 18, вход

19, адресные выходы 20, вход 21 блока 4 управления.

Блок 2 управления (фиг. 2) содержит элемент И 22, элемент ИЛИ 23, триггер 24, элемент И 25, элемент НЕ

26, элементы И 27 и 28, триггер 29, элементы И 30 и 31, элемент НЕ 32, элемент И 33 и блок 34 сравнения.

Блок 4 управления (фиг. 3) содержит мультиплексор 35, элементы

И 36-39, триггеры 40 и 4 1, генера:тор 42 импульсов, распределитель 43 импульсов.

Блок 2 управления предназначен для включения одного из двух режимов работы буферного запоминающего устройства, выбор которого определяется; управляющим потенциалом, поступающим на вход 1. Первый режим работы обеспечивает приоритетную запись информации в накопитель 6 и многократное ее считывание в разрешенные моменты времени. Во втором режиме обеспечивается также приоритетная запись информации в накопитель 6, но с однократным считыванием массива информации, объем которого определяется разницей содержимого. счетчиков 3 и 5 адресов. Счетчик 3 адресов предназначен для формирования адреса ячеек накопителя 6, в которые осуществляется запись информации.

Счетчик 5 адресов предназначен для формирования адреса ячеек накопителя 6, из которых информация считывается. Блок 4 управления предназначен для выбора режима записи или считывания информации для синхронизации работы блоков ввода и вывода данных, а также обеспечивает соот10 ветствующее подключение выходов счет чиков 3 и 5 адресов к адресным входам накопителя 6. Накопитель 6 предназначен для временного запоминания и хранения информации.

Устройство работает следующим образом.

Если на вход 1 буферного запоминающего устройства поступает низкий управляющий потенциал, то реализуется первый режим работы устройства.

При этом в блоке 4 управления с помощью генератора 42 импульсов и трехтактного распределителя 43 импульсов цикл:-чески формируются три, неперекрывающихся во времени управляющих импульса, Первым по време ни управляющим импульсом осуществляется циклический опрос состояний блока 7 ввода данных и блока 8 вывода данных, в результате чего триггеры 40 и 41 устанавливаются в одинаковые состояния. При единичном состоянии триггера 40 реализуется этап записи информации, а при нулевом его состоянии и единичном состоянии триггера 41 — этап считыва ния информации.

При реализации режима записи открывается соответствующий вход мультиплексора 35, в результате чего выход счетчика 3 подключается к адресному входу накопителя 6 ° В то же время открываются элементы И 38 и 36, чем обеспечивается прохождение второго и третьего управляющих импульсов, формируемых распределителем 43 импульсов, соответственно на входы блока 7 и счетчика 3. По

40 второму управляющему импульсу, формируемому элементом И 38, блок 7 ввода данных обеспечивает выдачу в накопитель 6 записываемой информации и сигнала записи. По третьему управляющему импульсу, формируемому элементом И 36, осуществляется наращивание на единицу счетчика 3 адресов. В случае отсутствия информации, подлежащей вводу в буферное за50 поминающее устройство, на первом выходе блока 7 устанавливается низкий потенциал, в результате чего триггер 40 переключается в нулевое состояние. Этим разрешается реализация режима многократного считывания информации. В этом случае через мультиплексор 35 адресный вход накопителя 6 подключается к выходу счетчика 5 адресов. В то же время

1290423

40 разрешается прохождение второго и третьего управляющих импульсов соответственно через элементы И 39 и 37, если только блок 8 вывода данных готов принять информацию, о чем свидетельствует наличие высокого потенциала на выходе блока 8 и, соответственно, на выходе триггера 41. Управляющий импульс с выхода элемента И 39 проходит через элемент ИЛИ 33 и пос- 10 тупает на вход блока 8 вывода данных для стробирования считываемой из накопителя 6 информации. Импульс с выхода элемента И 37, пройдя через открытый элемент И 27 и элемент ИЛИ 23, 15 поступает на вход счетчика 5 адресов и автоматически наращивает его содержимое на единицу. Режим считывания продолжается до тех пор, пока не возобновится режим записи, либо не 2О появится низкий потенциал на выходе блока 8 вывода данных, либо не переключится режим работы буферного запоминающего устройства при режиме считывания информации. 25

Если на вход 1 буферного запоминающего устройства поступает высокий потенциал, то реализуется второй режим работы, который отличается от первого однократной выдачей записан- 30 ного в накопитель 6 массива информации. В данном режиме блок 4 управления работает так же, как.и в первом режиме.

Блок 2 управления работает следую- 35 щим образом.

При записи информации блок 34 сравнения осуществляет текущее сравнение содержимого счетчиков 3 и 5 адресов. Если сравнения кодов не происходит (что указывает на то, что массив записываемой информации меньше максимального объема накопителя 6), то элемент И 28 не открывается и триггер 24 остается в нулевом состоянии, чем запрещается ,прохождение третьего управляющего импульса через элемент И 22 и элемент ИЛИ 23 на вход счетчика 5.

Если при записи информации на выходе блока 34 сравнения появляется сигнал (что означает переполнение емкости накопителя 6), то с этого момента третьим управляющим импульсом, поступающим с выхода элемента И 36 на вход элемента И 22 осуществляется синхронное наращивание содержимого счетчиков 3 и 5. Это обеспечивает равенство их содержимого вплоть до окончания записи информации, как бы ее объем не соотносился с максимальным объемом накопителя 6.

На этапе считывания информации, когда триггер 24 находится в нулевом состоянии (т.е. когда факт переполнения на этапе записи не был зафиксирова,н), объем считываемой информации определяется разницей содержимого счетчиков 3 и 5. Как только содержимое счетчика 5 становится . равным содержимому счетчика 3, элемент И 31 вырабатывает управляющий потенциал, который, пройдя через элемент НЕ 32, запрещает прохождение второго и третьего управляющих импульсов соответственно через элементы И 33 и 27, чем и обеспечивается .однократное считывание записанного массива информации. При этом триггер 24 устанавливается в нулевое состояние сигналом с выхода элемента И 30. Этим исключается ложное срабатывание триггера 24 при возобновлении этапа записи очередного массива информации, так как в этот момент начальные состояния счетчиков 3 и 5 оказываются одинаковыми.

В случае, когда триггер 24 находится в единичном состоянии (что сигнализирует о необходимости однократного считывания максимально возможного объема информации, равного объему накопителя 6), элемент И 3 1 закрыт сигналом с нулевого выхода . триггера 24. Это обеспечивает прохождение второго и третьего управляющих импульсов через элементы И

33 и 27 в случае первоначального равенства содержимого счетчиков 5 и 3, после чего триггер 24 устанавливается в нулевое состояние и даль" нейшая работа блока 2 управлЕния не отличается от описанной.

Формула изобретения

Буферное запоминающее устройство, содержащее накопитель, адресные входы которого подключены к соответствующим выходам первого блока управления первый выход первого блока управления подключен к входу блока ввода данных, первый и второй выходы которого подключены соответственно к первому входу первого блока управления и к информационному входу накопителя, выход которого подклю"

12 чен к первому входу блока вывода данных, выход которого подключен к второму входу первого блока управления, третий и четвертый входы которого подключены к выходам соответственно первого и второго счетчиков адресов, вход второго счетчика адресов подключен к второму выходу первого блока управления, о т л ич а ю щ е е с я тем, что, с целью повышения надежности устройства оно содержит элементы И, элементы НЕ, триггеры, элемент ИЛИ, блок сравнения, первый и второй входы которого подключены к входам соответственно первого и второго счетчиков адресов, выход блока сравнения подключен к первым входам первого, второго и третьего элементов И, вторые входы первого и второго элементов И подключены соответственно к третьему и четвертому выходам блока управления, выход первого элемента И подключен к первому входу первого триггера, выход -которого подключен к третьему входу второго элемента И, четвертый вход которого подключен к второму входу третьего элемента И, к первому входу четвертого элемента И, 90423 6 к входу первого элемента HE и является входом устройства, выход второго элемента И подключен к первому входу второго триггера, первый и второй

5 выходы которого подключены соответственно к третьему входу третьего элемента И и к второму входу четвертого элемента И, третий вход которого подключен .к второму входу первого триг10 гера и второму выходу блока управления, пятый выход которого подключен к первым входам пятого и шестого элементов iH выходы которых подключены соответственно к второму входу вто15 рого триггера и первому входу элемента ИЛИ, второй вход и выход которого подключены соответственно к выходу четвертого элемента И и к входу первого счетчика адресов, выход первого

20 элемента НЕ подключен к второму входу пятого элемента И, выход третьего элемента И подключен к входу второго, элемента НЕ, выход которого подклю,чен к второму входу шестого элемента

25 И и к первому входу седьмого элемента И, второй вход и выход которого подключены соответственно к шестому выходу блока управления и к второму входу блока вывода данных.

Фиг.

1290423

Составитель С. Шустенко

Редактор К. Волощук Техред Д.Олейник Корректор Л. Пилипенко.

Закаэ 7910/52 Тираж 611 Подписное

ВНИИПИ Государственйого комитета СССР по делам изобретений.и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно"полиграфическое предприятие, г. Ужгород, ул. Проектная, 4