Программируемый делитель частоты

Иллюстрации

Показать всеРеферат

Изобретение относится к импульсной технике. Может быть использовано, в системах автоматики в качестве делителя частоты на любой вещественный /v/yyv/v / V/ °F коэффициент деления, в устройствах синхронизации, а также в цифровых синтезаторах частоты. Цель изобретв : НИН - упрощение устройства при сохранении быстродействия и диапазона коэффициентов деления. Для достижения поставленной цели введен блок вычитания импульса 1, образованы новые функциональные связи. того, устройство содержит делитель 2 частоты с переменным коэффициентом деления , элемент 3 сравнения кодов, счетчик 4 импульсов, шины 5 опорной частоты, 6 и 7 кодов, вЪкодну 8. Блок i содержит триггер, три элемента И. 2 ил. . /V / ffk. CD о сл

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН

ОИ А1 (19) (И) (51) 4 Н 03 К 23/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ABTOPGHOMV СВИДЕТЕЛЬСТВУ

1

4 ь

Ю

ГОСУДАРСТ8ЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) .3864677/24-21 (22) 11.03.85 (46) 15.02.87. Вюл № 6 (72) В.Д.Остриков (53) 621.374.3 (088.8) (56) Авторское свидетельство СССР

¹ 1058066, кл. Н 03 К 23/00, 1982.

Авторское свидетельство СССР ¹- 1051729, кл. Н 03 К 23/00, 1981. (54) ПРОГРАММИРУЕМЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ (57) Изобретение относится к импульсной технике. Может быть использовано. в системах автоматики в качестве делителя частоты на любой вешественный коэффициент деления, в устройствах синхронизации, а также в цифровых синтезаторах частоты. Цель изобрете- . ния — упрощение устройства при сохранении быстродействия и диапазона коэффициентов деления. Для достижения поставленной цели введен блок вычитания импульса 1, образованы новые функциональные связи. Кроме того, устройство содержит делитель 2 частоты с переменным коэффициентом деления, элемент 3 сравнения кодов, счетчик 4 импульсов, шины 5 опорной частоты, 6 и 7 кодов, выходную 8.

Блок 1 содержит триггер, три элемента И. 2 ил..

129G515

N о где

Изобретение относиТся к импульсной технике и может быть использовано в системах автоматики в качестве делителя частоты на любой вещественный коэффициент деления, в устройствах синхронизации, а также в цифровых синтезаторах частоты.

Цель изобретения " повышение на дежности устройства при сохранении быстродействия и диапазона коэффициентов деления.

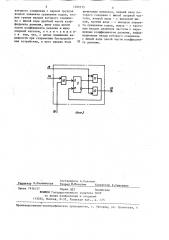

На фиг. 1 приведена электрическая структурная схема программируе- мого делителя частоты; на фиг. 2— электрическая функциональная схема блока вычитания импульса.

Программируемый делитель частоты содержит блок 1 вычитания импульса, делитель 2 частоты с переменным коэффициентом деления, элемент 3 сравнения кодов, счетчик 4 импульсов, шину 5 опорной частоты, шины о и 7 кодов соответственно дробной и целой частей коэффициентов деления и выходную шину 8, при этом шина 5 опорной частоты соединена с первым входом блока 1 вычитания импульса.

Выход блока 1 вычитания импульса соединен с тактовым входом делителя 2 частоты с переменным коэффициентом деления. Шина 7 кода целой части коэффициента деления соединена с ийформационными входами делителя 2 частоты с переменным коэффициентом деления. Выход делителя 2 частоты с переменным коэффициентом деления соединен с выходной шиной 8, вторым входом блока 1 вычитания импульса и входом счетчика 4 импульсов. Выхо- ды счетчика 4 импульсов соединены с первой группой входов элемента 3 сравнения кодов. Шина б кода дробной части коэффициента деления соединена с второй группой входов элемента 3 сравнения кодов, выход которого соединен с третьим входом блоха 1 вычитания импульса.. Блок 1 вычитания импульса предназ.начен для выработки выходной частоты

F,.значение которой приближено к величине опорной частотыР, а о число импульсов определяется соотношением:

М, если Т = О; о

И вЂ” 1, если Т О, 0 где N — число импульсов опорной с, частоты:F,.

2 — число импульсов выходной частоты F

Т, - состояние триггера 9 блока 1 вычитания импульса

5 (см. фиг. 2) .

Блок 1 вычитания импульса 1 содержит триггер 9, первый 10, второй 11 и третий 12 элементы И, первый 13, второй 14 и третий 15 входы и выход

® 16. Первый вход 13 опорной частоты соединен с первыми входами элементов И 11 и 12;управляющий и разрешающий входы 14 и 15 соединены соответственно с первым и вторым входами элемента И 10. Выход элемента И 10 соединен с установочным входом единицы триггера 9. Единичный и нулевой выходы триггера 9 соединены с вторыми входами элементов И 11 и 12 соответственно. Выход второго элемента

И 11 соединен с установочным входом нуля триггера 9. Выход элемента И 12 является выходом 16 блока 1, 25

Программируема делитель частоты работает следующим образом.

За исходное состояние программируемого делителя частоты принимают состояние, при котором триггер 9 блока 1 находится в нулевом состоянии, в делителе 2 находится (двоичный) код целой части коэффициента деления ч

Импульсы входной частоты,, поступающие с шины 5, через элемент 12

35 блока 1 поступают на тактовый вход целителя 2. Формирование выходного импульса F, делителя 2 осуществляется в соответствии с выражением:

40 Т = Т 1„,, Т, — период следования входной частоты Р (на шине 5);

N„— код целой части коэффициента деления (на шине 7) Импульсы с частотой Г, с выхода делителя 2 поступают на вход счетчика 4 и на второй вход блока

Если сумма кода на выходах счетчика 4 и кода дробной части коэффициента деления Nä4 присутствующего на шине 6, больше величины К, то на выходе элемента 3 присутствует высокий потенциал, разрещающий прохождение через элемент 10 выходного импульса делителя 2 на единичный вход триггера 9 блока 1. Выходной импульс Г делителя 2 осуществляет

3 12 в этом случае установку триггера 9 в единичное состояние. Высокий потенциал единичного выхода триггера

9 запрещает прохождение через элемент t2 очередного импульса опорной частоты F на тактовый вход део лителя 2 и разрешает прохождение через элемент 12 импульса опорной частоты F, который устанавливает о триггер 9 в нулевое состояние. Таким образом, в случае установления триггера 9 в единичное состояние выходной импульс делителя 2 формируется спустя время

Т Т (N + 1).

Если сумма кода на выходах счет чика 4 и кода дробной части коэффициента деления NA меньше или равна 4 величине К, то на выходе элемента 3 присутствует низкий потенциал, запрещающий прохождению через элемент 10 выходного импульса F деЯ. лителя 2 на единичный вход триггера 9..В этом случае выходной импульс делителя 2 формируется с периодом Т

Таким образом, программируемый делитель частоты осуществляет деление опорной частоты F, определяемой выражением: (N + 1), если N

Т. = 2 То Бц4, если М > Ид,, 30

\ a,gS °

8и (e.î. по Квайну);

QanPeAg змее.

Q,„„„g

20и (е.о. по Квайну).;

9С515 ройства в исхоцное состояние определяется формулой: ьт Т Т 1

Т N Т N (N + 1) Т N

Быстродействие программируемого делителя частоты складывается из быстродействия функциональных устройств и. определяется .выражением:

50 пд 2 лэ р ан ф, ttã где t„, t, — время задержки логического элемента и триггера соответствен15 но; — время. распространения сигнала от входа до выхода делителя 2.

Объем аппаратурных затрат уст20 ройства определяется формулой: л„„.,„„,=)::

1=1 где Q, — аппаратуриые затраты

i-ro элемента устройства.

25, Аппаратурные затраты i-го элемента данного устройства соответственно определены выражениями:

О

Qgоредп <1и б где Н1- текущий код счетчика 4. .Среднее значение периода следования выходной частоты F программируемого делителя частоты, определяемое как математическая средняя величина периодов за время возврата устройства в исходное состояние

Т = КТ, определяется выражением„ зоэв

Т = Т (И 4+ - ), N а среднее значение выходной частоты Г определяется формулой:

1

Е р и р о Я

К где N„ — код целой части, коэффициента деления;

N„„ — код дробной части коэффи- циента деления;

К вЂ” коэфиициент пересчета счетчика 4.

Неравномерность формирования выходной частоты программируемого делителя частоты за время возврата уст tflPPAA. Тi Q R3

Формула изобретенимПрограммируемый делитель частоты, содержащий делитель частоты с переменным коэффициентом деления, выход которого соединен с выходной шиной и входом счетчика импульсов, выходы

0 +Q атеней 4 % ° . шпеер,л 1пеем Qg S ° где Q. — объем аппаратурных зат1 рат i-го элемента предлагаемого устройства;

Q; — объем аппаратурных затрат >-го элемента известного устройства; п — разрядность схемы сравнения предлагаемого устройства и сумматора известного устройства;

Q»- айпаратурные затраты, определяемые в единицах оборудования, соответственно триггера и логического элемента.

1290515

Составитель А.Соколов

Редактор Л.Пчолинская Техред И.Попович Корректор E С тор . ирохман

Заказ 791б/57 Тираж 9 2 Подпис ное

ВНИИПИ Государственнога комитета СССР по делам изобретений и открытий

113035, Москва, И-35, Раушская наб., д. 4 /5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 которого соединены с первой группой входов элемента сравнения кодов, вторая группа входов которого соединена с шиной кода дробной части коэффициента деления, шину кода целой 5 части коэффициента деления и шину опорной частоты, о т л и ч а ю щ и йс я тем, что, с целью повышения надежности при сохранении быстродействия устройства, в него введен блок вычитания импульса, первый вход которого соединен с шиной опорной частоты, второй вход — с выходной шиной, третий вход — с выходом элемента сравнения кодов, выход — с тактовым входом делителя частоты с переменным коэффициентом деления, информационные входы которого соединены с шиной кода целой части коэффициента деления.