Система передачи цифровой информации

Иллюстрации

Показать всеРеферат

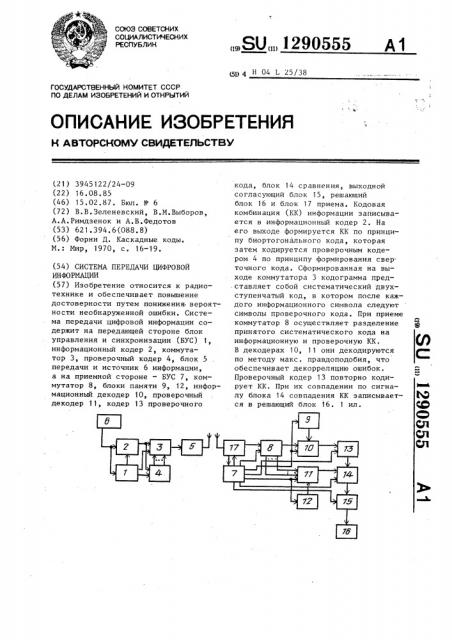

Изобретение относится к радиотехнике и обеспечивает повышение достоверности путем понижения вероятности необнаруженной ошибки. Система передачи цифровой информации содержит на передающей стороне блок управления и синхронизации (БУС) 1, информационный кодер 2, коммутатор 3, проверочный кодер 4, блок 5 . передачи и источник 6 информации, а на приемной стороне - БУС 7, коммутатор 8, блоки памяти 9, 12, информационньй декодер 10, проверочный декодер 11, кодер 13 проверочного кода, блок 14 сравнения, выходной согласующий блок 15, решающий блок 16 и блок 17 приема. Кодовая комбинация (КК) информации записывается в информационный кодер 2. На его выходе формируется КК по принципу биортогонального кода, которая затем кодируется проверочным кодером 4 по принципу формирования сверточного кода. Сформированная на выходе коммутатора 3 кодограмма пред- .ставляет собой систематический двухступенчатый код, в котором после каждЬго информационного символа следуют символы проверочного кода. При приеме коммутатор 8 осуществляет разделение принятого систематического кода на информационную и проверочную КК. В декодерах 10, 1 Г они декодируются по методу макс, правдоподобия, что обеспечивает декорреляцию ошибок. Проверочный кодер 13 повторно кодирует КК. При их совпадении по сигналу блока 14 совпадения КК записывается в решающий блок 16. 1 шт. (Л 1C со о СП ел ел

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

Ц1) 4 Н 04 L 25/38

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ABTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3945122/24-09 (22) 16.08.85 (46) 15.02.87. Бюл. № 6 (72) В.В.Зеленевский, В.M.Âûáoðoâ, А.А.Римдзенок и А.В.Федотов (53) 621.394.6(088.8) (56) Форин Д. Каскадные коды.

M.: Мир, 1970, с. 16-19. (54) СИСТЕМА ПЕРЕДАЧИ ЦИФРОВОЙ

ИНФОРМАЦИИ (57) Изобретение относится к радиотехнике и обеспечивает повышение достоверности путем понижения: вероятности необнаруженной ошибки. Система передачи цифровой информации содержит на передающей стороне блок управления и синхронизации (БУС) 1, информационный кодер 2, коммутатор 3, проверочный кодер 4, блок 5 передачи и источник 6 информации, а на приемной стороне — ЬУС 7, коммутатор 8, блоки памяти 9, 12, информационный декодер 10, проверочный декодер 11, кодер 13 проверочного

„„Я0„„1290555 А1 кода, блок 14 сравнения, выходной согласующий блок 15, решающий блок 16 и блок 17 приема. Кодовая комбинация (КК) информации записывается в информационный кодер 2. На

его выходе формируется КК по принципу биортогонального кода, которая затем кодируется проверочным кодером 4 по принципу формирования сверточного кода. Сформированная на выходе коммутатора 3 кодограмма пред.ставляет собой систематический двухступенчатый код, в котором после каждого информационного символа следуют символы проверочного кода. При приеме коммутатор 8 осуществляет разделение принятого систематического кода на информационную и проверочную КК.

В декодерах 10, 11 они декодируются по методу макс. правдоподобия, что обеспечивает декорреляцию ошибок.

Проверочный кодер 13 повторно кодирует КК. При их совпадении по сигналу блока 14 совпадения КК записывается в решающий блок 16. 1 ил.

1 1290555 2 ние относится к радиотех- управляемый блоком 7 управления и синт быть использовано в сис- хронизации, осуществляет разделение ачи информации. систематического кода на информационбретения — повышение до- ную и проверочную кодовую комбинацию, путем понижения вероят- 1 которые затем декодируются декодерааруженной ошибки. ми 10 и 11 по методу максимального же изображена структурная правдоподобия, на входы декодеров 10 ая схема предлагаемой и 11 подаются опорные комбинации ин-. формационного и проверочного кодов передачи цифровой информа- 10 из блоков 9 и 12 памяти, что обеспечит на передающей стороне вает декорреляцию ошибок. С выхода

"вления и синхронизации, декодера 10 правильно принятая кодоный кодер 2, коммутатор 3 вая комбинация (или с необнаруженныкодер 4 блок 5 передачи ми ошибками) поступает на кодер 13

У 15 информации, а на приемной пРовеРочного кода и записывается в лок 7 управления и синхро выходной согласующий блок 15, Повторммутатор 8 первый блок 9 но закодированная комбинация провеЭ .ормационный декодер 10 рочным кодером 13, аналогичным nepet декодер 11, второи бло дающей стоРоне, постУпает на третий кодер 13 проверочног 20 вход блока 14 сРавнениЯ, на пеРвый сравнения, выходной со- вход которой постУпает пРавильно принятая (или с необнаруженными ошибками) комбинация проверочного кода с выхода проверочного декодера 11. При совпадении комбинаций работает следующим образом.25 комбинация, поступающая на выходе блока 14 сравнения формиа 6 информации на входы руется разрешающий потенциал, котоавления и синхронизации, рый поступает в выходной согласуюго, а затем записывается щий блок 15 и разрешает выдачу запионный кодер 2. Блок 1 санной в последнем ИКК в решающий и синхронизации обеспечиблок 16. На выходе блока 14 сравнеение работой информационния может быть получен разрешающий

2, а также управление потенциал, если на схему сравнения утатора 3 и проверочного поступили одинаковые кодовые комбиким образом, что на выходе 35 нации.

110001 i 11

Изобрете нике и може темах перед

Цель изо стоверности ности необн

На черте электрическ системы.

Система ции содержи

7 блок 1 упр информацион проверочный источник 6 стороне — б низации, ко памяти, инА проверочныи

12 памяти, да, блок 14 гласующий блок 17 при

Система

Кодовая от источник блока 1 упр запускает е в информаци управления вает управл ного кодера работой комм кодера 4 та информационного кодера 2 формируется кодовая комбинация по принципу биортогонального кода, которая затем ко- дируется проверочным кодером 4 по принципу формирования сверочного ко- 40 да, и с его выходов (их может быть п) через коммутатор 3 сформированная кодограмма поступает на вход блока 5 передачи, Кодограмма представляет собой систематический двухступенчатый 45 код, в котором после каждого информационного символа следуют символы проверочного кода, например символы информационного кода 50 символы проверочного кода.

Полученная таким образом кодовая комбинация через блок 5 передачи поступает в линию связи, где подвергается воздействию помех.

Блок 17 приема выделяет искаженную помехами комбинацию, а коммутатор 8, формулаизобретения

Система передачи цифровой информации, содержащая на передающей стороне источник информации, выход которого соединен с первым входом информационного кодера, выход которого подключен к первому входу проверочного кодера, и блок передачи, а на приемной стороне — блок приема, информационный декодер, проверочный декодер и выходной согласующий блок, выход которого соединен с входом решающего блока, о т л и ч а ю щ а яс я тем, что, с целью повышения достоверности путем понижения вероятности необнаруженной ошибки, на передающей стороне введены коммутатор и блок управления и синхронизации, вход которого подключен к первому входу информационного кодера, второй вход которого соединен с первым выходом блока управления и син1290555

Составитель О. Геллер

Техред И. Попович Корректор E - Сирохман

Редактор В.Ковтун

Заказ 7918/59 Тираж 660 Поцписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.ужгород, ул.Проектная, 4 хронизации, второй выход которого подключен к первому входу коммутатора, второй вход которого соединен с первым входом проверочного кодера, второй вход которого подключен к 5 третьему выходу блока управления и синхронизации, при этом выходы проверочного кодера подключены к третьим входам коммутатора, выход которого соединен с входом блока передачи, а на приемной стороне введены блок сравнения, кодер проверочного кода, два блока памяти, коммутатор и блок управления и синхронизации, первый выход которого соединен с входом бло- 15 ка приема, первый выход которого соединен с первым входом коммутатора, второй вход которого подключен к второму выходу блока управления и синхронизации, третий выход которого 20 соединен с первым входом информационного декодера и с входом первого бло- ка памяти, выход которого соединен с вторым входом информационного декодера, третий вход которого подключен к первому выходу коммутатора, вторые выходы которого соединены с первыми входами проверочного декодера, второй вход которого подключен к выходу второго блока памяти, вход которого подключен к четвертому выходу блока управления и синхронизации и к третьему входу проверочного декодера, вход которого соединен с первым входом блока сравнения, второй вход которого подключен к пятому выходу блока управления и синхронизации, шестой выход которого соединен с первым входом выходного согласующего блока, второй вход которого подключен к выходу блока сравнения, третий вход которого подключен к выходу кодера проверочного кода, первый вход которого подключен к седьмому выходу блока управления и синхронизации, вход которого соединен с вторым выходом блока приема, причем выход информационного декодера соединен с вто рым входом кодера проверочного кода.