Накапливающий сумматор

Иллюстрации

Показать всеРеферат

Изобретение относится к области - вычислительной техники и может быть использовано в процессорах ЭВМ и цифровых устройствах автоматики. Цель изобретения - упрощение устройства. Для достижения этой цели в сумматор введены два элемента НЕ и элемент ИЛИ, изменены связи между элементами и поэтому число триггеров в каждом двоичном разряде доведено до одного триггера, 2 ил., 1 табл.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (51) 4 G 06 F 7/50 >

j 1 !

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

К ДBTOPCHOMY СВИДЕТЕЛЬСТВУ (21) 3933790/24-24 (22) 22,07.85 (46) 23. 02. 87. Бюл. Ф 7(72) Б ° М. Власов (53) 68 1.325.5(088.8) (56) Авторское свидетельство СССР

Н 1112363, кл. G 06 F 7/50, 1984>

Авторское свидетельство по заявке

Ф 3719267/24, кл. G 06 F 7/50, 1984.

„„80„„1291 А 1 (54) НАКАПЛИВАЮЩИЙ СУММАТОР (57) Изобретение относится к области вычислительной техники и может быть использовано в процессорах ЭВМ и цифровых устройствах автоматики. Цель изобретения — упрощение устройства.

Для достижения этой цели в сумматор введены два элемента НЕ и элемент

ИЛИ, изменены связи между элементами и поэтому число триггеров в каждом двоичном разряде доведено до одного триггера. 2 ил., 1 табл.

1 129

Изобретение относится к вычисли. тельной технике и может быть использовано в процессорах ЭВМ и цифровых устройствах автоматики.

Цель изобретения — упрощение устройства.

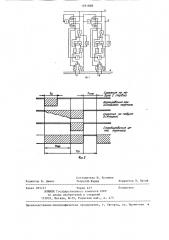

На фиг. 1 представлена функциональная схема двух разрядов предлагаемого сумматора, на фиг. 2 — временная диаграмма его работы.

Накапливающий сумматор содержит элементы ИЛИ 1-4, элементы И 5-10, накапливающий регистр на триггере 11, элементы НЕ 12 и 13, тактовый вход

14, вход 15 переноса из младшего разряда, вход 16 разрешения записи слагаемого, вход 17 разрешения сложения, вход 18 соответствующих разрядов слагаемых.

Рассмотрим работу сумматора при выполнении операции сложения двух положительных чисел, представленных в двоичном коде. Будем считать, что код первого слагаемого хранится в накапливающем регистре (триггеры 11), а код второго слагаемого поступает на вход 18.

В первом временном такте (t,) выполняется элементарная операция (ЭО) первого сложения по модулю два. Для выполнения этой ЭО на вход 16 подается исполнительный импульс. Если в рассматриваемом двоичном разряде сумматора на.входе 18 присутствует высокий (низкий) потенциал, соответствующий коду единицы, то исполнительный импульс по цепи И 9, ИЛИ 4 поступит на первые входы И 7 и 8 и выполнит инвертирование триггера 11, так как если в триггере 11 до поступления первого импульса хранился код единицы, то высокий (низкий) потенциал с единичного выхода триггера по цепи ИЛИ 3, И 6 поступит на второй вход И 7 и разрешит прохождение первого импульса на R-вход триггера, т.е. установит его в нулевое состояние. Заметим, что переключение триггера не меняет потенциала,с выхода

И 6, так как за счет связи R-входа с входом ИЛИ 3 на время длительности сохраняется прежнее значение сигнала

Если же до прихода первого импульса триггер 11 хранил код нуля, то с выхода НЕ 12 на второй вход И 8 поступает потенциал, разрешающий прохождение первого импульса на R-вход триггера 11. Первый тактовый импульс, 1968 2 поступивший на S-вход, одновременно поступает на вход НЕ 13 и запрещает появление высокого потенциала с выхода И 6 на время длительности импульса

Одновременно с выполнением 30 первого сложения по модулю два начинает формироваться потенциал переноса.

Если в триггере 11 хранится код единицы и на входе 18 присутствует потенциал единицы, то исполнительный импульс с выхода И 9 поступит на первый вход второго элемента ИЛИ 2 и с выхода И 7 этот же импульс поступит на второй вход ИЛИ 1. 3а счет этого на выходе И 5 сформируется потенциал переноса в старший разряд сумматора. Этот же потенциал с выхода И 5 поступает на третьи входы

ИПИ 1 и 2. Эта связь позволяет хранить сигнал переноса> выработанный в данном разряде, и после окончания действия первого исполнительного им25 ульса °

В период второго временного такта (t ) продолжает формироваться и распространяться в сторону старших разрядов потенциал сквозного переноса. Распространение сигнала переноса

30 должно завершиться до начала следующего временного такта, По третьему временному такту (t ) выполняется ЭО второго сложения по модулю два. Для выполнения этой ЭО на вход 17 подается исполнительный импульс. Если в данный двоичный разряд из младшего разряда сумматора на второй вход И 10 поступил потенциал переноса, то исполнительный

40 импульс по цепи И 10, ИЛИ 4 посту,пает на первые входы И 7 и 8 и выполняет инвертирование триггера 11. На этом операция-.сложения завершается.

Результат суммирования двух чисел будет храниться в триггерах 11. В момент выдачи результата сложения из сумматора выполняется ЭО стробирования (гашения) переносов, запоминаемых в цепях сквозного переноса. Эта

ЭО необходима для выполнения последующей операции сложения. Для ее выполнения с входа 14 снимается высокий (низкий) потенциал.

Пример выполнения операции сложения двух чисел приведен в таблице. ф о р м у л а и э о б р е т е н и я

Накапливакпций сумматор, содержащий в каждом разряде шесть элементов

Номер такта

Рааряды

Выполняемые операции, риггеры н вины

7 6 5 4 3

2 !

О 1 0 1 1

О О О 0 О

О 1 Триггеры 11, первое слагаемое, вход !8

О О

Исходное состояние

О» Триггеры 11 вход 18, второе слагаемое. словенце по модулю два (первое) О

О 1

1 О

Э

О,, О Триггеры 11, вход 18, распростране-

О О нне потенциала переноса

1 1 О 1

О О О О

О О

О О

О О

О О

О Триггеры 11, сумма, вход 18, слонение по

0 модулю два (второе) О

1. О

Триггеры 11, выдача суммы, вход !8 стробнрование (ганение) переноса

О 1

О 0 О О

Ю

Раяряды сумматора, в которых выработался потенциал переноса по времени t,.

Раяряды сумматора, в которых сформировался н вапомнился потенциал переноса по яремени t, и ts °

3 !2919

И, три элемента ИЛИ, RS-триггер,причем первый вход первого элемента И соединен с входом соответствующего разряда слагаемого сумматора, вход разрешения записи слагаемого сумматора соединен с вторым входом первого элемента И, выход которого соединен с первыми входами первого и второго элементов ИЛИ, вход разре— шения сложения сумматора соединен 10 с первым входом второго элемента И, выход которого соединен с вторым входом первого элемента ИЛИ,.выход которого соединен с первыми входами третьего и четвертого элемента И, выход четвертого элемента И соединен с S-входом RS-триггера, второй вход пятого элемента И соединен с выходом второго элемента ИЛИ, второй вход второго элемента И соединен с входом 20 переноса из младшего разряда сумматора, R-вход RS-триггера соединен с выходом третьего элемента И и первым входом третьего элемента ИЛИ, первый вход пятого элемента И соединен с тактовым входом сумматора, выход шестого элемента И соединен с вторым

68 4 входом второго элемента ИЛИ, о т -л ич а ю шийся тем, что, с целью упрощения устройства, в него введены два элемента HE и четвертый элемент

ИЛИ, первый вход которого соединен с прямым выходом RS-триггера, S-вход которого соединен с входом первого элемента НЕ, выход которого соединен с первым входом шестого элемента И, второй вход которого соединен с выходом четвертого элемента ИЛИ, второй вход которого соединен с выходом третьего элемента И, второй вход котoporo соединен с выходом шестого элемента И и входом второго элемента НЕ, выход которого соединен с вторым входом четвертого элемента И, третий вход второго элемента ИЛИ соединен с вторым входом третьего элемента ИЛИ, с выходом пятого элемента

И и выходом переноса в следующий разряд сумматора, третий вход третьего элемента ИЛИ соединен с входом переноса из младшего разряда сумматора, третий вход пятого элемента И соединен с выходом третьего элемента

ИЛИ.

1291968

Гни по Ф7Г /пероое! июйжио нам" мамоао переноса

errue по на8уио орое/

Фироооние грп ронодг

Составитель М, Есенина

Техред В.Кадар

Корректор Л, Патай

Редактор В. Данко

Заказ 265/47 Тираж 673

ВНИИПИ Государственного комйтета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раущская наб., д. 4/5

Подписное

Производственно-полиграфическое предприятие, r, Ужгород, ул. Проектная 4