Узел формирования переноса в сумматоре

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и электронике и может быть использовано при построении арифметико-логических устройств обработки цифровой информации, в частности при построении мносвразрядных сумматоров в качестве формирователя ускоренного переноса. Цель изобретения - упрощение узла формирования переноса в сумматоре. Узел формирования переноса содержит в каждом разряде два ЩП-транзистора р-типа, два МДП-транзистора п-типа, элемент И-НЕ, элемент ИЛИ-НЕ и два элемента НЕ. 1 ил., 2 табл. (Л и со со а со

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (51)4 С 06 F 7 50

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ г

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3967459/24-24 (22) 26.09 ° 85 (46) 23.02.87. Вюл. У 7 (72) В.А. Максимов, Я.Я. Петричкович, А.Е. Заболотный и В.Н. Филатов (53) 681,325.5(088.8) (56) Патент Японии Р 54-42573, кл. С 06 F 7/50.

Авторское свидетельство СССР

Р 1223223, кл. С 06 F 7/50, 1984.

ÄÄSUÄÄ 1291969 А1 (54) УЗЕЛ ФОРМИРОВАНИЯ ПЕРЕНОСА В

СУММАТОРЕ (57) Изобретение относится к вычислительной технике и электронике и может быть использовано при построении арифметико-логических устройств обработки цифровой информации, в частности при построении многоразрядных сумматоров в качестве формирователя ускоренного переноса..Цель изобретения — упрощение узла формирования переноса в сумматоре. Узел формирования переноса содержит в каждом разряде два МДП-транзистора р-типа, два МДП-транзистора п-типа, элемент

И-НЕ, элемент ИЛИ-НЕ и два элемента а с0

НЕ. 1 ил., 2 табл.

1291969

Изобретение относится к вычисли- тельной технике и электронике и может быть использовано при построении арифметико-логических устройств обработки цифровой информации, в 5 частности при построении многоразрядных сумматоров в качестве формирователя ускоренного переноса, Цель изобретения — упрощение узpea формирования переноса в сумматоре. 10

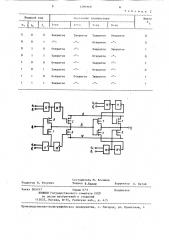

На чертеже представлена схема двух разрядов узла формирования переноса в сумматоре.

Узел формирования переноса в сумматоре содержит четыре МДП-транзистора 1-4 р-типа, четыре МДП-транзистора 5-8 п-типа, шину 9 питания, шину 10 нулевого потенциала, элементы И-НЕ 11 и 12, элементы ИЛИ-HE 13 и 14, элементы HE 15-18.

Узел работает следующим образом.

При совпадении логических значений первых разрядов слагаемых (и =

b = 0 либо a = Ь =1) на затворах

1 1

25 транзисторов 2 и 6 формируются уровни соответственно логических нулей .либо логических единиц, обеспечиваю щих открытое состояние, соответственно транзистора 2 либо транзистора 6.

При этом вне зависимости от логическо го состояния входа переноса Р,, на выходе первого инверсного переноса

P формируется уровень соответственно

"1" либо "0", При несовпадении логических значений первых разрядов слага-35 емых (a ib) на затворах транзисторов

2 и 6 формируются уровни соответственно "1" и "0", обеспечивающие их закрытое состояние. При этом на истоках транзисторов 1 и 5 формируются

11 11 уровни соответственно логическая 1 и логический "0", обеспечивающих формирование на выходе Р сигнала, инверсного по отношению к Р

В табл. 1 показаны состояния тран- 45 зисторов 1,2,5 и 6 в зависимости от входного кода а, b,, Р, и соответствующее каждому коду логическое состояние выхода P, °

I 50

Логическое уравнение, описывающее выход Р,, можно представить в виде

P =a.b, +а,. P, +b,, P,, представляющее собой инверсную функцию переноса первого разряда сумматора.

Второй разряд узла функционирует аналогично. При совпадении логических значений вторых разрядбв слагаемых о.,= b 0 либо а = Ь,=1 на затворах транзисторов 4 и 8 формируются уровни соответственно логических единиц либо логических нулей, обеспечивающих открытое состояние, соответственно транзисторов 8 либо 4, При этом вне зависимости от второго переноса формируется уровень соответственно "0" либо "1". При несовпадении логических значений вторых разрядов слагаемых а = b на затворах транзисторов 4 и 8 формируются уровни логических соответственно "1" и "0", обеспечивающих их закрытое состояние.

При этом на истоках транзисторов 3 и

7 формируются уровни логическая "1" и логический "О", обеспечивающие формирование на выходе Р сигнала, инверсного по отношению к Р

В табл. 2 показаны состояния транзисторов третьего 3, 4, 7 и 8 в зависимости от входного кода а, Ь,,Р, и соответствующее каждому коду логическое состояние выхода P

Логическое уравнение, описывающее выход Р,, можно представить в виде

Р,=а, ьд +(а,+ ь,)Р,, что соответствуеE функции переноса двухразрядного сумматора.

Формула и з обретения

Узел формирования переноса в сумматоре, содержащий. в каждом разряде первый, второй, ИДП-транзисторы

Р-типа, первый, второй ИДП-транзисторы п-типа, причем затворы первых МДПтранзисторов р- и п-типов каждого нечетного разряда узла. формирования переноса соединены с входом переноса иэ соответствующего предыдущего четного разряда узла формирования переноса, стоки первых и вторых ИДП-транзисторов р и и-типов каждого нечетного разряда узла формирования переноса соединены с инверсным выходом переноса в соответствующий последующий четный разряд узла формирования переноса,затворы первых ИДП-транзисторов р- и и-типов каждого четного разряда соединены с инверсными входами переноса иэ соответствующего предыдущего нечетного разряца узла формирования переноса,стоки первых и вторых1ДП-транзисторов р- и и-типов каждого четного разряда соединены с прямым выходом переноса в соответствующий следующий нечетный разряд узла формирования переноса, отличающийся

1291969

Таблица 1 транзистора

Выход

Состояние

1-го 2-ro 5-го 6-ro

0 Открытое Открытое Закрытое Закрытое

0 0

1 Закрытое

0 Открытое Закрытое

0 0

0 1

1 Закрытое

0 1

Открытое

Закрытое

Открытое

0 Открытое

1 0

1 0

1 Закрытое

11

Закрытое Открытое

1 Открытое

Открытое тем, что, с целью упрощения узла, в каждом разряде дополнительно содержатся элемент ИЛИ-НЕ, элемент И-НЕ и два элемента НЕ, причем истоки второго ИДП-транзистора р-типа и второ- 5

ro MgII-транзистора и-типа соединены соответственно с шиной питания и шиной нулевого потенциала узла формирования переноса, первый и второй входы элемента ИЛИ-НЕ нечетного разряда узла соединены соответственно с первыми входами соответствующих нечетных разрядов первого и второго операндов, первый и второй входы элемента И-НЕ нечетного разряда узла со- 15 единены соответственно с вторыми входами соответствующих нечетных разрядов первого и второго операндов узла, выход элемента ИЛИ-НЕ нечетного разряда узла соединен с истоком первого ИДП-транзистора и-типа и входом первого элемента НЕ соответствующего нечетного разряда, выход которого соединен с затвором второго ИДП-транзистора р-типа соответствующего не 25 четного разряда, выход элемента И-НЕ нечетного разряда узла соединен с истоком первого ИДП-транзистора р-типа и входом второго элемента НЕ соответI 30,ствующего нечетного разряда узла, вы,ход которого соединен с затвором втоIporo МДП-транзистора и-типа соответствующего нечетного разряда узла,первый и второй входы элемента И-HE четного разряда узла соединены соответственно с первыми входами соответствующих четных разрядов первого и второго операндов узла, первый и второй входы элемента ИЛИ-НЕ четного разряда узла соединены соответственно с вторыми входами соответствующих четных разрядов первого и второго оггерандов узла, выход элемента

И-НЕ четного разряда узла соединен с затвором второго 1ЩП-транзистора р-типа и входом первого элемента НЕ соответствующего четного разряда узла, выход которого соединен с истоком первого ИДП-транзистора п-типа соответствующего четного разряда узла, выход элемента ИЛИ-НЕ четного разряда узла соединен с затвором второго

ИДП-транзистора и-типа и входом элемента НЕ соответствующего четного разряда узла, выход которого соединен с истоком первого ИДП-транзистора р-типа соответствующего нечетного разряда узла.

l?919!!9

Таблица 2

Выход

Состояли» транзистора

Г- 3

3-ro

0 Закрытое

Закрытое Закрытое Открытое

Открытое

fl

Закрытое Закрытое

О Открьггое

1 Закрытое

О Открытое

Открытое

Закрытое

Открытое

1 Закрытое

О Открьггое

1 Закрытое

Открытое Закрытое

Редактор Н. Рогулич

Заказ 265/47 Тираж 673

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Подписное

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4

0 О

О, О

О 1

О 1

1,0

1 О

1 1

1 1

Составитель М..Есенина

Тежред В.Кадар КоРРектоР Л. Патай