Многоканальный формирователь последовательностей импульсов

Иллюстрации

Показать всеРеферат

Изобретение относится к импульсной технике и может быть использовано в устройствах для выработки периодических последовательностей импульсов , управляющих микросхемами с зарядовой связью. Целью изобретения является повьшение быстродействия и повьшение надежности за счет сокращения емкости блоков памяти. Устройство содержит генератор I тактовых импульсов , счетчик 7 адресов со счетным входом 8, входом 9 запуска и выходами разрядов 10-13, блок 14 памяти с выходом I5. Для достижения поставленной цели в формирователь введены блок 2 формирования периодических фазовых последовательностей импульсов с входом 3 и выходами 4-6, блок 16 оперативной памяти с входом 17 записи и выходами 18-20, образованы новые связи. Предложен пример конкретной реализации блока 2. 2 з.п. ф-лы, 2 ил. с € (Л Ъ

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

80 1292164 (50 4 Н 03 K 3/64

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

-"Л

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

Н АВТОРСНОМУ СВИДЕТЕЛЬСТВУ (21) 3921453/24-21 (22) 26.06.85 (46) 23.02.87. Бюл. Р 7 (72) А.В.Вето, Г.Н.Евграфов, В.В.Зарубкин,В.Я.Стенин и А.Б.Иейнин (53) 621.374.5(088.8) (56) Патент ФРГ N- 2831589, кл. Н 03 К. 3/64, 1981. (54) МНОГОКАНАЛЬНЫЙ ФОРМИРОВАТЕЛЬ

ПОСЛЕДОВАТЕЛЬНОСТЕЙ ИМПУЛЬСОВ (57) Изобретение относится к импульсной технике и может быть использова- но в устройствах для выработки периодических последовательностей импульсов, управляющих микросхемами с зарядовой связью. Целью изобретения является повьппение быстродействия и повышение надежности за счет сокращения емкости блоков памяти. Устройство содержит генератор I тактовых импульсов, счетчик 7 адресов со счетным входом 8, входом 9 запуска и выходами разрядов 10-13, блок 14 памяти с выходом 15. Для достижения поставленной цели в формирователь введены блок 2 формирования периодических фазовых последовательностей импульсов с входом 3 и выходами 4-6, блок 16 оперативной памяти с входом

17 записи и выходами 18-20, образованы новые связи. Предложен пример конкретной реализации блока 2. 2 з.п. а ф-лы, 2 ил.

2164 2 элементов И 24-26, вторые входы кото- рых соединены с выходами соответствую129 довательностеи импульсо с д и выходами 4-6, счетчик 7 адресов со счетным входом 8, входом 9 запуска (входная шина) и выходами 10-13 разрядов, блок 14 памяти с выходом 15, 25 блок 16 оперативной памяти с входом

17 записи и выходами 18-20.

Выход генератора 1 соединен с входом 3 блока 2, выходы 4-6 которого соединены с входными шинами данных 30 блока lб оперативной памяти. Входная шина 9 запуска соединена с входом запуска счетчика 7 адресов, счетный вход 8 которого соединен с выходом 4 блока 2. Выходы 10-13 разрядов счетчика 7 адресов соединены с соответствующими адресными входами блока

14 памяти, выход 15 которого соединен с входом 17 записи блока 16 оперативной памяти, выходы 18-20 которо-40

ro являются выходами устройства, Блок 2 формирования периодических фазовых последовательностей импульсов (фиг.1). содержит элемент ИСКЛЮЧА- 45

10ЩЕЕ ИЛИ 21, сднигоный регистр 22 с входом 23 синхронизации, логические элементы И 24-26, D-триггеры 27-29 °

Тактовые входы D-триггерон 27-29 объединены и соединены с входом 23 синх- >0 ронизации сдвигсзого регистра 22 и входом 3 блока 2. Первый и нторой выходы разрядов сдвигового регистра 22 через элемент ИСКЛ1ОЧАЮЩЕЕ ИЛИ 21 соединены с его входом последовательной записи данных, Выходы разрядов сдвигового регистра 22 соединены с информационными входами соответствующих

D òðèããåðîâ 27-29 и первыми входами

Изобретение относится к импульсной технике и может быть использовано в устройствах для выработки периодических последовательностей импульсов, управляющих микросхемами с зарядовой связью.

Цель изобретения — повьпцение быстродействия и повышение надежности за счет сокращения емкости блоков памяти.

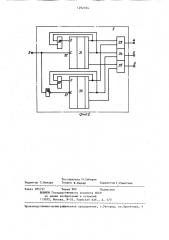

На фиг.l представлена .функциональная схема многоканального формирователя последовательностей импульсов; на фиг.2 — функциональная схема блока формирования периодических фазовых последовательностей импульсов (пример конкретной реализации).

Устройство содержит генератор 1 тактовых импульсов, блок 2 формирования периодических фазовых послев нхо ом 3

f5

20 щих D-триггеров 27-29. Выходы элементов И 24-26 соединены с соответствующими выходами 4-6 блока 2.

Блок 2 формирования периодических фазовых последовательностей (фиг.2) содержит элемент ИСКЛ1ОЧА1ОЩЕЕ ИЛИ 30, сдвиговый регистр 31 с входом 32 синхронизации, элементы И 33-35, сдвиговый регистр 36 с входом 37 синхронизации, элемент ИСКЛЮЧА1ОЩЕЕ

ИЛИ 38, инвертор 39.

Выходы двух разрядов сдвигового регистра 31 через элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 38 соедйнены с его входом последовательной записи данных. Выходы двух разрядов сдвигового регистра 36 через элемент ИСКЗПОЧАЮ11%Е

ИЛИ 30 соединены с его входом последовательной записи данных. Первые входы элементов И 33-35 соединены с выходами разрядов сднигового регистра 31, а вторые входы — с выходами разрядов сдвигового регистра 36. Выходы элементов И 33-35 являются выходами 4-6 блока 2. Вход 32 синхронизации непосредственно, а вход 37 синхронизации через инвертор 39 сое динены с входом 3 блока 2.

Устройство работает следующим образом.

Последовательность импульсов с периодом Т с выхода генератора 1 поступает на вход 3 блока 2, По отрицательному йерепаду напряжения на входе

23 синхронизации сднигового регистра

22 происходит сдвиг информации на один разряд и запись в первый разряд сдвигового регистра 22 нуля или единицы с выхода элемента ИСКЛОЧАЮЩЕЕ

ИЛИ 21, при помощи D-триггеров 2729 и логических элементон И 24-26 обеспечивается перекрытие фазовых импульсов на находах 4-6 на длительность импульса t, поступающего на вход 23 синхронизации сдвигового регистра. 22. С приходом на входную шину 9 запуска логического нуля счетчик 7 адресов получает разрешение на подсчет числа входных импульсов. По счетному входу 8 счетчика 7 адресов производится подсчет числа импульсов одной из фаз, например первой с ныхода 4, поступающих на входные шины данных блока 16 оперативной памяти. Блок 14 памяти запрограммирован таким образом, что по адресам меньФормула изобретения

1. Иногоканальный формирователь последовательностей импульсов, содержащий генератор тактовых импульсов, счетчик адресов, выходы разрядов которого соединены с соответствующими адресными входами блока памяти, отличающийся тем, что, с целью повышения быстродействия и повышения надежности, в него введены блок формирования периодических фазовых последовательностей импульI

55

3 !292! шим S в блоке 14 памяти записаны единицы, поступающие с выхода 15 блока

14 памяти на вход 17 записи блока

16 оперативной памяти, который работает в режиме сквозного пропускания импульсов с входных шин данных на выходы 18-20. По достижении адреса, соответствующего значению S, на выходе 15 блока 14 памяти появляется нуль, при помощи которого в блок 16 10 оперативной памяти записывается информация, присутствующая на входной шине данных блока 16 оперативной памяти в этот момент времени, и запрещается прохождение данных с вхо- 15 дов на выходы 18-20 блока 16 оперативной памяти (фиг.2).

Работа устройства с блоком 2 по фиг.2 аналогична описанному и оно работает следующим образом. 20

По отрицательному перепаду напряжения на входе 32 синхронизации сдвигового регистра 31 происходит сдвиг информации в сдвиговом регистре 31 на один разряд и запись в его первый разряд нуля или единицы с выхода элемента ИСКЛЮЧА!ОЩЕЕ ИЛИ 38.

Тактовые импульсы с выхода генератора 1 в инвертированном виде через инвертор 39 поступают на вход 30

37 синхронизации сдвигового регистра 36, при этом импульсы на его выходах оказываются сдвинутыми относительно импульсов на выходах сдвигового регистра 31 на длительность им- 35 пульса t генератора 1. С помощью элементов И 33-35 обеспечивается формирование перекрытия выходных фазовых импульсов блока 2, поступающих на выходы 18-20 устройства, на вели- 40 чину длительности импульса генератора 1 тактовых импульсов.

64 4 сов и блок оперативной памяти, причем выход генератора тактовых импульсов подключен к входу блока формирования периодических фазовых последовательностей импульсов, выходы которого подключены к соответствующим входным шинам данных блока оперативной памяти, счетный вход счетчика адресов подключен к первому выходу блока формирования периодических фазовых последовательностей импульсов, а выход блока памяти подключен к входу записи блока оперативной памяти, вход запуска счетчика адресов соединен с шиной запуска.

2, Иногоканальный формирователь по п. I, отличающийся тем, что блок формирования периодических фазовых последовательностей импульсов содержит сдвиговый регистр, выходы разрядов которого соединены с информационными входами соответствующих D-триггеров и первыми входами соответствующих элементов И, вторые входы которых соединены с выходами соответствующих D-триггеров, вход блока соединен с входом синхронизации сдвигового регистра и объединенными тактовыми входами D-триггеров, первый и второй выходы сдвигового регистра через элемент ИСКЛИЧА10ЩЕЕ ИЛИ соединены с его входом последовательной записи данных, выходы элементов И являются выходами блока.

3. Иногоканальный формирователь по п. I отличающийся тем, что блок формирования периодических фазовых последовательностей импульсов содержит первый сдвиговый регистр, выходы которого соединены .. с первыми входами элементов И, второй сдвиговый регистр, выходы которого соединены с вторыми входами элементов И, первый и второй выходы разрядов каждого сдвигового регистРа чеРез элементы ИСКЛЮЧАЮЩЕЕ. ИЛИ соединены с их входами последовательной записи данных, вход блока соединен с входом синхронизации первого сдвигового регистра непосредственно, а с входом синхронизации второго сдвигового регистра через инвертор, выходы элементов И являются выходами блока.

129Zle4

Составитель fO. Сибиряк

Редактор С.Пекарь Техред B.Кадар Корректор Г.Решетник

Заказ 285/57 Тираж 902 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.ужгород, ул.Проектная, 4