Цифровой генератор синусоидальных колебаний

Иллюстрации

Показать всеРеферат

Изобретение относится к импульсной технике и может найти применение в измерительной аппаратуре и устройствах автоматики. Цель изобретения - расширение диапазона генерируемых частот и упрощение устройства. Цифровой генератор (ЦГ) содержит задающий генератор 1 импульсов, делитель 2 частоты импульсов с переменным коэффициентом деления (Д), реверсивный счетчик 4 импульсов, дешифратор 5 и управляемьш интегратор 7. В устройство введены делитель 3 частоты импульсов с переменным коэффициентом деления, блок 6 преобразования кода. При этом максимальная неискаженная частота генерируемых ЦГ колебаний зависит от числа разрядов Д 2. Чем больбольше число разрядов Д 2, тем ниже генерируемая частота. Верхняя граница частотного диапазона ЦГ практически ограничена только быстродействием Д 3 и частотой задающего генератора 1 импульсов. Широкий диапазон частот ЦГ объясняется отсутствием погрешностей , вносимых умножителем частоты . 2 з.п. ф-лы, 4 ил. (Л ISD со to О5

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51) 4 Н 03 К 4/00 фе Г ° т . ° з йа . ч. °

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3768270/24-21 (22) 11.07.84 (46) 23.02.87. Бюл. ¹ 7 (72) Г.В.Боронин, В.Е.Денищенко и А.А.Шамов (53) 621.374 (088.8). (56) Авторское свидетельство СССР № 764107, кл. Н 03 К 4/00, 1976.

Смеляков В.В. Цифровая измерительная аппаратура инфранизких частот. — M.: Энергия, 1975, с. 130, рис. 3-19.

Марше Ж. Операционные усилители и их применение. — М.: Энергия, 1974, с. 78, рис. 5-43. (54) ЦИФРОВОЙ ГЕНЕРАТОР СИНУСОИДАЛЬНЫХ КОЛЕБАНИЙ (57) Изобретение относится к импульсной технике и может найти применение в измерительной аппаратуре и устройствах автоматики. Цель изобретения— расширение диапазона генерируемых

„„SU„„1292167 A 1 частот и упрощение устройства. Цифровой генератор (ЦГ) содержит задающий генератор 1 импульсов, делитель

2 частоты импульсов с переменным коэффициентом деления (Д), реверсивный счетчик 4 импульсов, дешифратор 5 и управляемый интегратор 7. В устройство введены делитель 3 частоты импульсов с переменным коэффициентом деления, блок 6 преобразования кода.

При этом максимальная неискаженная частота генерируемых ЦГ колебаний зависит от числа разрядов Д 2. Чем больбольше число разрядов Д 2, тем ниже генерируемая частота. Верхняя граница частотного диапазона ЦГ пракЖ тически ограничена только быстродейстанем Д 3 н частотой задающего гене- Q) ратора 1 импульсов. Широкий диапазон частот ЦГ объясняется отсутствием по- С грешностей, вносимых умножителем частоты. 2 з.п. ф-лы, 4 ил. !

Мейб

1292167

Изобретение относится к импульсной технике и может найти применение в измерительной аппаратуре и устройствах автоматики.

Цель изобретения — расширение диа- $ пазона генерируемых частот при одновременном упрощении устройства.

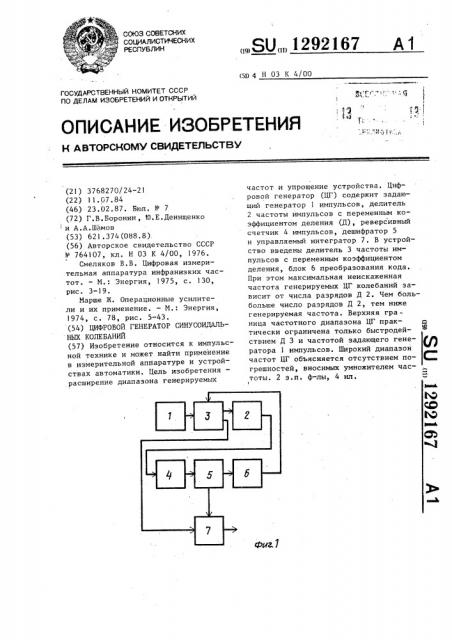

На фиг.l приведена структурная схема устройства; на фиг.2 — функциональная схема блока преобразования кода; на фиг.3 — функциональная схема управляемого интегратора; на фиг.4 временные диаграммы работы устройства.

Устройство содержит задающий гене«!5 ратор 1 импульсов, первый и второй деделители 2 и 3 частоты импульсов с переменным коэффициентом деления, pef ерсивный счетчик 4 импульсов, дешифратор 5, блок 6 преобразования кода и управляемый интегратор 7.

Задаюший генератор 1, второй делитель 3, первый делитель 2, реверсивный счетчик 4, дешифратор 5 и блок б соединены последовательно.

Выход блока б соединен с вторым выходом второго делителя 3, второй выход которого соединен с первым входом управляемого интегратора 7, второй вход которого соединен с вторым выходом дешифратора 5, а выход является выходом устройства.

Блок 6 содержит с первого по шестОЙ разряДы 8-13 ВХОДНОЙ шины, с первого по пятый элемент 2И-2ИЛИ-НЕ

l4-lg» триггер 19, с первого по шестой элементы И-НЕ 20-25. Первый разряд 8 соединен с входом установки в ноль триггера 19 и первым 4О входом первого элемента И пятого элемента 2И-2ИЛИ-НЕ 18, второй разряд

9 соединен с первыми входами вторых элементов И четвертого и пятого элементов 2И-2ИЛИ-НЕ 17и 18, третий раз-45 ряд 10 соединен с первыми входами первых элементов И третьего и чет-, вертого элементов 2И-2ИЛИ-НЕ lби 17, четвертый разряд 11 соединен с первыми входами вторых элементов И второго и третьего элементов 2И-2ИЛИ-НЕ

15 и 16, пятый разряд 12 соединен с первыми входами первых элементов И первого и второго элементов 2И-2ИЛИ-HE

14 и !5, шестой разряд 13 соединен с первым входом второго элемента И первого элемента 2И-2ИЛИ-HE 14 и входом установки в единицу триггера 19, прямой выход которого соединен с. вторыми входами вторых элементов И первого, третьего и пятого элементов

2И-2ИЛИ-НЕ 1 4, 16 и 18 и с вторыми входами первых элементов И второго и четвертого элементов 2И-2ИЛИ-НЕ 15, 17, а инверсный выход триггера 19 соединен с вторыми входами первых элементов И первого, третьего и пятого элементов 2И-2ИЛИ-НЕ 14, 16 и !8 и вторыми входами вторых элементов И второго и четвертого элементов

2И-ИЛИ-НЕ !5 и 17. Первые, входы с первого по шестой элементов И-НЕ

20-25 соединены с выходом пятого элемента 2И-ИЛИ-НЕ 18, вторые входы с первого по четвертый элементов И-НЕ

20-23 соединены с выходом четвертого элемента 2И-2ИЛИ-НЕ 17, второй вход пятого элемента И-НЕ 24 и третьи входы первого и второго элементов

И-НЕ 20 и 21 соединены с выходом третьего элемента 2И-2ИПИ-НЕ 16, второй вход шестого элемента И-НЕ 25, третий вход пятого элемента И-НЕ 24 и четвертый вход первого элемента ,И-НЕ 20 соединены с выходом второго элемента .2И-2ИЛИ-НЕ 15, третий вход третьего элемента И-НЕ 22 и четвертый вход пятого элемента И-НЕ 24 соединены с выходом первого элемента

2И-2ИЛИ-НЕ 14„

Выходы с первого по шестой элементов И-НЕ 20-25 образуют соответственно с шестого по первый разряды выхода блока б.

Управляемый интегратор 7 содержит триггер 26, первый и второй ключи 27 и 28, двухвходовой интегратор

29. Вход триггера 26 является вторым входом управляемого интегратора 7, прямой и инверсный выходы триггера

26 соединены с. управляющими входами первого и второго ключей 27 и 28, входы которых объединены и образуют первый вход управляемого интегратора 7, а выходы соединены соответственно с первым и вторым выходами двухвходовога интегратора 29, выход которого является выходом управляемого интегратора 7 °

Реверсивный счетчик 4 может быть выполнен по одной из известных схем с переключением направления счета при переполнении. Двухвходовый интегратор 29 также может быть выполнен по известной схеме. Остальные блоки выполнены на типовых элементах.

3 -! 2921

Рассмотрим работу цифрового генератора . Условимся наличие потенциала на выходе какого-либо логического элемента считать 1, а его отсутстн

lt tl вие 0

С выхода задающего генератора напряжение с частотой f поступает на счетный вход второго делителя 3, который по первому выходу имеет постоянный коэффициент деления, рав- !0 ный п, независящий от управляемого кода. C первого выхода этого делителя напряжение с частотой f„

f п поступает на счетный вход пер-. !

5 вого делителя 2. Коэффициент деления этого делителя изменяется переключателями от 1 до N.

При изменении коэффициента деления первого делителя 2 меняется выходная 20 частота цифрового регистра. С выхода первого делителя 2 импульсы с частотой — — поступают на вход реверN. сивного счетчика 4. Емкость ревер- 25 сивного счетчика 4 определяет число участков аппроксимации генерируемой синусоиды. От числа участков аппроксимации зависит коэффициент нелинейных искажений генерируемых колебаний.30

Поэтому емкость счетчика 4 выбирается исходя из заданного коэффициента нелинейных искажений, который при линейной аппроксимации равен (2, с98 ). 35

К = — — (1 2й

720 l где f — число участков аппроксимации всего периода синусоиды.

ТаК как реверсивный счетчик 4 40 определяет число участков аппрокси.мации только четверти периода сину- . соидального Сигнала, то его емкость

E будет равна ††.. Выходной код счет4 45 чика 4 поступает на вход дешифратора 5. Первый выход дешифратора 5 подключен к кодовым шинам фтока 6, с выхода которого поступают коды,.

1 пропорциональные значениям синуса 50 .в точках аппроксимации. Эти коды определяют углы наклона аппроксимирующих прямых для каждого участка аппроксимации, Выход блока 6 поразрядно соединен с вторым входом вто-, рого делителя 3. На втором .выходе второго делителя 3 за. время T„

= — — формируется пачка импульсов, .л

67 приблизительно равномерно распределенных по интервалу времени Т„, количество которых в пачке, пропорционально управляющему коду. Пачки импульсов с второго выхода второго делителя 3 поступают на первый вход управляемого интегратора 7. Число импульсов в пачке определяет скорость нарастания напряжения на выходе управляемого интегратора 7, т.е. наклон аппроксимирующей прямой на данном участке аппроксимации.

Рассмотрим процесс формирования синусоидального напряжения. В момент времени, когда реверсивный счетчик 4 заполнен, на разряде 13 фиг. (фиг.2) блока 6 появится "1", которая установит триггер 19 в "1". Единица с прямого выхода триггера 19 откроет левые (по фиг.2) элементы И элементов,2И-2ИЛИ-НЕ 14-18. При этом

"1" с разряда 13 пройдет через элемент 14 на входы элементов 22 и 24, в результате чего на выходе блока 6 появится код 001010, в соответствии с которым на выходе второго делителя

3 появится соответствующая пачка импульсов, число которых и определит угол наклона аппроксимирующей прямой на участке от t, до t, (фиг.4 }. При поступлении очередного импульса на вход реверсивного счетчика 4 выходной код его изменится так (в это время он работает на вычитание), что на разряде 12 блока 6 появится "1", которая, пройдя через элемент 15, изменит код на выходе блока 6. Значение кода станет равным 100011.

Этим кодом будет задан другой наклон аппроксимирующей прямой на втором участке от t до t и т.д. Когда

1 2 значение кода в реверсивном счетчике

4 будет равно 001, на разряде 9 бло :ка 6 появится "14, которая, пройдя через элемент 18, сформирует на выходе блока 6 код llllll. С приходом очередного импульса на вход реверсивного счетчика 4 его выходной код станет равным 000. На этом заканчивается формирование первой четверки синусоиды. В это время на разряде 8 блока появится "1", которая установит триггер 19 в состояние "0", при этом закроются левые (по.фиг.2) и откроются правые элементы И элементов

2И-2ИЛИ-НЕ 14-18. Через правый элемент И элемента 2И-2ИПИ-НЕ 18 единица с разряда 8 пройдет на .входы элементов И-НЕ 20-25 и на выходе бло5 129216 ка 6 появится код llllll, т.е. такой же, какой был сформирован до этого единицей с разряда 9. Действительно углы наклона аппроксимирующих прямых на участках t -t и t, --t (фиг.4, е)

9 9 6 равны, Тоже можно сказать и об участках t -t è С -t» C,-t u и C- C-1 иt-C . Участ2 8 9 о 1 1О ком аппроксимации t,-t,, заканчивается процесс формирования половины 1р синусоиды. Вторая половина синусоиды формируется аналогичным образом.

Рассмотрим работу управляемого интегратора 7. С второго выхода второго делителя 3 пачки импульсов 15 (фиг ° 4, а) поступают на первый вход управляемого делителя 7. Когда код реверсивного счетчика 4 достигает максимального значения, на втором выходе дешифратора 5, а следователь- 2р но, и на счетном входе триггера 26 появляется "1" (фиг.4,5 ), которая опрокидывает триггер 26 (фиг.4,6).

При наличии "1" на прямом выходе триггера 26 ключ 28 закрыт, а ключ 25

27 открыт. При этом пачки импульсов, поступающие на первый вход управляемого интегратора 7, проходят через ключ 7 (фиг,4, z),ïoñòóïàþò на первый вход двухвходового интегратора 29 и Зр заряжают имеющийся в нем конденсатор. Заряд идет все время, пока реверсивный счетчик 4 считает от максимального значения до нуля и обратно до максимального значения эа время от е . до (фиг.4, е). После этого на втором входе управляемого интегратора 7 опять появится ")" (фиг.4,8 ), которая опрокидывает триггер 26, при этом на инверсном выходе триггера 26 рр .появляется "1", а на прямом "О" (фиг.4,8). Ключ 27 закрывается, а ключ 28 открывается и импульсы, поступающие на первый вход управляемого интегратора 7, пройдя через ключ

28 (фиг.4,a ), поступают на второй вход двухвходового интегратора 29 и начинают разряжать конденсатор — участок времени от t„ до t (фиг.4,е).

Разряд емкости происходит такое же 50 время, как и ее заряд. В дальнейшем цикл заряда и разряда емкости повторяется. В результате на выходе интегратора 7 формируется. синусоидальное напряжение (фиг.4,e). 55

Минимальная неискаженная частота генерируемых цифровым генератором колебаний зависит от числа разрядов первого делителя 2. Чем больше

6 число разрядов первого делителя 2, тем ниже генерируемая частота. Увеличение разрядности первого делителя 2 каких-либо технических трудностей не вызывает.

Верхняя граница частотного диапазона цифрового генератора практически ограничена только быстродействием схемы второго делителя 3 и частотой задающего генератора 1.

Коэффициент нелинейных искажений при линейной аппроксимации зависит от количества участков апйроксимации. В предположении, что интегратор 7 линеен, других погрешностей ( при генерированйи колебаний генератор не имеет. Широкий диапазон частот предлагаемого цифрового генератора по сравнению с известным объяс няется отсутствием погрешностей, вносимых умножителем частоты.

Формула изобретения

1. Цифровой генератор синусоидальных колебаний, содержащии задающий генератор импульсов, первый делитель частоты импульсов с переменным коэффициентом деления, реверсивный счетчик импульсов, выход которого соединен с входом дешифратора, и управляемый интегратор, о т л и ч а ю щ и йс я тем, что, с целью расширения диапазонов генерируемых частот при одновременном упрощении устройства, в него введены второй делитель частоты импульсов с переменным коэффициентом деления и блок преобразования кода, причем выход задающего генератора импульсов соединен с первым входом второго делителя частоты импульсов с переменным коэффициентом деления, первый выход которого через первый делитель частоты импульсов с переменным коэффициентом деления соединен с входом реверсивного счетчика, а первый выход дешифратора через блок преобразования кода соединен с вторым входом второго делителя частоты, второй выход которого соединен с первым входом управляемого интегратора, второй вход которого соединен с вторым выходом дешифратора.

2. Генератор по п. 1, о т л и— ч а ю шийся тем, что блок преобразования кода содержит с первого по пятый элементы 2И-2ИЛИ-НЕ, триггер, 1292!67 с первого ло шестой элементы И-НЕ, причем первый разряд входа блока соединен е входом установки в ноль триггера и первым входом первого элемента И пятого элемента 2И-2ИЧИ-НЕ, 5 второй разряд — с первыми входами вторых элементов И четвертого и пятого элементов 2И-2ИЛИ-НЕ,. третий разряд — с первыми входами первых элементов И третьего и четвертого элементов 2И-2ИЛИ-НЕ, четвертый разряд — с первыми входами вторых элементов И второго и третьего элементов 2И-2ИЛИ-НЕ, пятый разряд — с первыми входами первых элементов И пер15 вого и второго элементов 2И-2ИЛИ-НЕ„ шестой разряд входа — с первым входом второго элемента И первого элемента 2И-2ИЛИ-НЕ и входом установки в единицу триггера, прямой выход которого соединен с вторыми входами вторых элементов И первого, третьего, пятого и с вторыми входами первых элементов И второго и четвертого эле-2 ментов 2И-2ИЛИ-НЕ, а его инверсный выход соединен с вторыми входами первых элементов И, первого, третьего, пятого и второго элементов И второго и четвертого элементов 2И-2ИЛИ-НЕ 30 при этом первые входы с первого по шестой элементов И-НЕ соединены с выходом пятого элемента 2И-2ИЛИ-НЕ, . вторые входы с.первого по четвертый элементов И-НЕ соединены с выходом четвертого элемента 2И-2ИЛИ-НЕ, второй вход пятого элемента И-НЕ и третьи входы первого и второго элементов И-HE соединены с выходом третьего элемента 2И-2ИЛИ-НЕ, второй вход шестого элемента И-НЕ, третий вход пятого элемента И-НЕ и четвертый вход первого элемента И-НЕ соединены с выходом второго элемента 2И-2ИЛИ-НЕ, третий вход третьего элемента И-НЕ и четвертый вход пятого элемента

И-hE соединены с выходом первого элемента 2И-2ИЛИ-НЕ, а выходы с первого по шестой элементов И-НЕ образуют соответственно с шестого по первый разряды выхода блока преобразования кода.

3. Генератор по п. 1, о т л и ч а— ю шийся тем, что управляемый генератор содержит триггер, первый и второй ключи и двухвходовый интегратор, причем вход триггера является вторым входом управляемого интегратора, прямой и инверсный выходы триггера соединены с управляющими входами соответственно первого и второго ключей, входы которых соединены с первым входом управляемого интегратора, а выходы соединены соответственно с первым и вторым входами двухвходо" вого интегратора, выход которого является выходом управляемого интегратора.

1292167

f fJ tJ 4 р6 Йу6у6ю

Корректор В,Бутяга

Техред В.Кадар

Редактор С.Пекарь

Заказ 285/57 Тираж 902 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Иосква, )!1-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.ужгород, ул.Проектная, 4