Устройство для детектирования амплитудно-фазомодулированных сигналов

Иллюстрации

Показать всеРеферат

Изобретение относится к технике передачи данных по каналам связи и обеспечивает повьшшние помехозащиценности при скачках фазы. Устр-во содержит групповой коррелятор 1, блоки 2, 25 пересчета проекций сигнала , преобразователи кода 3, 4, решающий блок 5, блок 6 декодирования, ЙГ1 Д./ М -Hj м-- гщ- ВыкоУдониых -5 1 R (Л

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

А1 (19) (11) (51) 4 Н 04 L 27/22

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3780053/24-09 (22) 08.08.84 (46) 23.02.87.Бюл. Р 7 (71) Одесский электротехнический институт связи им.А.С.Попова (72) В.А.Балашов, П.Я.Нудельман, В.С.Скляр, К,Л.Спиваковский, k.È.Темесов и И.B.111евченко (53) 621.394.62 (088.8) (56) Авторское свидетельство СССР

У 543195, кл. Н 04 L 27/22, 1975.

С И (54) УС РО .ЯСТВО ДЛЯ ДЕТЕКТИРОВАНИЯ

АМПЛИТУДНО-ФАЗОМОДУЛИРОВАННЫХ СИГНАЛОВ (57) Изобретение относится к технике передачи данных по каналам связи и обеспечивает повьш ение помехоза( шюценности при скачках фазы. Устр-во содержит групповой коррелятор 1, блоки 2, 25 пересчета проекций сигнала, преобразователи кода 3, 4, ре- шаюший блок 5, блок 6 декодирования, 1292202

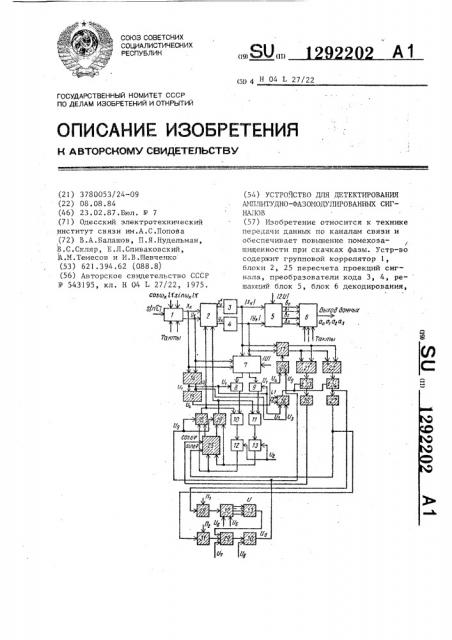

Устройство для детектирования амплитудно-фазомодулированных сигналов содержит групповой коррелятор f5

1, первый блок ? пересчета проекций сигнала, первый 3 и второй 4 преобразователи кода, решающий блок 5, блок 6 декодирования, анализатор 7 . фазовой расстройки, первый 8 и вто20 рой 9 коммутаторы, первый 10 и второй I) сумматоры, первый 12 и второй !

3 оперативные запоминающие бло, .ки, амплитудный селектор !4, элемент ИЛИ 15, третий 16, четвертый 17, пятый 18 и шестой

19 коммутаторы, первый элемент И 20, третий 21 и четвертый 22 сумматоры, первый 23 и второй 24 перемножители, второй блок .25 пересчета проекций сигнала, первый 26 и второй 27 усреднители, первый блок 28 сравнения, второй элемент И 29, триггер 30, второй блок 31 сравнения, регистр 32 сдвига, третий элемент И 33, анализатор 7 фазовой расстройки, коммутаторы 8, 9, 16-19, сумматоры

10, ll, 21, 22, оперативные запоминающие блоки 12, 13, амплитудный селектор 14, элементы ИЛИ 15, И 20, 29, 33, перемножители 23, 24, усреднители 26, 27, блоки 28,31 сравнения, триггер 30, регистр сдвига 32. В групповом корреляторе 1 вычисляются коэф.корреляции входного группового сигнала с 2 и опорными сигналами.

В решающем блоке 5 они сравниваются с порогом. В результате сравнения формируется четырехразрядное двоич,ное число, которое декодируется в переданные по данному каналу инфорИзобретение относится к технике передачи данных по каналам связи и может использоваться для построения когерентных приемников высокоскоростных многоканальных УПС. 5

Цель изобретения — повышение помехозащищенности при скачках фазы.

На чертеже представлена структурная электрическая схема предлагаемого, устройства. !О мационные символы. Анализатор 7 вырабатывает значения корректирующих коэф. для каждого канала, которые затем усредняются в групповом цифровом интеграторе, состоящем из ком,мутаторов 8,9, сумматоров 10, 11 и запоминающих блоков 12, 13. Полученные значения коэф. пересчета через коммутаторы 18,19 поступают на блок 2. Для исключения ложных срабатываний схемы компенсации скачка фазы в случае вхождения в синхро, низм предусмотрен детектор синхронизма, состоящий из блока сравнения

28, регистра сдвига 32 и элемента

И 33. 1 ил.

Устройство работает следующим образом.

Входной групповой сигнал S (n q ) поступает на вход группового корре, лятора 1, в котором по определенному алгоритму на каждом тактовом интервале вычисляются коэффициенты корреляции Х „ и У (k=1,2,...,n) входного сигнала с 2 и опорными сигналами. Полученные коэффициенты . преобразуются в первом блоке 2 по соответствующему алгоритму через первый 3 и второй 4 преобразователи. кода подаются в решающий блок 5, где сравниваются с порогом, равным ()2nj), В результате сравнения формируется четырехразрядное двоичное число

b b,Ь Ь, которое декодируется в блоке 6 декодирования в переданные по данному каналу УПС информационные о а< а2 аз °

Подстройка значений коэффициентов пересчета созц„и sing» (k =

1,2... п) осуществляется сигналами, поступающими с пятого 18 и шесто- го 19 коммутаторов. Анализатор 7 фазовой расстройки вырабатывает значения корректирующих коэффициентов

ЬХ„и Ь У (k=1,2,...,n) для каждого канала, которые затем усредняются в групповом цифровом интеграторе, состоящем из первого 8 и второго 9 коммутаторов, первого 10 и второго 11 сумматоров и первого 12

1292202

45 и второго 13 запоминающих блоков.

Полученные на выходе первого 12 и второго 13 запоминающих блоков зна,чения cos(pÄ v sin(p„ (k = 1,2,...,n) через пятый 18 и шестой 19 коммутаторы коммутируются на входы первого блока 2.

Амплитудный селектор 14 анализирует сигналы A„ (X»,V») и вырабатывает сигнал U при обработке сиг- 10 налов с минимальной амплитудой (класс S (1) и сигнал U> при обработке сигналов с максимальной амплитудой (класс S (3). Элемент ИЛИ 15 осуществляет операцию логического . f5 сложения сигналов U Ч U = U . Так3 4 товый сигнал U> служит для синхронной с обрабатываемыми сигналами

А < (Х„,VK), k = 1,п выдачи из первого 12 и второго 13 запоминающих 20 блоков соответствующих коэффициентов созц> и sing,, k =1,и. При отсутствии скачка фазы триггер 30 находится в естественном состоянии "01, и сигналом U> с его выхода на выходы пятого 18 и шестого 19 коммутаторов коммутируются первые их входы, а четвертый коммутатор 17 подключает сигналы на входы третьего и четвертого сумматоров 21 и 22, когда 30 обрабатываются сигналы из классов

S (i) и S (3). Сигнал управления четвертым коммутатором 17 формируется первым элементом И 20, реализующим функпию U4 Л Uq Сигналы А„ (Х„,Y»)

% М соответствующие классам S (1) и

S,3), поступают на входы третьего

21 и четвертого 22 сумматоров. Полученные сигналы масштабируются путем умножения их амплитуд в первом 23 и втором 24 перемножителях на коэффициенты,и р, которые коммутируются третьим коммутатором 16, в зависимости от наличия управляющего сигнала S (1) либо S (3). Амплитуда сигналов Х» и У», соответствующая ° сигналу. S (1), умножается на коэффициент g,, а амплитуда сигналов

Х „ и У», соответствующая сигналам из класса S (3),,умножается íà g

Промасштабированные подобным образом амплитуды сигналов Х» и Y соответствуют значениям тригонометрических функций cos h(g и здп ьсф„ соответственно, где АЦ» = ЬЦ + Р„,, 55

Ь вЂ” величина скачка фазы с точо ностью +45, а У» — помеха в канале УПС. Полученные значения cos А(р и sindlfp усредняются в течение посыпки в первом 26 и втором 27 усреднителях. Амплитуда усредненного сигнала sin hp сравнивается во втором блоке 31 сравнения с порогом

П, и в случае его превьппения по сигналу U7 при наличии сигнала синхронизма U ð вторым элементом

И 29 формируется сигнал установки триггера 30 в состояние "Лог.1".

Сравнение сигнала sin Ьщ с порогом

П преследует цель уменьшить влия2 ние небольших случайных флуктуаций фазы, которые вызываются шумами в каналах. Значение порога П выбирается о в пределах sin 3 — sin 5Р. На следующем тактовом интервале сигналом Ll третий коммутатор 17 размыкается, чем достигается запоминание предыдущего состояния первым и вторым усреднителями 26 и 27, а пятый и шестой коммутаторы 18 и 19 коммутируют на выход сигналы с выхода второго блока 25 пересчета проекций сигнала.

При этом на очередном тактовом интервале сигналы cosg, и sing„, k = 1,п преобразуются дополнительно во втором блоке 25 в соответствии с заданными алгоритмами, т.е. осуществляется компенсация скачка фазы. С выхода пятого 18 и шестого 19 коммутаторов откорректированные сигналы

cos cf „ и sing>„ k = 1,и поступают на входы первого блока 2 и первые входы первого 10 и второго 11 сумма торов. В конце цикла обработки сигналов Х„ и У„ сигналом U8 триггер 30 устанавливается в состояние "Лог.00 и устройство возвращается в первоначальное состояние.

Чтобы избежать ложных срабатываний схемы компенсации скачка фазы в случаях вхождения в синхронизм, в предложенном устройстве предусмотрен детектор синхронизма, состоящий из первого блока 28 сравнения,, ре— гистра 32 сдвига и третьего элемента

И 33.

Амплитуда сигналов сравнивается в первом блоке 28 сравнения с порогом

П,, а результат сравнения записывается в соответствующую данному каналу ячейку регистра 32 сдвига. Выходы регистра 32 сдвига объединены через третий элемент И 33. В случае, когда во всех каналах УПС подстройка фаз будет завершена, амплитуды сигналов

sinhq>», k = 1,п станут меньше порога и во все ячейки регистра сдвига 32

1292202

25

ННИИПИ Заказ 288/59 Тираж 639 Подписное Произв-аолигр, пр-тие, r. Ужгород, ул. Проектная, 4 будут записаны "Лог.1",третьим эле- ментом И 33 формйруется сигнал U разрешающий компенсацию скачка фазы.

Сигнал 1 служит для очищения ре5 гистра 32 сдвига при первоначальном вхождении в синхронизм. Тактовый сигнал служит для сдвига информации в регистре 32 сдвига, Формула изобретения

Устройство для детектирования амплитудно-фазомодулированных сигналов, содержащее групповой коррелятор, выходы которого подключены к одним входам первого блока пересчета проекций сигнала, выходы которого . соединены с входами преобразователей кода, выходы которых подключены к одним входам анализатора фазовой расстройки, другие входы которого соецинены с выходами группового коррелятора, и к входам решающего блока, выходы которого соединены с входами блока декодирования, при этом выходы анализатора фазовой расстройки подключены к сигнальным входам первого и второго коммутаторов, выходы которых соединены соответственно с первыми входами первого и второго сумматоров, выходы которых подключены соответственно к первым входам первого и второго оперативных .запоминающих блоков, вторые входы которых объединены, о т л ич а ю щ е е с я тем, что, с целью повышения помехозащищенности при скачках фазы, введены три элемента

И, третий, четвертый, пятый и шестой коммутаторы, элемент ИЛИ, третий и четвертык сумматоры, два перемножи. теля, два усреднителя, два блока сравнения, триггер, регистр сдвига, второй блок пересчета проекций сигнала и амплитудный селектор, выходы которого соединены с управляющими входами первого и второго коммутаторов, с входами элемента ИЛИ, выход которого подключен к первому входу первого элемента И, и с сигнальными входами третьего коммутато" ра, выход которого подключен к первому входу первого перемножителя, второй вход которого соединен с выходом третьего сумматора, и к первому входу второго перемножителя, второй вход которого соединен с выходом четвертого сумматора, входы которого соединены с входами третьего сумматора и с выходами четвертого коммутатора, сигнальные и управляющий входы которого соединены соответственно с одними входами анализатора фазовой расстройки, другие входы которого соединены с входами амплитудного селектора, и с выходом первого элемента И, второй вход которого соединен с выходом триггера, к входу которого подключен выход второго элемента И, с управляющж входом пятого коммутатора, выход которого подключен к второму входу первого сумматора, и с управляющим входом шестого коммутатора, выход которого подключен к второму входу второго сумматора, причем выходы первого и второго перемножителей через соответственно первый и второй усреднители подключены к одним входам второго блока пересчета проекций сигнала, другие входы которого соединены соответственно с первыми сигнальными входами пятого и шестого коммутаторов, выходы которых подключены к другим входам первого блока пересчета проекций сигнала, и с выходами первого и второго опе—

35 ративных запоминающих блоков, вы.ходы второго блока пересчета проек,ций сигнала подключены к вторым сигнальным входам пятого и шестого коммутаторов, выход второго перемножителя через первый блок сравнения, второй вход которого является первым пороговым входом устройства, подключен к входу регистра сдвига, выходы которого соединены с входами третьего элемента И, выход которого подключен к первому входу второго элемен— та И, второй вход которого соединен с выходом второго блока сравнения, к первому входу которого подключен выход второго усреднителя. а второй вход второго блока. сравнения является вторым пороговым входом устройства.