Устройство для контроля пакетных @ кодов

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике. Изобретение позволяет повысить достоверность пакетных t кодов. Устройство содержит п-разрядный регистр 1, злементы И 2, 3, 4, 8, элемент ИЛИ 5, блоки 6 и 7 индикации . 1 ил. 11 S (Л &0 vi 00

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51) 4 G 06 Р 11/00

g &

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

К ABTOPCHOMY СВИДЕТЕЛЬСТВУ (21) 3861539/24-24 (22) 28.02.85 (46) 28.02.8?. Бюл. Р 8 (72) А.В.Ткаченко и О.П.Гриб (53) 681.3(088.8) (56) Авторское свидетельство СССР

У 8!7718, кл. G 06 F 11/00, 1979.

Авторское свидетельство СССР

У 1149261, кл. G 06 Р 11/00, .1983. (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПАКЕТНЫХ

КОДОВ (57) Изобретение относится к вычислительной технике. Изобретение позволяет повысить достоверность пакетных кодов. Устройство содержит п-разрядный регистр 1, элементы И 2, 3, 4, 8, элемент ИЛИ 5, блоки 6 и 7 индикации. 1 ил.

129373

Изобретение относится к вычислительной технике и может быть использовано для контроля пакетных кодов.

Цель изобретения — повышение достоверности контроля.

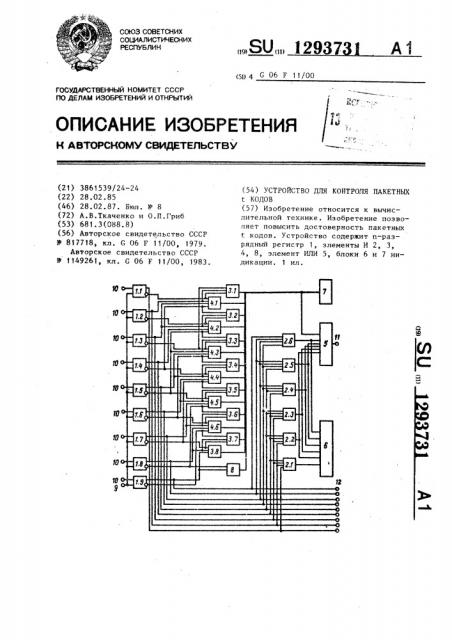

На чертеже представлена блок-схема устройства для и = 3.

Устройство содержит п-разрядные регистр 1, первую группу 4-входовых 10 элементов И 2, группу 3-входовых элементов И 3, вторую группу 4-входовых элементов И 4, элемент ИЛИ 5, первый б и второй 7 блоки индикации, элемент

И 8, вход 9 сброса устройства, ин- 15 формационные входы 10 устройства, выход 11 сбоя устройства и информационные выходы 12 устройства.

Устройство работает следующим образом. 20

Контролируемый код вводится через информационные входы 10 в п-разрядный регистр 1. Веса двоичнык пакетнык t кодов определяются следующим образом:

0 при п<0 25

1 при n (t

2 при п = t т

У 4(п — t — k) при и т t к=о

ЗО

B этом случае любое натуральное число может быть представлено двоичным кодом, содержащим пакеты из подряд идущих единиц, разделеннык одним или несколькими нулями. В данном устройстве фиксируется в каждой группе соседних разрядов отклонения от пакетной формы элементами И 2 в виде (t+1) единицы, элементами И 3 в виде (t-2) единицы, элементами И 4 в виде 40 (t-1}. единицы. При наличии одной из ,запрещенных комбинаций в контролируемом коде на выходе одного или нескольких элементов И возникает единичный сигнал, который индицируется в первом45

6 или втором У блоках индикации и через элемент ИЛИ 5 поступает иа выход сбоя устройства °

Формула изобретения

Устройство для контроля пакетных кодов, содержащее и-разрядный регистр, информационные входы разрядов

KoTQpoI о являются информационными входами устройства, а информационные выходы — информационными выходами устройства, вход сброса п-разрядного

1 2 регистра является входом сброса устройства, первую группу из (n-t) (t+1)-входовых элементов И, выходы котбрых подключены к соответствующим первым входам элемента ИЛИ и соответствующим входам первого блока индикации, второй блок индикации, входы которого соединены с соответствующими вторыми входами элемента ИЛИ, выход которого является выходом сбоя устройства, элемент И, первый вход которого подключен к прямому выходу п-ro разряда и-разрядного регистра, а выход - к соответствующему входу второго блока индикации, о т л и ч аю щ е е с я тем, что, с целью повышения достоверности контроля в него введены (t-2) группы m-входовых элементов И (m = 3, 4, ..., t) no (и-m+2) элемента в каждой и вторая группа из (n-t) (с+1} -входовых элементов И, первый вход i-го m-входового элемента И подключен к инверсному выходу i-го разряда п-разрядного регистра, j -ый выход (j = 2,3,...,(m-1)

j-ro m-входавого элемента И к прямому выходу (i+j-1) -го разряда и-разряднога регистра, последний вход

j ãî m âõîäîâîãî элемента И вЂ” к BH 1 верснаму выходу (i+m-1} -го разряда и-разрядного регистра, первый вход (и-ш+2} -го m-вхадового элемента И подключен к инверсному выходу (n m+1)-го разряда п-разрядного регистра, )-ый вход {j = 2, 3, ...,ш) (п-та+2) -го m-входового элемента Ик прямому выкоду (и-ш+)+1} -го разряда и-разрядного регистра, первый вход

i-го (с+1) -входового элемента И первой группы подключен к прямому, а второй группы — к инверсному выходу

i-го разряда и-разрядного регистра, j é вход (j = 2,3,...,t) i-ro (t+1)— входового элемента И первой и второй групп подключен к прямому выходу (i+j -1) -го разряда и-разрядного р егнстра, последний вход i-ro (t+1) входового элемента И первой группы . подключен к прямому, а второй группы — к инверсному выкоду (i+t)-го разряда п-разрядного регистра, второй вход элемента И подключен к инверсному выходу (n-1)-го разряда п-разрядного регистра„ выходы m-вхадовых элементов И и (t+1}-вхадовых элементов

И второй группы подключены к соответствующим входам второго блока индикации.