Декодирующее устройство для исправления пакетных ошибок

Иллюстрации

Показать всеРеферат

Изобретение относится к вычис- -лительной технике. Его использование в системах передачи и обработки цифровой информации позволяет повысить быстродействие устройс.тва. Декодирующее устройство для исправления пакетных ошибок содержит регистры 1 и 2 сдвига вычислитель 3 синдрома , блоки 4 и 5 ключей, ключи 6-30, анализатор i 1 синдрома и блок 12 управления . За счет введения блока 13 синхронизации, блока 14 селекции и блоков 15-17 ко в1утации исключается декодирование тех кодовых слов,в которых пакет ошибок не стоит в крайних левых ячейках вычислителя 3 синд- Q рома, т.е. исключены заведомо неудачные попытки декодирования, ф-лы, 6 ил. 1 3 .п. (Л tc со со 00 1 ел 941%. I

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

4 А1 (19) (11) (5)) 4 Н 03 М 13/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ASTOPCHOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3841520/24-24 (22) 07,01 ° 85 (46) 28,02,87, Бюл. У 8 (71) Ленинградский институт авиационного приборостроения (72) Г,С.Евсеев, 10.Т.Ефимов, Е.А,Крук, Д,N,Ëåðíåð, С.В,Семенов и Б.К,Трояновский (53) 681.32 (088.8) (56) Питерсон У,, Узлдон Е. Коды, исправляющие ошибки. М.: Мир, 1976, с. 213-218.

Касами Т и др, Теория кодирования. М.: Мир, !978, с. 403-405, Авторское снидетепьстно СССР

У 1185614. кл. Н 03 М 13/00, 1984. (54) ДЕКОДИРУКЩЕЕ УСТРОЙСТВО ДЛЯ

ИСПРАВЛЕНИЯ ПАКЕТНЫХ ОШИБОК (57) Изобретение относится к вычислительной технике. Его использование в системах передачи и обработ— ки цифровой информации позволяет повысить быстродейстние устройства. Декодирующее устройство для исправления пакетных ошибок содержит регистры 1 и 2 сдвига, вычислитель 3 синдрома, блоки 4 и 5 ключей, ключи 6-10, анализатор 11 синдрома и блок 12 управления, 3а счет введения блока 13 синхронизации, блока 14 селекции и блоков 15-17 коммутации исключается декодирование тех кодовых слон, в которых пакет ошибок не стоит в крайних левых ячейках вычислителя 3 синдрома, т.е. исключены заведомо не- . Е удачные попытки декодирования. l з.п. ф-лы, 6 ил.

С::

1 12938

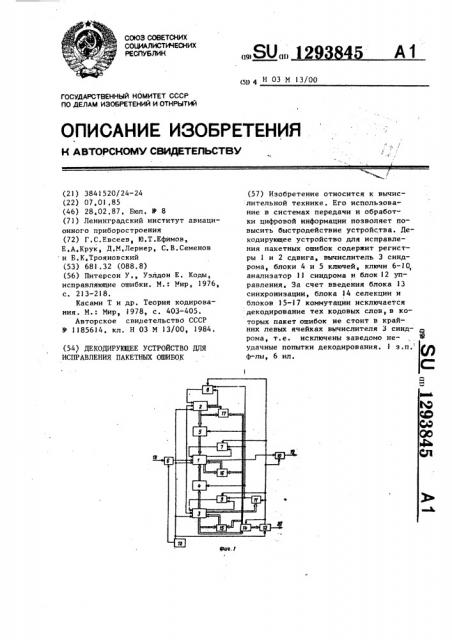

Изобретение относится к вычислительной технике и может быть использовано в системах передачи и обработки информации, Цель изобретения — повышение быстродействия устройства, На фиг,l приведена блок-схема декодирующего устройства для исправления пакетных ошибок на фиг.2— функциональная схема конкретного вы- !О полнения вычислителя синдрома; на фиг.3 — схема анализатора синдрома, на фиг.4 — схема блока синхронизации; на фиг .5 — возможная реализация функциональной схемы блока коммутации; на фиг.б — временные диаграммы рабаты блока управления, Декодирующее устройство для исправления пакетных ошибок содержит первый 1 и второй 2 регистры сдвига, вычислитель 3 синдрома, первый 4 и второй 5 блоки ключей, первый— пятый ключи 6 — 10, анализатор 11 синдрома, блок 12 управления, блок

13 синхронизации, блок 14 селекции, первый !5, второй 16 и третий 17 блоки коммутации, На фиг,l обозначены вход 18,информационный выход 19 и выход 20 синхронизации, Вычислитель 3 . синдрома представляет собой кодовый фильтр и для линейного циклического (15,9) -кода с порождающим многочленом g(z) = х6 + х + х + х + 1 выполнен (фиг. 2! на полусумматорах

2l и триггерах 22. На фиг.2 обозна- 35 чены первый 23, второ" 24 и третий

25 информационные входы, управляющий вход 26, первый 27 и вторые 28 выходы, На фиг,1 вторые выходы вычислителя 3 синдрома для удобства изоб- 40 ражения показаны в виде трех отдельных групп, Анализатор 11 синдрома (фиг,3) выполнен на блоке 29 ключей, |буферном регистре 30 и блоке 31 сравнения, На фиг,3 обозначены первые 32 и 45 вторые 33 входы и выход 34. Блок

13 синхронизации (фиг.4) выполнен на шифраторе 35, сумматоре 36, элементе ИЛИ 37, ключе 38 и счетчике

39, На фиг.4 обозначены первые 40 50 и второй 41 входы, первый 42 и второй 43 выходы. Блок 14 селекции представляет собой селектор, выходы которого соединены с информационными входами группы ключей, управляющие 55 входы которых объединены и являются вторым входом блока 14. Селектор служит для определения числа нулей справа от старшей значащей цифры в числе, подаваемом на первые входы блока, Он может быть реализован в виде логической схемы, каждый выход у, который связан с входами зависимостью у; х х ....х 1 i-1 1

Блоки 15 — 17 коммутации имеют одинаковое выполнение, например, как на фиг.5, где показаны группы 44 ключей, буферный регистр 45, информационные входы 46 и выходы 47, Управляющие входы ключей в каждой группе

44 (не показаны) объединены. Совокупность управляющих входов всех групп

44 является управляющими входами блока. Выходы всех групп 44 на входе регистра 45 объединяются на элементах ИЛИ, Блоки 16 и 17 содержат по п групп 44 ключей, где n — - разрядность входного кодового слова, Блок 15 содержит r групп 44, где r число проверочных символов кода.

Блоки 15 — 17 коммутации осуществляют циклическую перестановку подаваемых на их входы слов х, х,,х на i+ п-1 разрядов, Блоки !5 — !7 могут быть реализованы также с помощью оперативных запоминающих устройств (ОЗУ), Блок !2 управления представляет собой генератор тактовых импульсов, выход которого соединен с входом счетчика, выходы которого подключены к входам дешифратора.

Выходы последнего являются выходами блока 12 управления. Сигналы íà первом и втором входах блока !2 управленин приведены на фиг.б.

Декодирующее устройство для исправления пакетных ошибок работает следующим образом.

В исходном положении открыты первый б, второй 7, третий 8 и четвертый 9 ключи, ключ !О и блок 4 и 5 закрыты, первый I и второй 2 регистры сдвига и вычислитель 3 синдрома находятся в нулевом, а регистр 30 в анализаторе 11 синдрома — в единичном состоянии, блок 13 синхронизации находится в нупевом состоянии, 1, В режиме приема переданного слова с входа 18 п символом (и— длина используемого кода) последовательно поступают через открытый ключ 6 на первые информационные входы первого 1 и второго 2 регистров сдвига и вычислителя 3 синдрома, в которых одновременно осуществляются циклические сдвиги (ключи 7 - 9 отк1293845

50 рыты), Эти сдвиги управляются сигналами, поступающими на управляющие . входы регистров l и 2 сдвига и вычислителя 3 синдрома с первого выхода блока 12 управления. В результате через и тактов {и циклических сдвигов)принятое слово записывается в регистрах 1 и 2 сдвига, а синдром принятого слова — в вычислителе 3 синдрома, 2, После приема слова осуществляется режим декодирования. В этом режиме первый ключ б закрывается управляющим импульсом с второго выхода блока 12 управления, В режиме декодирова- 15 ния осуществляются следующие операции.

2,1, Символы синдрома с вторых выходов вычислителя 3 синдрома параллельно поступают на информационные входы анализатора ll синдрома и сравниваются в блоке 31 сравнения как двоичное число с числом, записанным в регистре 30. В случае, если число, поступающее с вторых. выходов вычислителя 3 синдрома на блок 31 сравнения строго меньше числа, поступающего с выхода регистра 30, на выходе блока 31 сравнения появляется импульс,.который одновременно открыва- 30 ет ключ 29 и выдается с выхода анализатора il синдрома, При открытом ключе 29 происходит в параллельном коде перепись содержимого вычислителя

3 синдрома в регистр 30. 35

2.2. Импульс с выхода анализатора 11 синдрома открывает блоки 4 и 5 ключей, закрывает ключи 7 — 9 и обнуляет содержимое второго регистра 2 сдвига. При закрытых ключах 7 — 9 це- 40 пи обратной связи регистров 1 и 2 сдвига и вычислителя 3 синдрома разрываются и содержимое вычислителя 3 синдрома подается на входы r (r число проверочных символов кода) ле- 45 вых разрядов первого регистра 1 сдвига, где складывается по модулю два с содержимым второго регистра 2 сдвига, 2,3, Символы синдрома с выходов вычислителя 3 синдрома параллельно поступают на информационный вход блока 14 селекции, в котором производится анализ поступающего синдрома. В результате этого анализа на выходе блока 14 появляется слово, содержащее ровно один нулевой символ, соответствующий числу . нулей, стоящих справа от старшего ненулевого разряда синдрома. Слово с выхода блока 14 селекции поступает на управляющие входы блоков 15 — 17 коммутации и инициирует сдвиг содержимого регистров

1 и 2 сдвига и вычислителя 3 синдрома на число позиций, равное числу нулей, находящихся справа от старшего ненулевого элемента в синдроме.

В результате операций, проведенных в пунктах 2.! и 2.2, в регистре 30 анализатора 11 синдрома будет записан синдром, являющийся минимальным арифметическим числом среди чисел, соответствующих построенным ранее синдромам, а в регистре 1 сдвига будет записан соответствующий этому синдрому вариант декодированного слова, Величина сдвига в и-й форме (в системе счисления по модулю и) поступает с вторых выходов блока 14 селекции на входы блока 13 синхронизации, где преобразуется в двоичную форму (в шифраторе 35) и складывается с содержимым сумматора Зб.

2,4, С первого выхода блока 12 управления на управляющие входы первого 1 и второго 2 регистров сдвига и вычислителя 3 синдрома поступает импульс, по которому производится циклический сдвиг содержимого первого

1 и второго 2 регистров сдвига и вычислителя 3 синдрома. Затем повторяются операции по пунктам 2.1-2.3. Пиклические сдвиги производятся до тех пор, пока с выхода сумматора Зб не появится импульс, соответствующий числу и, записанному в сумматоре (импульс переполнения), В результате этапа 2 в первом регистре I сдвига будет записан декодированный вариант принятого слова, 3, По окончании декодирования начинается этап вывода декодированного слова. Импульсом с первого выхода блока 13 синхронизации ключи 7—

9 закрываются, а ключ 10 открывается, За и тактов содержимое первого регистра 1 сдвига (декодированное слово) выдается в последовательном коде через открытый ключ 10 на выход

19 устройства, При этом содержимое первого 1 и второго 2 регистров сдвига и вычислителя 3 синдрома обнуля-, ется. После выдачи результата декодирования импульсы .с первого выхода блока 13 синхронизации устанавливают все ключи и ячейки памяти устройства в.исходное положение.

12938

Формула

Иэ пункта 2.3 следует, что в случае, когда пакет ошибок не стоит в крайних левых ячейках вычислителя 3 синдрома, анализ синдрома (декодирование) производиться не будет. Поскольку этому соответствуют заведомо неудачные попытки декодирования, то предлагаемое устройство имеет по сравнению с прототипом, в котором обязательно проводятся все и попыток

> кодирования, преимущественно по быстродейстнию, Оценки показывают, что выигрьпп по быстродействию по сравнению с .прототипом составляет 30—

407..

Таким образом, декодирующее устройство для исправления пакетных ошибок позволяет без ущерба для качества декодирования отказаться от проведения ряда попыток декодирования, К и тем самым повысить быстродействие устройства, изобретения

1. Декодирующее устройство для исправления пакетных ошибок, содержащее первый ключ, выход которого соединен с первыми информационными входами первого и второго регистров сдви- ЗО га и вычислителя синдрома, первые выходы которых соединены с информационными входами соответственно второго третьего и четвертого ключей, выходы которых подключены к вторым информационным входам соответственно первого и второго регистров сдвига и вычислителя синдрома, вторые выходы вычислителя синдрома и второго регистра сдвига подключены к соот- 4р ветствующим информационным входам соответственно первого и второго блоков ключей выходы которых соединены соответственно с третьими и четвертыми информационными входами первого регистра сдвига, второй выход которого соединен с информационным входом пятого ключа, блок управления и анализатор синдрома, выход которого соединен с управляющими входами блоков ключей и первыми управляющими входами второго, третьего и четвертого ключей, вторые управляющие входы которых объединены, вторые выходы вычислителя синдрома подключены к соответствующим информационным входам анализатора синдрома, первый выход блока управления подключен к управляющим входам первого и второго регистров сдвига и вычислителя синдрома, второй выход блока управления соединен с управляющим входом первого ключа, информационный вход которого является входом устройства, выход пятого ключа является информационным выходом устройства, о т л и ч а ю щ е е с я тем, что, с целью поньппения быстродействия устройства, в него введены блок селекции, блок синхронизации и блоки ком--мутации, выходы которых подключены соответственно к третьим информационным входам вычислителя синдромов, пятым информационным входам первого и третьим информационным входам второго регистров сдвига, вторые выходы вычислителя синдрома, третьи выходы первого и вторые выходы второго регистров сдвига подключены к соответствующим информационным входам соответственно первого, второго и третьего блоков коммутации, вторые выходы вычислителя синдрома соединены с первыми входами блока селекции, первые выходы которого подключены к соответствующим управляющим нходам блоков коммутации, вторые выходы блока селекции соединены с первыми входами блока синхронизации, первый выход которого соединен с вторым нхоpîì блока селекции, управляющими входами анализатора синдрома и пятого ключа и вторым управляющим входом . второго ключа, первый выход блока управления соединен с вторым входом блока синхронизации, второй выход которого является выходом синхронизации устройства.

2, Устройство по п.1, о т л и ч аю щ е е с я тем, что блок синхронизации выполнен на сумматоре, счетчике, ключе, элементе ИЛИ и шифраторе выхоцы которого подключены к соответствующим входам сумматора выход которого соединен с первым входом элемента ИЛИ и управляющим входом ключа, выход которого подключен к входу счетчика, выход которого соединен с вторым входом элемента

ИЛИ, входы шифратора и информационный вход ключа являются соответственно первым и вторым входами блока, выход элемента ИЛИ и выход счетчика являются соответственно первым и вторым выходами блока, ) 2938й5.Рд

pok8

1293845

Составитель О,Ревинский

Техред g . .Кадар Корректор М,Самборская

Редактор Э,Слиган

Закаэ 396/59

Тираж 902 Подписное

ВНИИПИ Государственного комитета СССР

lIo делам иэобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, r.Óærîðoä, ул.Проектная,4