Устройство для умножения

Иллюстрации

Показать всеРеферат

J9 )29390

Класс 42m, 14С С(. l

« союзно (:АТЕЕ г, 0.

ТГЛ Нц . Е С(. р. д

t .45 .tiЭ Т;: Ъ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Подписная группа М 174

М. А. Карцев

УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ

Заявлено 4 сентября 1959 г. за М 637953/2б в Комитет по делам изобретений и открытии при Совете Министров СССР

Опубликовано в «Бюллетене изобретений» No 12 за 1960 г.

Недостатком известных устройств для одновременного выполнения двоичного умножения (построенных на основе методов второго порядка ускорения умножения) является невозможность использования их оборудования при выполнении других действий.

Предлагаемое устройство для умножения может быть пспользованэ также и при выполнении деления олагодаря тому, что один из входов каждого сумматора соединен через вентили с прямым или инверсным выходом соответствующего разряда регистра множпмого (делнтеля), два других входа каждого сумматора соединены с выходами суммы и переноса сумматоров предыдущего ряда и в каждом ряду сумматоров имеется дешифратор сигналов управления, к входам которого присоединены сумматоры трех старших разрядов предыдущего ряда и соответствующий разряд множителя. Дешифратор управляет вентилями на входах сумматора данного ряда.

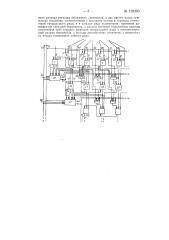

На чертеже представлена часть функциональной схемы устройства для умножения — старшие сумматоры трех первых рядов.

К сумматорам 1, 2, 8, 4, 5 первого ряда к входам 6, 7, 8, 9, 10 присоединены прямые выходы регистра делимого (числа, к которому должно быть добавлено произведение). Дешифратор сигналов управления в первом ряду сумматоров отсутствует, а вентили «И» 11, 12, .18, 14 управляются сигналом «деление», который поступает от схемы управления на вход 15 устройства. Другие входы этик вентилей присоединены к инверсным выходам регистра множимого (делителя) 16, 17, 18, 19. Выходны" сигналы вентилей присоединены ко вторым входам 20, 21, 22 и 28 сумматоров первого ряда. К третьему входу 21 сумматора 1 присосдиYåí выход переноса сумматора 2, а третьи входы ocTBJlbHbIy сумматоров первого ряда (входы 25, 26, 27, 28) не задействованы. Быходы 29, 80 п

81 сигналов переноса и выходы 82, 88 и 84 сигналов суммы старших разрядов первого ряда присоединены к входам дешифратора 85 сигналов управления второго ряда. Кроме того, выходы суммы и переноса сумМ 129390 мяторов перВОГО ряда соединены со входами сумматоров 8.>,, и второго ряда; входы 40 и 41 сумматора 86 соединены с выходом 83 сигнала суммы сумматора 2 и выходом 80 сигнала переноса сумматора и т. д. (до конца ряда). В сумматоре 86 один из входов (42) соединен с выходом переноса сумматора 87, а в остальных сумматорах второго ряда аналогичные входы 43, 44, 45 соединены с выходами вентилей 46, 47, 48. Вентили здесь, как и в последующих рядах, представляют собой л >гическис схемы «И — ИЛИ». На эти схемы поступают инверсные цифры множимого (делителя) со входов 16, 17, 18, 19 и прямые цифры —::о входов 49, 50, 51. Вентили управляются выходными сигналами дешифратора 85, так что при наличии сигнала «-;-» (на выходе 52 дешифрятора) вентили пропускают прямые цифры множителя (делителя), ири наличии сигнала « — » (на выходе 5> дешифратора) — инверсные цифры. а при отсутствии обоих этих сигналов на выходах вентилей получаются нули. Кроме того, на входы дешифраторов поступают сигналы «деление» (с входа 15), «умножение» (с входа 54), а также сигналы цифр соОтветствующих разрядов множителя — с входов 55, 56 и т. д Во все; последующих рядах соединения аналогичны второму ряду. с той лишь разницей, что на один из входов дешифратора сигналов управления до. полнительно вводится сигнал «--» с дешифратора предыдущего ряд 1 (например, B дешифратор 57 третьего ряда введен сигнал с выхода 5« дсшифратора 85 второго ряда и т. д.).

При выполнении умно>кения дешифратор сигналов управления вырабатывает сигнал «+», если соответствующая цифра множителя есг, «1», и не вырабатывает никаких сигналов, если «0». Поэтому каждый из рядов сумматоров добавляет очередное частичное произведение к сумме предыдущих произведении; результат при этом получается в виде суммы двух чисел (на выходах сумм и переноса сумматоров данного ряда). Окончательное произведение тоже получается в виде двух чисел, появляющихся ня выходах стярши" с ммяторов каждого ряда. ОднО и. чисел — па г:ыходах 32, 58, 59 и т. д., другое — на выходах 60, 61 и т. ч.

Эти числа в конце операции складываются дополнительным рядом сумматоров, который на чертеже не показан.

При выполнении деления первый ряд сумматоров всегда вычитает из делимого делитель. В каждом из последующих рядов дешифратор сигналов управления анализирует четыре старшие разряда предыдущего остатка (без учета переносов из младших разрядов). Если чис|О представленное этими разрядами, неотрицатсльно, то Очсредня,l цифра частного есть «+1», и дешифратор выдает на вентили сигнал « — »; если это число отрицательно, но не равно — /4, то цифра частного есть « — 1.>, на вентили Выдается сигнал «+»: сели это число равно —,/4, то цифра частного есть «0», на вентили никакие сигналы не выдаются. Окончательно частное получается при помощи дополнительного ряда суммато— ров (того же, что при умножении) как разность двух чисел; первое из них содержит «1» в старшем разряде и «1» в тех разрядах, где дешифраторы выдают сигналы « — »; второе число (вычитаемое) сп.иржит «1,: в тех разрядах, где дешифраторы дают сигналы «- -;>, Предмет изобретения

Устройство для умножения двух п-разрядных двоичных чисел, содср>кащее m+1 ряд сумматоров, Отл ич я ющеее я тем, что, с целью его использования для выполнения операции деления без существенного снижения быстродействия, один из входов каждого сумматора соединен через вентили с прямым или инверснь1м вы;;одом соответствую— 3—

¹ 129390 щего разряда регистра множимого (делителя), а два других входа сумматора соединены соответственно с выходами суммы и переноса сумматоров предыдущего ряда, и в каждом ряду сумматоров применен дешифратор сигналов управления, к входам которого подключены выходы сумматоров трех старших разрядов предыдущего ряда и соответствуюIII HH разряд множителя, а Bblxo+bl дешпфратора cop+HHE HI I c венти IIHXIH на входах сумматоров данного ряда.