Импульсный стабилизатор постоянного напряжения

Иллюстрации

Показать всеРеферат

Изобретение относится к вторичным источ1шкам питания радиоаппаратуры . Целью изобретения является повышение качества выходного напряжения стабилизатора при коммутации потребитрлей со скачкообразным изменением тока нагрузки за счет синхронизации моментов подключения и отключения потребителя 20 с моментами соответственно размыкания и замыкания ключевого элемента 1 стабилизатора. Для синхронизации используется логическая схема, содержащая три D-триггера 11- 13, два элемента И 14 и 15, элемент НЕ 17, элемент ИЛИ 16, два компаратора 7 и 8 и элемент 18 управления. Логическая схема определяет момент размыкания ключевого элемента 1 стабилизатора и.при наличии сигнала на подключение потребителя 20 с элемента управления переводит транзисторный ключ 19, обеспечивающий коммутацию потребителя 20, в открытое состояние в тот же момент. Этим достигается уменьшение провала напряжения на выходе стабилизатора. Аналогично уменьшается выброс напряжения при отключении потребителя 20. 1 ил. е (Л с: ю со ел САЭ СО

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (11) А1 (51) 4 С 05 F 1/56 и И ф

) ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCHGMV С8ИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

;(21) 3965790/24-07 (22) 22.10.85 (46) 07.03.87. Бюл. Ф 9 (71) Челябинский политехнический институт им. Ленинского комсомола (72) В.В.Злакоманов, Л.А.Озеров, О.А.Разнополов и Н.Е.Терентьев (53) 621.316.7.22.1(088.8) (56) Источники вторичного электропитания./Под ред. 10.И.Конева. — M.:

Радио и связь, 1983, с. 150, рис.4.1.

Букреев С.С. Силовые электронные устройства. — M.: Радио и связь, 1982, с. 197, рис. 11.9. (54) ИМПУЛЬСНЫЙ СТАБИЛИЗАТОР ПОСТОЯННОГО НАПРЯЖЕНИЯ (57) Изобретение относится к вторичным источникам питания радиоаппаратуры. Целью изобретения является повышение качества выходного напряжения стабилизатора при коммутации потребителей со скачкообразным изменением тока нагрузки за счет синхронизации моментов подключения и отключения потребителя 20 с моментами соответственно размыкания и замыкания ключевого элемента 1 стабилизатора. Для синхронизации используется логическая схема, содержащая три D-триггера 11—

13, два элемента И 14 и 15, элемент

НЕ 17, элемент ИЛИ 16, два компаратора 7 и 8 и элемент 18 управления. Логическая схема определяет момент размыкания ключевого элемента 1 стабилизатора и .при наличии сигнала на подключение потребителя 20 с элемента управления переводит транзисторный ключ 19, обеспечивающий коммутацию потребителя 20, в открытое состояние в тот же момент. Этим достигается уменьшение провала напряжения на выходе стабилизатора. Аналогично уменьшается выброс напряжения при отключении потребителя 20. 1 ил.! 12953

Изобретение относится к электротехнике и может быть использовано во вторичных источниках питания автономных систем электроснабжения °

Целью изобретения является повьппеwe динамической стабильности выходного напряжения стабилизатора при скачкообразном изменении тока нагрузки в моменты коммутации потребителей путем синхронизации моментов подклю- !О чения и отключения потребителя с моментами замыкания и размыкания ключевого элемента.

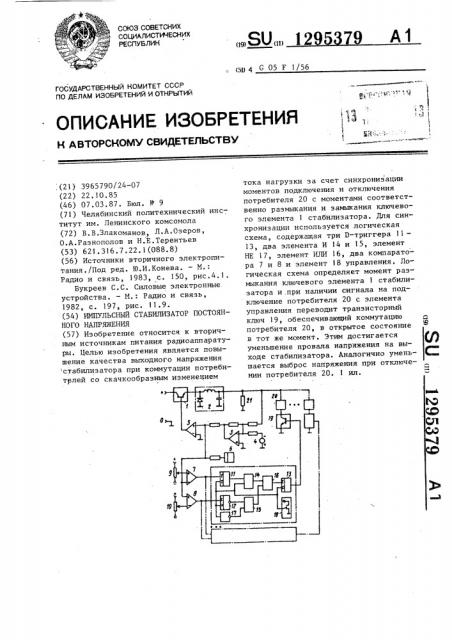

На чертеже приведена функциональная схема импульсного стабилизатора постоянного напряжения.

Устройство содержит ключевой элемент 1, DLC-фильтр 2, усилитель 3 рассогласования, источник 4 эталон- 20 ного напряжения, компаратор-модулятор 5, генератор 6 пилообразного напряжения, компараторы 7 и 8, делители

9 и 10 напряжения три D-триггера 11—

13, логические элементы И 14 и 15 ло- 25 гический элемент ИЛИ 16, элемент НЕ

17, управляющий элемент 18 коммутации нагрузки, транзисторный ключ 19, коммутируемый потребитель 20 энергии (нагрузка), постоянный потребитель 3О

21. По командам управляющего элемента 18 коммутации нагрузки транзисторный ключ 19 переходит в открытое или закрытое состояние, что соответствует подключению или отключени!и лотре- 35 бителя 20 ° При этом в моменты времени, в которые необходимо произвести подключение или отключение потребителя 20, формируются сигналы управления в виде положительных перепадов щ выходных напряжений компараторов 7 и 8, соединенных входами с входом компаратора-модулятора 5. Два Dтриггера 11 и 12 своими С-входами соединены с выходами компараторов 7 и 8, Входы D-триггеров ll и 12 соединены с выходом управляющего элемента 18 коммутации нагрузки, а выходы триггеров ll (прямой) и 12 (инверсный) подключены к первым входам элементов И 14 и 15, вторые входы которых соединены с выходом управляющего элемента 18 коммутации нагрузки, причем элемент И 15 — через элемент НЕ 17. Выходы элементов И 14 и 15 подключены к входам элемента

ИЛИ 16, выход которого соединен с

С.-входом D-триггера 13. D-вход З— триггера 13 подключен к выходу управ79 2 ляющего элемента 18 коммутации нагрузки. Триггер 13 своим выходом соединен с входом управпения транзисторного ключа 19. При высоком уровне напряжения на выходе триггера !3 транзисторный ключ 19 открыт. При низком уровне напряжения на выходе триггера 13 транзисторный ключ 19 закрыт.

Импульсный стабилизатор постоянного напряжения работает следующим образом, В установившемся режиме работы компаратор-модулятор 5 переключается с частотой генератора 6 пилообразного напряжения, обеспечивая поддержа" ние на выходе стабилизатора постоянного напряжения заданного уровня.

Двойная амплитуда пульсации тока дрбсселя имеет при этом значение ьТ . Компараторы 7 и 8 переключаются в моменты, близкие к моментам переключения компаратора-модулятора 5.

Импульсы с выходов компараторов 7 и

8 поступают на С-входы триггеров ll и 12. На выходе управляющего элемента коммутации нагрузки присутствует нулевой сигнал, что соответствует отключенному состоянию коммутируемого потребителя 20.

Логический "0" с управляющего элемента 18 поступает íà D-входы триггеров 11 и 12. В результате поступления на С-входы триггеров 11 и 12 импульсов с компараторов 7 и 8 они принимают ранее выходные состояния:

"0" — триггер 11 (прямой выход), "1" — триггер 12 (инверсный выход).

На оба входа элемента И 14 поступают

"0" и на его выходе, таким образом, имеется "0". На входы элемента И 15 поступают сигналы "1". При наличии двух "1" на входах элемента И 15 на

его выходе устанавливается "!". С выхода элемента И 15 "1" поступает на второй вход элемента ИЛИ 16, выходной сигнал которого также принимает значение "!". При первом появлении "1" на выходе элемента ИЛИ 16 триггер 13 переписывает "0" с управляющего элемента 18 на свой выход.

На выходе триггера 13 устанавливается "0", который подается на вход управления транзисторным ключом 19.

При этом транзисторный ключ 19 заперт, а нагрузка 20 отключена от выходных шин предлагаемого стабилизатора.

3 12

При включении потребителя 20 управляющий элемент 18 переводится в состояние "Включить нагрузку". При этом на его выходе появляется положительный потенциал, соответствующий, логической "l". Логическая "1" с управляющего элемента 18 поступает одновременно на D-входы триггеров 11

l3 на элемент НЕ 17 и на второй вход элемента И 14. В результате на выходе элемента HE 17 появляется логический "0", который поступает на второй вход элемента И 15 и переводит его выход в состояние "0". Логический "0" с выхода элемента И 15 поступает на второй вход элемента ИЛИ 16 и также переводит его выходное состояние в 0". На этом заканчивается подготовка схемы к подключению потребителя 20.

В момент переключения компаратормодулятор 5 переключается, работающий с ним в противофазе компаратор 7 изменяет свое выходное состояние с

"0" на "1", компаратор 8 при этом переключается из "1" в "0" ° Положительный перепад напряжения с выхода компаратора 7 поступает на С-вход триггера ll, который переписывает

"1" с D-входа на свой выход. Логическая "1" с выхода триггера 11 поступает на первый вход элемента И 14 и, так как на втором входе элемента

И 14 уже имеется "1",. на выходе элемента И 14 появляется "1". Появление

"1" на выходе элемента И 14 воспринимается триггером 13 как положительный перепад, триггер 13 переписывает

"1" на свой выход и переводит транзисторный ключ 19 в открытое состояние. Тем самым потребитель 20 подключается к выходу в момент времени, соответствующий максимальному значению тока дросселя DLC-фильтра.

Одновременно компаратор-модулятор

5 переходит из состояния "0" в состояние "1", компаратор 7 — из "1" в

"0", а компаратор 8 — из "0" в "1".

Триггер ll при этом не изменяет своего состояния, а триггер 12 переходит в состояние "0". После этого схема приходит в устойчивое состояние, при котором триггер 13 удерживается в состоянии "1", что соответствует открытому состоянию транзисторного ключа 19 и подключенному состоянию потребителя 20, Поступающие с компарато95379 4 ров 7 и 8 импульсы уже не могут изменить состояние триггеров 11 и 12.

Для отключения потребителя 20 на выходе управляющего элемента 1 8 формируется логический "0"; который поступает на D-входы триггеров 11 -13, элемента И 14 и элемента НЕ 17. Элемент НЕ 17 переходит в состояние "1", элемент И 14 — в состояние "0", а

10 элемент И 15 не изменяет своего сос.тояния. После появления "0" на выходе элемента И 14 на входах элемента

ИЛИ 16 имеются уже два "0". На выходе элемента ИЛИ 16 также появляется "0".

Данное состояние логической схемы сохраняется до прихода первого положительного перепада (О-1) с компаратора 8 на вход триггера 12.

Триггер 12 переходит в состояние "1". Логическая "1" с выхода. триггера 12 поступает на первый вход элемента И 15, на втором входе которого уже имеется "1". В результате на выходе элемента И 15 появляется

"1", которая через элемент ИЛИ 16 поступает на триггер 13. Триггер 13 переписывает "0" с D-входа на выход.

При появлении на выходе триггера 13

"О" транзисторный ключ 19 переводится в закрытое состояние и потребитель 20 отключается.

В следующий момент времени происходит новое переключение компараторов 5, 7 и 8. При этом триггер 11 изменяет состояние выхода с "1" на

"0". После того состояние выходов элементов логической схемы не меняется. Данные состояния логических элементов соответствуют отключенному потребителю 20 и являются начальными к моменту нового подключения потребителя 20.

Таким образом, два дополнительных компаратора 7 и 8, элементы 11 — 17, элемент 18 управления и транзисторный ключ 19 позволяют подключать и отключать потребитель 20 в моменты, близкие к моментам размыкания и замыкания ключевого элемента 1 соответственно. Для корректировки моментов переключения компараторов 7 и 8 с целью компенсации временной задержки прохождения фронтов импульсов через схему логики введены два делителя 9 и 10 напряжения, ко орые изменяют пороговые напряжения срабатывания компараторов в небольших пределах от

Ф 129 потенциала земли и обеспечивают синхронное переключение ключевого элемента 1 и транзисторного ключа 19.

В результате предлагаемой коммутации потребителя 20 отсутствует переходный процесс по напряжению на выходе стабилизатора при токах нагрузки, равных или меньших двойной амплитуде тока дросселя DLC-фильтра hI . А при коммутациях потребителя 20 с токами больше 6I значительно снижается амплитуда переходного процесса по напряжению, в результате повышается качество напряжения на выходе предлагаемого стабилизатора. формула изобретения

Составитель Ю.Опадчий

Техред JI.Ñåðäþêoâà Корректор М.Пожо

Редактор И.Шулла

Тираж 864 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ б17/54

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

При наличии других потребителей

Со скачкообразным изменением тока нагрузки схема стабилизатора может наращиваться блоками управления коммутацией этих потребителей и соответСтвующими силовыми транзисторными ключами (дополнительные блоки управления, потребители, ключи и цепи их подключения показаны пунктиром);

Импульсный стабилизатор постоянного напряжения, содержащий последовач тельно включенные между входными н выходными клеммами ключевой элемент и DLC-фильтр, усилитель рассогласования, входами подключенный к источнику эталонного напряжения и выходным клеммам, а выходом совместно с выходом генератора пилообразного напряжения соединенный с выходом компаратора-модулятора, выход которого подсое5379 Ь динен к управляющему входу ключевого элемента, отличающийся тем, что, с целью повышения динамической стабильности выходного напря5 жения стабилизатора при коммутациях потребителя со скачкообразным изменением тока путем синхронизации моментов подключения и отключения потребителя с моментами замыкания и размыка10 ния ключевого элемента, он снабжен двумя компараторами, двумя делителями напряжения, тремя 17 -триггерами, двумя логическими элементами И, элементом ИЛИ, элементом НЕ, управляю15 щим элементом коммутации нагрузки и транзисторным ключом и клеммами для подключения коммутируемой нагрузки, причем соединенные вместе разноименные входы компараторов соединены с

20 входом компаратора-модулятора и с выходами делителей напряжения, выходы компараторов соединены с С-входами первого и второго D òðèããåðîâ, выходы которых соединены с первыми входами элементов И, а выходы элементов И соединены- с входами элемента

ИЛИ, выход которого соединен с 37— входом третьего триггера, выход которого соединен с управляющим входом

30 транзисторного ключа, электроды которого последовательно с клеммами для подключения коммутируемой нагрузки подсоединены к выходным клеммам, при этом управляющий элемент коммутации нагрузки своим выходом соединен с 7-входами триггеров, с вторым входом одного элемента И и через элемент НЕ с вторым входом второго элемента И.