Логический анализатор

Иллюстрации

Показать всеРеферат

Изобретение относится к области вычислительной техники и может быть использовано при диагностике цифровых блоков. Цель изобретения - повышение достоверности контроля. Логический анализатор содержит триггер, формирователь импульсов, интегратор, элемент И, сумматор по модулю два, регистр сдвига и блок индикации. С помощью сумматора по модулю два и регистра сдвига формируется сигнатура,. входной последовательности, поступающей на вход сумматора по модулю два через интегратор, который не пропускает узкие сигналы помех. Тактирующие импульсы для регистра сдвига формирует формирователь импульсов из входной информационной последовательности . Если расстояние между двумя соседними изменениями входного информационного сигнала больше постоянной времени интегратора, импульсы формируются при каждом изменении информационного сигнала. Если расстояние между двумя соседними изменениями информационног о сигнала меньше постоянной времени интегратора, то импульс формируется только по первому изменению информационного сигнала. Логический анализатор позволяет благодаря этому учитывать при формировании сигнатуры узкие сигналы, Что повышает достоверность контроля. 1 ил. i (Л ю со ел со

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (И) А3 (5D 4

Щ(Г

1

" й<)

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЬ1Й КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И OTHPblTHA (21) 381 3589/24-24 (22) 10.ll.84 (46) 07.03.87. Бюл. lt 9 (72) А.П.Смирнов (53) 681.3(088.8) (56) Авторское свидетельство СССР

ll 890396, кл. С 06 Р ll/00, 1980.

Авторское свидетельство СССР

Ф 1146677, кл. С 06 F 11/00, 1983. (54) ЛОГИЧЕСКИЙ АНАЛИЗАТОР (57) Изобретение относится к области вычислительной техники и может быть использовано при диагностике цифровых блоков. Цель изобретения — повышение достоверности контроля ° Логический анализатор содержит триггер, формирователь импульсов, интегратор, элемент И, сумматор по модулю два, регистр сдвига и блок индикации. С помощью сумматора по модулю два и регистра сдвига формируется сигнатура входной последовательности, поступающей на вход сумматора по модулю два через интегратор, который не пропускает узкие сигналы помех. Тактирующие импульсы для регистра сдвига формирует формирователь импульсов из входной информационной последовательности. Если расстояние между двумя соседними изменениями входного информационного сигнала больше постоянной времени интегратора, импульсы формируются при каждом изменении информационного сигнала. Если расстояние между двумя соседними изменениями информационного сигнала меньше постоянной времени интегратора, то импульс формируется только по первому изменению информационного сигнала.

Логический анализатор позволяет благодаря этому учитывать при формировании сигнатуры узкие сигналы, Что повышает достоверность контроля. 1 ил.

1295396

Изобретение относится к вычислительной технике и может быть испопьзовано при диагностике цифровых бпоков.

Целью изобретения является повыше.. ние достоверности контроля.

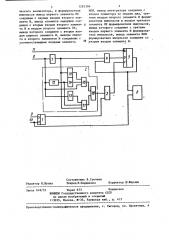

На чертеже приведена функциональная схема логического анапизатора.

Логический анализатор содержит триггер 1, формирователь 2 импульсов, элемент И 3, сумматор 4 по модулю два, регистр 5 сдвига, блок 6 чндикации, интегратор 7, информационный вход 8 логического анализатора, входы 9 и 10 соответственно начала и конца контроля логического анализато ра, установочный вход 11 логического анализатора, элемент 12 задержки, элементы HE 13-15, элементы И 16 и

17 и элемент ИЛИ 18 формирователя 2 импульсов.

Логический анализатор работает следукицим образом.

Единичный сигнал, поступающий на вход 9 начала контроля логического анализатора, устанавливает в единичное состояние триггер 1, который разрешает прохождение сигналов с выхода формирователя 2 импульсов через . элемент И 3 на тактирующий вход регистра 5 сдвига. Регистр 5 сдвига предварительно устанавливается . в исходное состояние по установочному входу ll логического анагжзатора.

Формирователь 2 импульсов формирует импульсы при изменениях входного информационного сигнала, поступающего на вход 8 логического анализатора. Информационные сигналы через интегратор 7 поступают на вход сумматора 4 по модулю два, с выхода которого идут на информационный вход регистра 5 сдвига, на последнем формируется сигнатура информационной последовательности.

Интегратор 7 не пропускает на регистр 5 сдвига узкие импульсы, длительности которых меньше постояннои времени интегратора 7. Совокупность элемента 12 задержки, элементов НЕ

14 и 15 и первого элемента И 16 формирователя 2 импульсов вырабатывает импульс при изменении входного сигнала от нулевого значения к единичному, а совокупность элемента 12 задержки, первого элемента НЕ 13 и второго элемента И 17 формирователя 2 импульсов — импульс при изменении

Формула изобретения

Логический анализатор, содержащий триггер, элемент И, формирователь импульсов, сумматор по модулю два, регистр сдвига и блок индикации, причем единичный вход триггера является входом начала контроля логического анализатора, нулевой вход триггера объединен с входом записи блока индикации и является входом конца контроля логического анализатора, прямой выход триггера соединен с первым. входом элемента И, выход которого соединен с тактирующим входом регистра сдвига, группа информационных выходов которого соединена с группой информационных входов блока индикации и группой входов сумматора по модулю два, выход которого соединен с информационным входом регистра сдвига, установочный вход регистра сдвига явля1 ется установочным входом логического анализатора, отличающийся тем, что, с целью повышения достоверности контроля, в него введен интегратор, формирователь импульсов содержит элемент задержки, при элемента НЕ, два элемента И и элемент ИЛИ, причем информационный вход интегратора объединен с первым входом первого элемента И формирователя импульсов, входом первого элемента НЕ формирователя импульсов, входом элемента задержки формирователя импульсов и подключен к информационному входу srora-: входного сигнала от единичного значения к нулевому.

Благодаря введению интегратора 7 сигнал на выходе формирователя 2 импульсов появляется по переднему и заднему фронтам информационного сигнала, если длительность этого сигнала больше постоянной времени интегратора 7, и только по переднему фронту, если длительность входного сигнала меньше постоянной времени интегратора 7. Длительность сигналов на выходе формирователя 2 импульсов не превышает величины элемента 12 задержки.

Сигнал, поступающий на вход 10 конца контроля логического анализатора, устанавливает в нулевое состояние триггер 1 и записывает в блок

6 индикации содержимое регистра 5 сдвига (сигнатуру). По сигнатуре определяется правильность работы контролируемого объекта.

Составитель В.Гречнев

Техред Л.Сердюкова

Корректор М.Шароши

Редактор И.Шулла

Заказ 618/55

Тираж 673 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

3 12953 ческого анализатора, в формирователе импульсов выход первого элемента НЕ соединен с первым входом второго элемента И, выход элемента задержки сое- . динен е вторым входом второго элемен- 5 та И и входом второго элемента НЕ, выход которого соединен с вторым входом первого элемента И, выходы первого и второго элементов И соединены с соответствующими входами элемента

ИЛИ. выход интегратора соединен с входом сумматора по модулю два, третьим входом второго элемента И формирователя импульсов и входом третьего элемента НЕ формирователя. импульсов, вы1сод которого соединен с третьим входом первого элемента И формирователя импульсов, выход элемента ИЛИ формирователя импульсов соединен со

;вторым входом элемента И.