Устройство для тестового контроля цифровых узлов электронных вычислительных машин

Иллюстрации

Показать всеРеферат

Изобретение относится к области цифровой вычислительной техники, может быть использовано в аппаратуре автоматического контроля и диаг- . ностики узлов ЭВМ и является усовершенствованием изобретения по авт.св. № 694863. Целью изобретения является повышение быстродействия. Устройство содержит формирователь 4 теста, блок 5 управления, коммутаторов 6, блок 7 сравнения, регистр 8 сдвига. Коммутатор 6 связан с контролируемым объектом 11. Для достижения цели в устройство введены регистр 9 и делитель 10 частоты, позволяющие программно задавать момент сравнения реакций объекта с эталоном, .который может меняться в зависимости от типа контролируемого объекта и типа тестового воздействия. 3 ил. (Л 0

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

i РЕСПУБЛИК (19) (И) (Sl) 4 С 06 F l l/22

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР пО делАм изоБРетений и ОтнРытий (61) 694863 (21) 3837893/24-24 (22) 04.01.85 (46) 07.03.87. Бюл. У 9 (71) Новосибирский электротехнический институт (72) Л.A.Àêóëüøèèà, Ю.Ф.Ерофеев, П.И.Унру и О.В.Иалявко (53) 681. 3 (088. 8) (56) Авторское свидетельство СССР

У 694863, кл. G 06 F 11/22, 1976. (54) УСТРОЙСТВО ДЛЯ ТЕСТОВОГО КОНТ° РОЛЯ ПИФРОВЫХ УЗЛОВ ЭЛЕКТРОННЫХ ВЫЧИСЛИТКЛЬНЫХ МАШИН (57) Изобретение относится к области цифровой вычислительной техники, может быть использовано в аппаратуре автоматического контроля и диагностики узлов ЭВМ и является усовершенствованием изобретения по авт. св.

У 694863. Целью изобретения является повышение быстродействия. Устройство содержит формирователь 4 теста, блок

5 управления, коммутаторов 6, блок

7 сравнения, регистр 8 сдвига. Комму-. татор 6 связан с контролируемым объектом 11. Для достижения цели в устройство введены регистр 9 и делителй

10 частоты, позволяющие программно задавать момент сравнения реакций объекта с эталоном, .который может меняться в зависимости от типа контролируемого объекта и типа тестового воздействия. 3 ил.

1295400

Изобретение относится к цифровой вычислительной технике, может быть использовано в аппаратуре автоматического контроля и диагностики узлов

ЭВИ и является усовершенствованием известного устройства по авт, св.

I1 694863.

Целью изобретения является повышение быстродействия.

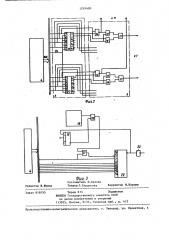

На фиг.l приведена схема устройства; на фиг.2 — структура блока управления и коммутатора; на фиг.3 — вариант структуры делителя-частоты с регистром.

Устройство для тестового контроля цифровых узлов. электронных вычислительных машин содержит запоминающий блок 1, блок 2 записи информации, регистр 3 теста, образующие формирователь 4 теста, блок 5 управления, коммутатор 6, блок 7 сравнения, регистр

8 сдвига, регистр 9,делитель 10 частоты, контролируемый узел 11, блоки триггеров 12 и 13, элементы И-НЕ 14, элементы И 15 и l6,элементы ИЛИ 17, триггер 18, генератор 19 импульсов, элемент И 20, элемент ИЛИ 21, делитель 22 частоты с переменным коэффициентом деления, выполненный на интегральной схеме ИЕ 8, элемент НЕ 23.

В качестве формирователя 4 теста мои жет быть применена ЭВМ Электроника 60".

Устройство работает следующим образом.

Тестовая информация, хранящаяся в формирователе тестов, поступает на шину данных. Структура теста такова: тест состоит из двух частей — заголовка и последовательности кадров.

Заголовок теста — это информация о распределении выводов контролируемого узла 11, Калдый кадр теста содержит стимулирующее слово для контролируемого узла и эталлонное слово (эталлонное значение выходов контролируемого узла). Если задержка фиксации результата предыдущего шага проверки отличается от текущего, то кадр теста содержит командное слово для делителя 10 частоты, Работу устройства можно разбить на два этапа: первый — настройка

5О отличающееся тем, что, с целью повышения быстродействия, в него введены регистр и делитель частоты, причем группа информационных входов регистра соединена с выходами разрядов кода задержки регистра теста, выходы регистра соединены с настроечными входами делителя частоты, выход которого соединен с разрешающим входом блока сравнения, синхровход блока управления, вход записи регистра, вход запуска делителя частоты и синхровход регистра сдвига соединены с выходами командных разрядов регистра теста. блока управления, второй — пошаговое тестирование.

На первом этапе в блок 5 по сигналу на линии 24 записывается заголовок теста, Блок 5 вырабатывает в парафазном коде сигналы управления коммутатором 6 и определяет входные и выходные контакты контролируемого узла 11. Затем начинается второй этап контроля.

Устройство на отдельном шаге тестирования работает следующим образом.

По управляющему сигналу на линии

25 производится запись командного слова в регистр 9. Формирователь 4 выводит на шину данных стимулирующее слово, которое через коммутатор 6 передается на входы контролируемого узла Il, и выдает сигнал на линию 26 в делитель 10 частоты, по которому он вырабатывает сигнал управления фиксацией спустя некоторое время, соответствующий значению слова в регистре 9, По управляющему сигналу делителя 10 в блоке 7 сравнения происходит фиксация отклика контролируемого узла. Далее формирователь 4 выводит на шину данных эталонное слово, которое поступает на блок 7 сравнения через коммутатор 6.

По сигналу на линии 27 результат сравнения записывается в регистр 8 сдвига.

Формула изобретения

Устройство для тестового контроля цифровых узлов электронных вычислительных машин по авт. св. 9 694863, 1295400

Корректор М.Шароши

Техред Л.Сердюкова

Редактор И.Шулла

Тираж 673 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 618/55

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4