Устройство для отладки программ

Иллюстрации

Показать всеРеферат

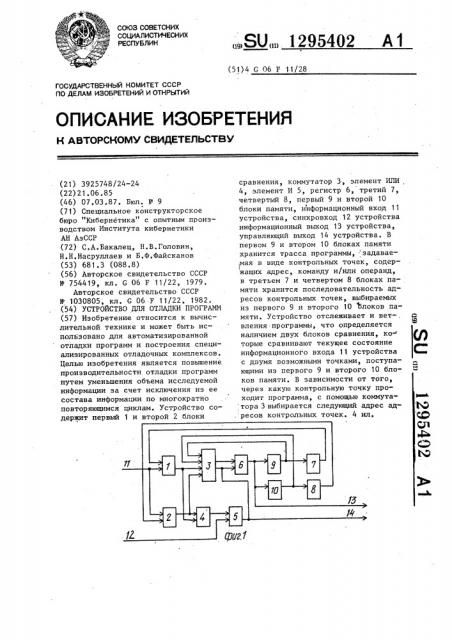

Изобретение относится к вычислительной технике и может быть использовано для автоматизированной отладки программ и построения специализированных отладочных комплексов. Целью изобретения является повьшение производительности отладки программ путем уменьшения объема исследуемой информации за счет исключения из ее состава информации по многократно повторяющимся циклам. Устройство содержит первый 1 и второй 2 блоки сравнения, коммутатор 3, элемент ИЛИ 4, элемент ИЗ, регистр 6, третий 7, четвертьй 8, первый 9 и второй 10 блоки памяти, информационный вход 11 устройства, синхровход 12 устройства информационньй выход 13 устройства, управляющий выход 14 устройства. В первом 9 и втором 10 блоках памяти хранится трасса программы, задавае- ,мая в виде контрольных точек, содержащих адрес, команду и/или операнд, в третьем 7 и четвертом 8 блоках памяти хранится последовательность адресов контрольных точек, выбираемых из первого 9 и второго 10 Ълоков памяти . Устройство отслеживает и вет-. вления-программы, что определяется наличием двух блоков сравнения, которые сравнивают текущее состояние информационного входа 11 устройства с двумя возможными точками, поступающими из первого 9 и второго 10 блоков памяти. В зависимости от того, через какую контрольную точку проходит программа, с помощью коммута- ;тора 3 выбирается следующий адрес ад- . ресов контрольных точек. 4 ил. с (Л с to со ел 4 О to

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН (51)4 С 06 Р и/28

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ сравнения, коммутатор 3, элемент ИЛИ

4, элемент И 5, регистр 6, третий 7, четвертый 8, первый 9 и второй 10 блоки памяти, информационный вход 11 устройства, синхровход 12 устройства информационный выход 13 устройства, управляющий выход 14 устройства. В первом 9 и втором 10 блоках памяти хранится трасса программы, задавае-! мая в виде контрольных точек содерЭ жащих адрес, команду и/или операнд, в третьем 7 и четвертом 8 блоках памяти хранится последовательность адресов контрольных точек, выбираемых из первого 9 и второго 10 Ълоков памяти. Устройство отслеживает и вет-, вления программы, что определяется наличием двух блоков сравнения, ко торые сравнивают текущее состояние информационного входа 11 устройства с двумя возможными точками, поступающими из первого 9 и второго 10 блоков памяти. В зависимости от того, через какую контрольную точку проходит программа, с помощью коммута тора 3 выбирается следующий адрес ад. ресов контрольных точек. 4 ил.

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3925748/24-24 (22) 21.06.85 (46) 07.03.87. Бюл. N - 9 (71) Специальное конструкторское бюро "Кибернетика" с опытным производством Института кибернетики

АН АэССР (72) С.А.Бакалец, Н.В.Головин, Н.Н.Насруллаев и Б.Ф.Файсканов (53) 681.3 (088.8) (56) Авторское свидетельство СССР

9 754419, кл. G 06 F 11/22, 1979.

Авторское свидетельство СССР

1030805, кл. G 06 F 11/22, 1982. (54) УСТРОЙСТВО ДЛЯ ОТЛАДКИ ПРОГРАИИ (57) Изобретение относится к вычислительной технике и может быть использовано для автоматизированной отладки программ и построения специализированных отладочных комплексов.

Целью изобретения является повышение производительности отладки программ путем уменьшения объема исследуемой информации за счет исключения из ее состава информации по многократно повторяющимся циклам. Устройство содержит первый 1 и второй 2 блоки

„„SU„„1295402 А 1

1295402 2 ответственно информация А1 и НК (несуществующая комбинация адреса, кои второго 2 блоков сравнения, на другие входы которых поступают сигналы с информационного входа 11 устройства, на который поступают сигналы с шин отлаживаемой вычислительной машины. Появление информации на информационном входе t1 устройства со ровождается синхросигналами, поступающими на синхровход 12 устройства.

Информация, поступающая на информационный вход 11 устройства, постоянно сравнивается первым 1 и вторым

2 блоками сравнения с информацией, считываемой с первого 7 и второго 8 блоков памяти.

При появлении на информационном входе 11 устройства состояния А1 первый блок 1 сравнения вырабатывает на своем выходе сигнал, который поступает на управляющий вход коммутатора 3, в результате коммутатор 3 подсоединяет к информационному входу регистра 6 информацию с выхода третьего блока 9 памяти. Одновременно сигнал с выхода первого блока 1 сравнения через элемент ИЛИ 4 поступает на вход элемента И 5, разрешая прохождение синхроимпульса с синхровхода 12 устройства на стробирующий вход регистра 6. При поступлении синхроимпульса на синхровход, 12 устройства происходит запись в регистр 6 информации, стоящей на его информационном входе, в указанном случае 1 (фиг.3). С выхода регистра 6 новый адрес поступает на адресные входы третьего 9 и четвертого 10 блоков памяти, из которых происходит выборка ячеек с адресом !. Информация с выходов третьего 9 и четвертого 10 блоков памяти (фиг.3 соответственно

2 и 5) поступает на соответствующие адресные входы первого 7 и второго 8 блоков памяти, из которых соответственно выбираются контрольные точки

А2 и А5 (фиг„4) и поступают соответственно на входы первого 1 и второго

2 блоков сравнения. Таким образом, устройство остается в ожидании появления на информационном входе 11 устройства информации А2 или А5 (фиг.2), Если, например, появилась контрольУстройство работает следующим образом.

В начальном состоянии регистр 6 обнулен (вход начальной установки не показан). Сигналы с выхода регистра 6, поступая на адресные входы третьего 9 и четвертого 10 блоков памяти, выбирают ячейки с нулевым адресом. Информация, считываемая с выходов третьего 9 и четвертого 10 блоков памяти, является адресом .ячеек, выбираемых из первого 7 и второго 8 блоков памяти, т.е. выбираются ячейки с адресами 1 и 0 (фиг.3 и

Изобретение относится к высилите- фиг.4) . На выходах первого / и вто= льной технике и может быть использо- рого 8 блоков памяти появляется совано для автоматизированной отладки программ и построения специализированных отладочных комплексов. манды, операнда), которая поступает

Целью изобретения является повы- на соответствующие входы первого 1 шение производительности при отладке путем уменьшения объема исследуемой информации за счет исключения из ее состава информации по многократно 10 повторяющимся циклам.

На фиг.1 представлена блок-схема устройства для отладки программ, на фиг.2 — пример задания трассы программы; на фиг.3 — содержимое третье- 1 го и четвертого блоков памяти для указанного примера задания трассы программы, на фиг ° 4 — то же,для первого и второго блоков памяти.

Устройство (фиг.1) содержит пер- 20 вый 1 и второй 2 блоки сравнения, коммутатор 3, элемент ИЛИ 4, элемент

И 5, регистр 6, первый 7, второй 8, третий 9 и четвертый 10 блоки памяти, информационный вход 11 устройства, синхровход 12 устройства, информационный выход 13 устройства, управляющий выход 14 устройства.

Трасса программы (фиг.2) задается в виде блоков, каждый из которых пред- З0 ставляет собой контрольную точку (адрес, команда или операнд), Обозначения блоков А -А введены для об19. легчения сопоставления трассы программы с ее заданием в блоках памяти. 35

Перед отладкой программы ее вариантная трасса задается в виде графа (фиг.2). Б третьем 9 и четвертом 10 блоках памяти формируется информация о трассе прохождения программы по 40 контрольным точкам. В первом 7 и втором 8 блоках памяти записываются сами контрольные точки (адрес, команда, операнд).

129540

3 ная точка А5 срабатывает второй

I блок 2 сравнения и с его выхода сигнал поступает на другой управляющий вход коммутатора, в результате на информационный вход регистра подается информация с выхода четвертого блока 10 памяти. Одновременно сигнал с выхода второго блока.2 сравнения через элемент ИЛИ 4 поступает на вход элемента И 5, разрешая прохождение 10 синхроимпульса с синхровхода 12 ус ройства на стробирующий вход регистра 6. При поступлении синхроимпульса происходит запись в регистр 6 информации, стоящей на его информационном выходе, т.е. 5. Из третьего 9 и четвертого 10 блоков памяти происходит выборка ячеек с адресом 5. Информация с выбранных ячеек (фиг.3,6 и О) поступает на адресные входы соответ- 20 ственно с первого 7 и второго 8 бло= ков памяти, из которых выбираются контрольные точки соответственно А6 и НК.

Сигнал, поступающий на стробирующий вход регистра 6, одновременно поступает на управляющий выход 14 устройства. Сигнал с управляющего выхода 14 устройства может быть использован для останова отлаживаемой программы или идентификации момента прохождения контрольных точек.

Выход регистра 6, кроме адресных входов третьего 9 и четвертого 10 блоков памяти, поступает также на 35 ийформационный выход 13 устройства и может быть использован для индентификации места прохождения программы на ее трассе.

Формула изобретения 40

Устройство для отладки программ, содержащее первый блок сравнения, 2 4 элемент ИЛИ, элемент И, регистр, первый и второй блоки памяти,.причем тактовый вход устройства соединен с первым входом первого элемента И, выход первого блока памяти соединен первым информационным входом первого блока сравнения, о т л и ч а— ю щ е е с я тем, что, с целью повышения производительности при отладке, в устройство введены второй блок сравнения, коммутатор, третий и четвертый блоки памяти, причем информационный вход устройства соединен с вторым .входом первого блока сравнения и первым входом второго блока сравнения, выход которого соединен с первым входом элемента ИЛИ и первым управляющим входом коммутатора, выход первого блока сравнения соединен с вторым управляющим входом коммутатора и вторым входом элемента ИЛИ, выход которого соединен с вторым входом элемента И, выход элемента И соединен с входом записи регистра и является выходом индентификации контрольной точки устройства, выход коммутатора соединен с информационным входом регистра, выход второго блока памяти соединен с вторым входом второго блока сравнения,выход регистра соединен с адресными входами третьего и четвертого блоков памяти и является адресным выходом устройства, выход третьего блока памяти соединен с адресным входом первого блока памяти и с первым информационным входом коммутатора, выход четвертого блока памяти соединен с адресным входом второго блока памяти и с вторым информационным входом коммутатора.

1295402

Редактор И.Шулла

Заказ 619/56 Тираж 673 ПодписнОе

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, r.Óæãîðoä, ул.Проектная,4

АУ 44

А

) да ((а 1 г

Юиг4

Составитель И.Сигалов

Техред Я.Попович Корректор В. Бутяга