Устройство для организации мультипроцессорной иерархической системы

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной техника и может быть использовано для организации мультипроцессорной иерархической вычислительной системы. Изобретение решает задачу уменьшения аппаратурных затрат и повышения скорости обмена информацией за счет уменьшения необходимости чис-. ла команд обмена. С этой целью устройство содержит регистр 6 управления , предназначенный для хранения номера канала обмена информацией между уровнями системы, дешифратор 7 выбора канала и блоки 10 приемопередатчиков , управляемые блоками 5 управления прямым доступом в память и обеспечивающие прием и передачу информа ции в режимах Ввод и Вывод, Зил. с (Л с: to со О нй о со

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (11) 5409 А i (51) 4 С "6 Р 15/16

1 г.

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А BTOPGHOMV СВИДЕТЕЛЬСТВУ

О

4ъ

1)

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3831145/24-24 (22) 26.09,84 (46) 07,03,87, Бюл. ¹ 9 (71) Институт электродинамики АН

УССР и СКТБ Института электродинамики АН УССР (72) В.И.Назаренко, В.В.Рогоза, В.В.Сорочинский и Ю.Н.Холоденко (53) 681.325 (088.8) (56) Вейцман К. Распределенные сис.темы мини- и микроЭВМ. - M.: Финансы и статистика, 1982.

Титце У., Шенк К. Полупроводниковая схемотехника: Справочное руководство. — M.: Мир, 1983.

Интерфейс накопителя на гибких магнитных дисках И 4 15 ИПГ-16-012.

Техническое описание и инструкция по эКсплуатации 3.858.377 ТО, 1979.

Устройство прямого доступа к памяти ИЗ-15КС-16-002, Техническое описание и инструкция по эксплуатации

И9М3,858.385 ТО, 1979. (54) УСТРОЙСТВО ДЛЯ ОРГАНИЗАЦИИ МУЛЬТИПРОЦЕССОРНОЙ ИЕРАРХИЧЕСКОЙ СИСТЕМЫ (57) Изобретение относится к вычислительной технике и может быть использовано для организации мультипроцессорной иерархической вычислительной системы. Изобретение решает задачу уменьшения аппаратурных затрат и повышения скорости обмена информацией за счет уменьшения необходимости чис-. ла команд обмена. С этой целью устройство содержит регистр 6 управления, предназначенный для хранения номера канала обмена информацией между уровнями системы, дешифратор 7 выбора канала и блоки 10 приемопередат- Я

МФ чиков, управляемые блоками 5 управления прямым доступом в память и обеспечивающие прием и передачу информа:ции в режимах "Ввод" и "Вывод". 3 ил.

1295409 2

Изобретение относится к вычислительной технике и может быть испольэовано для организации мультипроцессорной иерархической вычислительной системы.

Цель изобретения — уменьшение аппаратурных затрат, а также повышение скорости обмена за счет уменьшения числа команд, необходимых для организации обмена.

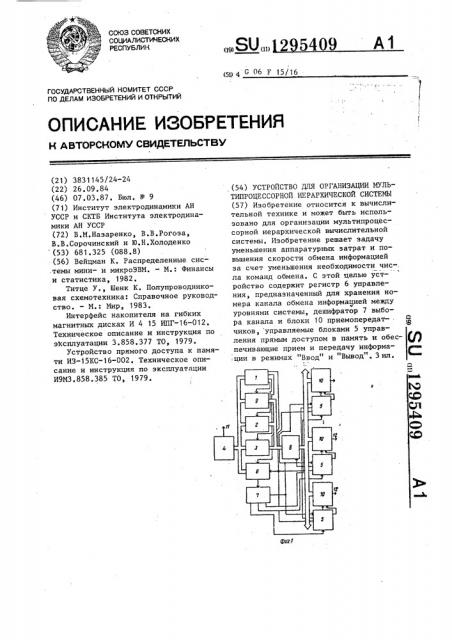

На фиг. 1 представлена структурная схема устройства, на фиг, 2 блок-схема алгоритма работы устройства в режиме ввода информацпи в память микроЭВМ верхнего уровня," на фиг. 3 — то же, в режиме вывода информации в память микроЭВМ нижнего уровня.

Устройство содержит дешифратор 1 управляющих сигналов, входной регистр

2, регистр 3 адреса, блок 4 приемопередатчиков верхнего уровня, блоки

5 управления прямым доступом в память, регистр 6 управления, дешифратор 7 выбора, блок 8 внутренних приемопередатчиков, выходной регистр 9 и блоки 10 приемопередатчиков нижнего уровня. Устроиство имеет входвыход 11 верхнего уровня, входы-выхбды 12 нижнего уровня.

Устройство работает следующим образом.

Всеми обменами в системе управляет микроЭВМ верхнего уровня. Под ее управлением происходит ввод-вывод информации в режиме прямого доступа к памяти в (из) одну (ой) микроЭВМ нижнего уровня.

Вывод информации происходит следующим образом. В программном режиме микроЭВМ верхнего уровня заносит в регистр 3 адреса адрес ячейки памя.ти, по которому производится вывод информации в выходной 9 регистр данные, которые переданы. Занесение адреса и данных в регистры стробируется с выходов дешифратьра 1 управляющих сигналов. Затем в регистр 6 управления записываетея информация о номере микроЭВМ нижнего уровня, с которой осуществлен обмен данными и о режиме обмена (в рассматриваемом случае "Вывод" ). С выхода регистра

6 управления информация поступает на вход дешифратора 7 выбора, на одном иэ выходов которого появляется сигнал пуска блока 5, номер которого определен номером на регистре 6 управления. Кроме того, на входы выбора направления обмена всех блоков 5 логики прямого доступа передается информация о выбранном режиме обмена.

5 По сигналу пуска блок 5 управления прямым доступом формирует запрос к микроЭВМ нижнего уровня и, в случае разрешения прямого доступа, формирует все необходимые сигналы для управления процессом обмена (" Вывод" ).

Эти сигналы с выходов блоков 5 через блоки приемопередатчиков нижнего уровня поступают в канал ЭВМ, При этом блоки 5 по выходам "Адрес-данные" осуществляют управление блоком

8 внутренних приемопередатчиков, а по выходам управления выдачей — управление выходами блоков 10 приемопередатчиков нижнего уровня, устанавливая таким образом связь через магистраль между каналом выбранной микроЭВМ и регистром 3 адреса и выходным 9 регистром. Адрес ячейки па25 мяти в канал микроЭВМ нижнего уровня поступает с регистра 3 адреса, а данные — с выходного регистра 9. Обмен заканчивается выдачей блоком 5 сигнала сброса на регистр б управления.

После этого устройство готово к новому циклу работы.

Ввод информации происходит аналогичным образом, за исключением того, .что с регистра б управления через дешифратор 7 выбора на вход выбора направления обмена блоков 5 логики прямого доступа поступает информация о- режиме работы "Ввод", После запуска блока 5 он формирует все необходимые сигналы для управления процессом ввода. При этом блок 5 осуществляет управление блоками внутренних приемопередатчиков и приемопередатчиков нижнего уровня таким образом, что адрес ячейки поступает с регистра 3 адреса, а входные данные фиксируются на регистре 2. После выдачи блоком 5 сигнала "Сброс" на регистр б управления данные с регистра

2 могут быть считаны с входа-выхода верхнего уровня.

Формула изобретения

Устройство для организации мультипроцессорной иерархической системы, 55 содержащее дешифратор управляющих сигналов, входной регистр, регистр адреса„ блок приемопередатчиков верхнего уровня и И блоков управления

1295 прямым доступом в памят, причем первые информационные входы-выходы входного регистра и регистра адреса подключены к первому информационному входу-выходу блока приемопередатчиков верхнего уровня и к входу дешифратора управляющих сигналов, первый и второй выходы которого подключены к синхровходам входного регистра и регистра адреса соответственно, второй инфор- 10 мационный вход-выход блока приемопередатчиков верхнего уровня является входом-выходом верхнего уровня устройства, о т л и ч а ю щ е е с я тем, что, с целью уменьшения аппаратурных15 затрат и повышения скорости обмена за счет уменьшения числа команд, необходимых для организации обмена, оно содержит регистр управления, дешифратор выбора, блок внутренних приемо- О передатчиков, выходной регистр и блоки приемопередатчиков нижнего уровня, причем третий и четвертый выходы дешифратора управляющих сигналов подключены к синхровходам выходного регистра и регистра управления соответственно, первые информационные входывыходы которых подключены к первому информационному входу-выходу блока приемопередатчиков верхнего уровня, вторые информационные входы-выходы входного регистра, выходного регистра и регистра адреса подключены к первому информационному входу-выходу

409 л блока внутренних приемопередатчиков, второй информационный вход-выход которого подключен к первым информационным входам-выходам блоков приемопередатчиков нижнего уровня, вторые информационные входы-выходы которых являются соответствующими входамивыходами нижнего уровня устройства, выход регистра управления подключен к входу дешифратора выбора, первый выход которого подключен к входам выбора направления обмена блоков управления прямым доступом в память, вход пуска i-ro (i=1 N) блока управления прямым доступом в память подключен к j-му (j=2,N+1) выходу дешифратора выбора, выходы окончания цикла блоков управления прямым доступом в память подключены к входу сброса регистра управления, выходы "Адрес-данные" блоков управления прямым доступом в память подключены к входу

"Адрес-данные" блока внутренних приемопередатчиков, выходы управлейия выдачей информации блоков управления прямым доступом в память подключены к входам управления выдачей информации соответствующих блоков приемопередатчиков нижнего уровня, выходы уп-! равляющих слов обмена блоков управле,ия прямым доступом в память подключены к входам управления режимом прямого доступа соответствующих блоков приемопередатчиков нижнего уровня.

1295409

Составитель Н.Захаревич

Редактор Н,Бобкова Техред И.Попович Корректор Г.Решетник

Заказ 619/56 Тираж 673 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035s o s E-35 Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул, Проектная, 4