Запоминающее устройство

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано при создании быстродействующих систем памяти повышенной надежности . Целью изобретения является повьшюние быстродействия устройства в режиме считьшания. Запоминающее устройство содержит накопитель, шифратор , первый и второй регистры, блок коррекции ошибок, блок вычисления признаков ошибки, блок обнаружения ошибки, первый и второй дешифраторы , блок ассоциативной памяти, первый и второй блоки селекции, сумматор по модулю два, первый и второй элементы И, элемент ИЛИ. 11овьш1ение быстрюдействия устройства в режиме считывания обеспечивается за счет перераспределения дополнительных временных затрат между циклами записи и считывания путем согласования в режиме записи записываемого бита информации с логическим состоянием отказавшего разряда ячейки накопителя . 2 шт. с (Л СП ел

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

А1 (11 4 Ь 11 С 29/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

flO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3933798/24-24 (22) 22.07.85 (46) 07.03.87.Вюл. Ф 9 (71) Минский радиотехнический институт (72) Н.И.Урбанович (53) 681.327.67 (088.8) (56) Авторское свидетельство СССР

У 1014042, кл. G 11 С 29/00, 1983.

Авторское свидетельство СССР

У 1195393, кл. С 11 С 29/00, 1984 ° (54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО (57) Изобретение относится к вычислительной технике и может быть использовано при создании быстродействующих систем памяти повышенной надежности. Целью изобретения является повышение быстродействия устройства

„. $}}„„} 2ЩЩ} в режиме считывания. Запоминающее устройство содержит накопитель, шифратор, первый и второй регистры, блок коррекции ошибок, блок вычисления признаков ошибки, блок обнаружения ошибки, первый и второй дешифраторы, блок ассоциативной памяти, первый и второй блоки селекции, сумматор по модулю два, первый и второй элементы И, элемент ИЛИ. Повышение быстродействия устройства в режиме считывания обеспечивается за счет перераспределения дополнительных временных затрат между циклами записи и считывания путем согласования в режиме записи записываемого бита ин- а ф формации с логическим состоянием отказавшего разряда ячейки накопителя. 2 ил.

С:

1295456

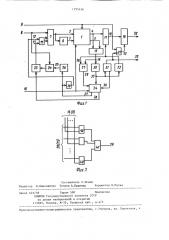

Блок селекции (фиг.2) содержит элементы И 40 и элемент ИЛИ 41.

Блок 34 ассоциативной памяти предназначен для хранения признаков одиночных ошибок и состояния отказавшего элемента памяти накопителя, ко- 40 торое вырабатывается блоком 27, На выходах 37 и 38 блока 34 — то, что записывалось по соответствующему адресу по входам 35 и 29 соответственно. 45

При появлении единичного сигнала на входе !4 регистра 7 его состояние инвертируется. Единичный сигнал на выходах 32 и 36 блока 31 появляется при обнаружении двойной и одиночной соответственно ошибок в кодовом слове.

Накопитель, как обычно, состоит из отдельных элементов памяти, режимом работы которых запись/считывание) управляет сигнал 9.

Устройство работает следующим образом.

Изобретение относится к вычислительной технике и может быть использовано при создании быстродействующих систем памяти повышенной надежности. 5

Целью изобретения является повышение быстродействия устройства в режиме считывания, На фиг.l изображена схема запоминающего устройства; на фиг.2 — схема блока селекции.

Устройство (фиг.1) содержит накопитель 1 с информационными входами 2 и 3 и выходами 4 и 5, шифратор

6, первый регистр 7, информационные

8, управляющий 9 и адресные 10 входы устройства, второй элемент И 11 с входами 12 и 13 и выходом 14, второй регистр 15 с выходами 16, блок 17 коррекции ошибок с выходами 18, блок 19 вывода информации, информационные выходы 20 устройства, первый элемент И 21 с выходом 22, сумматор

23 по модулю два, первый блок 24 селекции с входами 25, второй дешифратор 26, второй блок 27 селекции с входами 28 и выходом 29, блок 30 вычисления признаков ошибки, блок 31 обнаружения ошибки, выход 32 ошиб30 ки устройства, первый дешифратор 33, блок 34 ассоциативной памяти с входами 35 и 36 и выходами 37 и 38 и элемент ИЛИ 39.

В режиме записи входная информация (R-1 символов) по входам 8 заносится в регистр 7. Адрес опрашиваемой ячейки накопителя 1 установлен на шинах 10, в соответствии с чем на выходах 37 и 38 блока 34 ассоциативной памяти появляется признак возникшей ранее в этой ячейке ошибки и логическое состояние этой ячейки. Если ошибок ранее не было, то признак ошибки равен нулю (синдром равен нулю) . Дешифратором 26 признак ошибки дешифруется и устанавливается точное местоположение отказавшего разряда (на одном из выходов 25 дешифратора

26 — единичный сигнал). Блок 24 селекции выделяет из информационных символов тот, который должен запи-. саться в этот элемент памяти. Причем в блоке 34 хранится признак ошибки и логическое состояние элемента вне зависимости произошел ранее сбой или отказ. Согласование записываемой информации с состоянием отказавшего элемента происходит только для основных разрядов, поскольку длина информационного слова обычно значительно больше, чем длина проверочного, и вероятность возникновения неисправности в разрядах, хранящих информационные биты, вьппе, чем в хранящих проверочные. Сравнение ло-. гических состояний неисправного элемента с информационным символом, подлежащим хранению, производится сумматором 23 по модулю два. Если сравнение дает "1", а о том, что в этой ячейке накопителя 1 ранее уже возник отказ, свидетельствует единичный сигнал на выходе элемента ИЛИ 39, то все разряды слова, записанного в регистр 7, инвертируются, на основании чего шифратор 6 вырабатывает проверочные символы. После этого на шину 9 подается сигнал разрешения записи в накопитель 1 кодового слова по входам 2 и 3 накопителя. На этом цикл записи закончен. Факт хранения слова в инверсном виде означает единичный символ R-го разряда кодового слова.

В цикле считывания кодовое слово записывается в регистр 15, кроме того К информационных символов поступают в блок 17 коррекции ошибок через его входы 4. Блоком 30 вычисляется признак ошибки. Если в считанном кодовом слове ошибок нет, то признак

1295456

Формула изобретения 45

Запоминающее устройство, содержащее накопитель, одни информационные входы которого соединены с выходами шифратора, другие информационные входы подключены к входам шифратора и к входам первого регистра, управляющий вход соединен с прямым входом первого элемента И и является управляющим входом устройства, одни

50 ошибки равен нулю, и не равен нулю в противном случае. Признак ошибки поступает с выхода блока 30 на входы блокон 31 и 33; блок 31 обнаружения ошибки определяет кратность ошибки, дешифратор 33 определяет точное местоположение ошибочного разряда в кодовом слове. Если произошла одиночная ошибка, то единичный сигнал на выходе

36 блока 31 разрешает запись в блок 10

34 (по адресу, установленному на ши нах 1.0) признака ошибки и логического состояния неисправного элемента памяти, которые установлены соответственно на входах 35 и 29 блока 34.

Параллельно с этим единичный сигнал на одном из ньжодов дешифратора 33 исправляет неправильно считанный бит информации. Таким образом на выход устройства попадает искомая инфор- 20 мация без ошибок. Если в режиме считывания установлено, что произошла двойная ошибка, то единичный сигнал на выходе 32 блока 31 блокирует блок

19 вывода информации и сообщает процессору (не показан) о появлении некорректируемой ошибки, которая однако может быть нейтрализована довольно просто известными методами. В последнем случае имеется в виду, что двойная ошибка появилась за время хранения последнего кодового слова.

Если одна из ошибок возникает ранее, а другая позже, то первая из них нейтрализуется при записи инфор- 35 мации, другая — при считывании..При этом не учитывается тип отказа. Даже в случае первоначального появления сбоя входная информация и последующем инвертируется. В режиме считы- 40 вания состояние ячеек блока 34 влия-. ния на считываемую информацию не оказывает. ньходы накопителя подключены к одним входам блока коррекции ошибок и второго регистра, а другие выходы соединены с другими входами второго регистра, выходы которого подключены к входам блока вычисления признаков ошибки, выходы которого соединены с одними информационными входами блока ассоциативной памяти, входами блока обнаружения ошибки и с входами первого дешифратора. выходы которого подключены к другим входам блока коррекции ошибок, выходы которого подключены к информационным входам блока вывода информации, выходы которого являются информационными выходами устройства, а управляющий вход соединен с выходом первого элемента

И, инверсный вход которого является выходом ошибки устройства и подключен к одному выходу блока обнаружения ошибки, другой выход которого соединен с управляющим входом блока ассоциативной памяти, адресные входы которого подключены к адресным входам накопителя и являются адресными входами устройства, а одни выходы соединены с входами элемента ИЛИ и входами второго дешифратора, одни входы первого регистра являются информационными входами устройства, о т л и ч а ю m; е е с я тем, что с целью повышения быстродействия устройства в режиме считывания, в него введены первый и второй блоки селекции, сумматор по модулю два и второй элемент И, причем одни входы первого блока селекции соединены с выходами второго дешифратора, другие входы подключены к информационным входам устройства, а выходы соединены с одними входами сумматора по модулю два, другие входы которого подключены к другим выходам блока ассоциатив- ной памяти, а выход соединен с первым входом второго элемента И, второй вход которого подключен к выходу элемента ИЛИ, а выход соединен с другим входом первого регистра, входы второго блока селекции подключены к выходам второго регистра и первого дешифратора соответственно, а выходы подключены к другим информационным входам блока ассоциативной памяти.

1295456

Составитель О.Исаев

Редактор И.Николайчук Техред А.Кравчук Корректор И.Муска

Заказ б22/58 Тираж 590 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул. Проектная, 4