Цифровой вероятностный фильтр

Иллюстрации

Показать всеРеферат

Изобретение относится к области вычислительной техники и может быть использовано в стохастических оптимальных системах автоматического управления и вычислительных сетях. Цель изобретения - повьшение быстродействия . Поставленная цель достигается за счет того, что оптимальный фильтр содержит (N-1) блок 1 , - 1 , вьделения наименьшего числа, N блоков постоянной памяти, демультиплексор 3, элемент И 6, счетчик 4, синхронизатор 5 и соответствующие связи между узлами фильтра, 2 нл.

СОЮЗ СОВЕТСКИХ

COLlHAЛИСТИЧЕСНИХ

РЕСПУБЛИН

507 А1 (19) (11) (51)4 Н 03 Н 17 06 G 06 F 15/353

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А ВТОРСНОМЪГ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3936856/24-24 (22) 05.08.85 (46) 07.03.87. Бюл. № 9 (72) С.В.Соколов (53) 681.321(088,8) (56) Титце У., Шенк К. Полупроводниковая схемотехника. — M.: Мир, с.429.

Авторское свидетельство СССР № 1170463, кл. G 06 Р 15/353, Н 03 Н 21/00, опублик.1985. (54) ЦИФРОВОЙ ВЕРОЯТНОСТНЫЙ ФИЛЬТР (57) Изобретение относится к области вычислительной техники и может быть использовано в стохастических оптимальных системах автоматического управления и вычислительных сетях. Цель изобретения — повышение быстродействия. Поставленная цель достигается за счет того, что оптимальный фильтр содержит (К вЂ” 1) блок 1, — 1.„ „ выделения наименьшего числа, Л блоков

2, — 2 постоянной памяти, демультиплексор 3, элемент И 6, счетчик 4, синхронизатор 5 и соответствующие связи между узлами фильтра. 2 ил.

1 12955

Изобретение относится к специализированной вычислительной технике и может быть использовано в стохастических оптимальных системах автоматического управления и вычислительных 5 сетях.

Цель изобретения — повышение быстродействия.

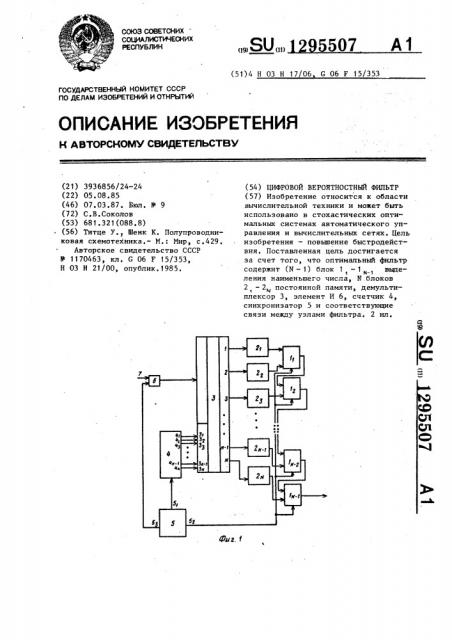

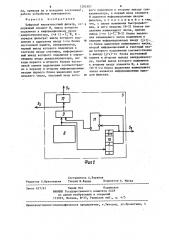

На фиг.1 представлена функциональная схема фильтра; на фиг.2 — синхро-1О низатор.

Фильтр (фиг.1) содержит блоки

1 „- 1 я 4 выделения наименьшего числа, блоки 2 — 2 .постоянной памяти,деN 3 мультиплексор 3, счетчик 4, синхрони- 15 затор 5, элемент И 6 и информационный, вход 7.

Синхронизатор 5 (фиг.2) содержит тактовый генератор 8, элемент И 9, Т-.разрядный регистр 10 сдвига, RS- 2О триггер 11 и делитель 12 частоты.

Фильтр работает следующим образом.

Случайная последовательность N

1-разрядных чисел с известным вероятностным распределением и частотой следования с входа 7 устройства поступает на вход элемента И 6. На другой вход элемента И 6 поступают синхроимпульсы с третьего выхода 5 синхронизатора 5 (через элемент И 9 с выхода тактового генератора 8), обеспечивая хронированное поступление входной последовательности на инфор- мационный вход демультиплексора 3.

Одновременно импульсы с выхода такто- g5 ваго генератора 8 через элемент И 9, на второй вход которого поступает единичный сигнал с нулевого выхода, RS-триггера 11 (в исходном состоянии

RS-триггер 11 обнулен), поступают на 40 вход делителя 12 частоты (коэффициент равен 1/1). С выхода делителя 12 частоты (т.е. первого выхода 5„ синхронизатора 5) импульсы поступают на счетный вход счетчика 4. Код с выхо- 45 дов 4,-4 „ счетчика 4 поступает на входы 3, 3„ управления коммутацией демультиплексора 3 "1 x N . Для синхронизации сигналов управления на входах 3 -3„ и информационных сигна- 50 лов на информационном входе демультиплексора 3 время задержки <,: элемента

И 6 выбирается равным =Т + t« +

+ 7, (ьс, где ; — время задержки

i-го блока; gt — временной интервал следования импульсов входной после:довательности, равный также интервалу следования самих 1-разрядных входных кодовых последовательностей (чисел).

I=NI 1 ьС где ()

L IO H "II

- знак целевого числа;

- время задержки блоков

10 и 1 1, снимается сигнал, переводящий RSтриггер 11 в единичное состояние— запрещается прохождение импульсов с выхода тактового генератора 8 через элемент И 9.

Тем самым исключается возможность прохождения через элемент И 6 и демультиплексор 3 какой-либо информации до окончания формирования кода на выходе блока 1„,, По окончании формирования числа на выходе устройства с Т-ro выхода регистра 10, е й\

+б

Т = С 1 — -- — - — Ы 1 + р — 1 + t

+ + 2+ е О

« о Я: где С вЂ” любое целое число, обеспечивающее данное неравенство; снимается сигнал, поступающий на Rвход RS-триггера 11 — RS-триггер 11 переводится в исходное (нулевое) положение (одновременно этот сигнал через второй выход 5 синхронизатора

5 поступает на тактовые входы блоков

1,,...,1„ выделения наименьшего чис1эеееэ И 1

07 2

С выходов 1,2,...,N демультиплексора 3 1-разрядные кодовые последовательности поступают на входы соот ветствуШ блоков 2 „ 22.. .,2 постоянной памяти, где происходит их умножение на р-разрядный код соответствующего весового коэффициента а, .

Для синхронизации сигналов на входах

Р блоков 1<„ -,, выделения наименьшего числа время задержки в схеме 2(и- 1 задержки выбрано равным i(1 a t =, ), i = 1 2,...,К-2, где t — время задержки блока выделения наименьшего числа. Так как последовательное соединение блоков 1„,...,1„,. реализует процедуру выбора наименьшего числа из выходной выборки заданного объема

N, то на выходе (N-i)-ro блока 1„, выделения наименьшего числа формируется в (1+р-1)-разрядном коде число с требуемым законом распределения.

Для повышения помехоустойчивости работы через время 1 at c I-го выхода регистра 10 сдвига (в начальный момент в первый разряд регистра 10 сдвига записана "1", а в остальные—

II 01 I )

Составитель А. Баранов

Редактор О.Юрковецкая Техред В.Кадар Корректор И. Муска

Заказ 627/61

Тираж 902 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

3 1295 ла, приводя их в исходное состояние), работа устройства повторяется.

Формула изобретения

Цифровой вероятностный фильтр, со- 5 держащий элемент И, выход которого подключен к информационному входу демультиплексора, -й (i = 1, N N— порядок фильтра) выход которого подключен к адресному входу i-ro блока 1о постоянной памяти, синхронизатор, первый выход которого подключен к счетному входу счетчика, информационный выход которого подключен к управляющему входу демультиплексора, вы- 15 ходы первого и второго блоков постоянной памяти подключены соответственно к первому и второму информационным входам первого блока выделения наименьшего числа, тактовый вход кото- 20

507 4 рого подключен к второму выходу синхронизатора, а первый вход элемента

И является информационным входом фильтра, отличающийся тем, что, с целью повышения быстродействия, в него введены (N-2) блоков выделения наименьшего числа, причем выход j-го (j=1,, N-2) блока выделения наименьшего числа подключен к первому информационному входу (j+1)го блока выделения наименьшего числа, второй информационный и тактовый входы которого подключены соответственно к выходу (3+2)-ro блока постоянной памяти и второму выходу синхронизатора, третий выход которого подключен к второму входу. элемента И,. а выход (И-1)-го блока выделения наименьшего числа является информационным выходом фильтра.