Вычислитель ошибок помехоустойчивого декодера

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике. Его использование в аппаратуре передачи и обработки цифровой информации позволяет упростить устройство. Вычислитель ошибок содержит блок 1 сумматоров, перемножителд 2, 3, квадратор 4, преобразователь 5 кода, сумматоры 6, 7, элемент ИЛИ 8, элемент ИЛИ-НЕ 9, элемент И 10 и блоки 11, 12 элементов И. Благодаря сокращению числа вычисляемых переменных достигается упрощение схемы, I ил, сл с

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCHGMY СВИДЕП:ЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3867257/24-24 (22) 12,03.85 (46) 07.03.87. Бюл. № 9 (71) Курский политехнический институт (72) А.Г. Бабанин и А.П. Типикин (53) 681.327(088.8) (56) Патент Великобритании ¹ 2079993, кл. G 06 F 11/08, 1983.

Авторское свидетельство СССР

1Ф 1018119, кл. G 06 F 11/10,, 10.06.81 (54) ВЫЧИСЛИТЕЛЬ ОШИБОК ПОМЕХОУСТОЙ- .

ЧИВОГО ДЕКОДЕРА

„„Я0„„1295532 А 1 (5В 4 Н 03 М 13/02 G 06 F 11/00 (57) Изобретение относится к вычислительной технике. Его использование в аппаратуре передачи и обработки цифровой информации позволяет упростить устройство. Вычислитель ошибок содержит блок 1 сумматоров, перемножители 2, 3, квадратор 4, преобразователь 5 кода, сумматоры 6, 7, элое†мент ИЛИ 8, элемент ИЛИ-НЕ 9, элемент

И 10 и блоки 11, 12 элементов И. Благодаря сокращению числа вычисляемых переменных достигается упрощение схемы. 1 ил.

1295532

Изобретение относится к вычислительной технике и может быть использовано в устройствах декодирования кода Рида-Соломона (PC-кода) в аппаратуре передачи и обработки цифровой информации.

Цель изобретения — уттрощение устройства.

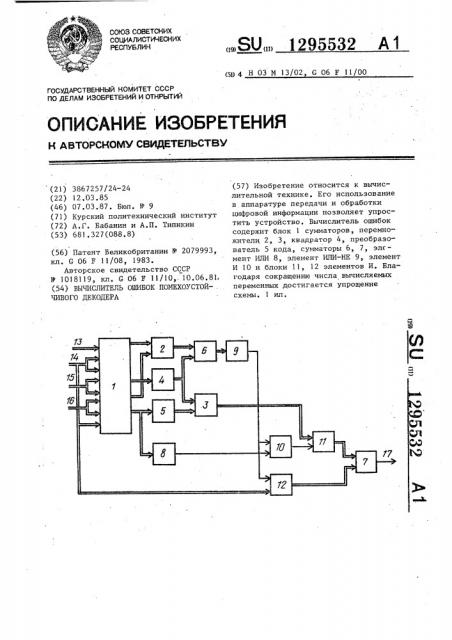

На чертеже приведена блок-схема вычислителя ошибок.

Вычислитель ошибок помехоустойчивого декодера содержит блок I сумматоров, первый и второй перемножители

2 и 3, квадратор т), преобразователь

5 кода, первый и второй сумматоры 6 и 7, элемент ИЛИ 8, элемент ИЛИ-НЕ

9, элемент И 10, первый и второй блоки ll и 12 элементов И, первые— четвертые входы 13-16 и выходы 17.

Сумматоры 1, 6 и 7, перемножители 2 и 3 и квадратор 4 выполняют операции надчислами виоле Галуа07 (2 ), где m — - разрядность входных символов.

Преобразователь 5 кода служит для выдачи кода обратного элемента поля

Галуа. Он может быть выполнен на программируемом постоянном запоминающем устройстве, по нулевому адресу которого заносится. нулевое значение эле мента поля Галуа GF (2 ).

При описании работы устройства использованы следующие обозначения: У, и У - значения ошибок как символы

2 .длиной ш бит или элементы конечного .поля GP (2 ); Х, и Х.2 — локаторы ошибок; $,, Sz, Зз и S4 — синДРомы ошибок; О, — примнтивный элемент конечного поля ОР (2 ); Х =О произm . l( вольный элемент конечного поля, обратный локатору;

1 при Е>0 - операция.вьще61яп 2= ленин нулевого

0 при Z=D значения элемента конечного поля

Принцип работы устройства представляет собой совмещение процедуры нахождения корней полинома локаторов ошибок с пошаговым методом декодирования циклических кодов, причем в ка)тдом такте декодирования совмещены

"процедуры классификации тИпов ошибок, локализации ошибки и вычисления ее значения.

Вычислитель ошибок работает следующим образом.

В k-м такте, где k E, (0, К-1), Кдлина информационной части РС-кода, на входы 13-16 вычислителя с блока формирования синдромов (не показан) параллельно подаются соответствующие синдромы S, Х, S Х, Б Х и S4Õ де2 з 4 кодируемого кодового слова, а на выходах 17 вычислителя ошибок в этом же такте появляются, значения ошибок

t0 1 в позициях — Х кодового слова. При отсутствии ошибок в кодовом слове на выходах 17 во всех тактах вырабатывается нулевое значение У. В слу15 чае одной ошибки со значением У, в позиции Х(на выходах 17 значение

У У, вырабатывается только при

Х = — а во всех остальных тактах

Х

20 на выходах 17 вырабатывается У = О.

В случае двух ошибок со значениями

У, и У в соответствующих позициях

Х, .и Х2 значения У = У, и У = У2 вырабатываются на выходах 17 при соот25 1 l ветственно Х = — и Х = —, а в ос-. х, х тальных тактах на выходах 17 вырабатывается значение У = О.

Синдромы, поступившие в очередном такте с входов 13-16 на соответствующие входы блока 1 сумматоров, попарно суммируются, образуя на выходах блока 1 сумматоров соответствующие

35 суммы:

«4 где t< и и " логические переменные, с помощью которЫх производится класg5 сификация типов ошибок в кодовом сло-, ве и локализация места ошибок.

Логические переменные вычисляются по следующим выражениям:

® «- 24( щ teal ««ig« (Х) )+««Д«(Е, (Х)+ «; (Х) <

)(z; (x}

Логическая переменная Ся образуется на выходе элемента ИЛИ 8, логическая переменная t вычисляется с помо55 щью блоков 2, 4, 6, 9 и образуется на выходе элемента ИЛИ-НЕ 9, отноz (x) шение (Х вычисляется блоками 3-5.

<-М4(!

295532

При декодировании РС-кодов с исправлением двух ошибок в вычислителе ошибок возможны следующие три ситуации.

При первой ситуации в кодовом слове отсутствуют ошибки, т.е. X<=X<=

=У =У2 =О. В этом случае в каждом такте на входы 13-16 поступают нулевые значения, .так как -< =S =Sз=S4 =О.

На выходе элемента,ИЛИ 8 образуется

t =О, на выходе элемента ИЛИ-.НЕ 9

=1, поэтому на каждом такте работы на выходах 17 образуется значение ошибки У = X S2 = О.

При второй ситуации в кодовом слове имеет место одна ошибка, т.е. х ФО, У< 09 х=уг=б, Возможны два случая. Зо-первых-, ХХ„ф1, т.е. ошибка не локализована, тогда Z, (Х)9-0, а

f(X) = О. Поэтому на выходе элемента

ИЛИ 8 и на выходе элемента ИЛИ-НЕ 9 образуются соответственно t =l и t =1, В этом случае на выходах !7 всегда будет нулевое значение, так как

2 (Х)

Х (Х,У, )+Х (Х,У, )

+Х (ХУ) О

Во-вторых, ХХ,=1, т.е. ошибка локализована. Тогда Z (X)=0 и P(X)=

=0. Поэтому на выходе элемента ИЛИ 8 и на выходе элемента ИЛИ-НЕ 9 обра35 зуются соответственно t< =О и =1.

В этом случае на выходах 17 вырабатывается значение ошибки У, У = Х Бг = Х (Х„У,) = ХХ,) У„=У,.

При третьей ситуации в кодовом 4О слове имеют место две ошибки, т.е ° х ф09 х 09 У, 409 х(х29 У 0. Воз можны два случая. Во-первых, ХХ, и ХХ 19 т.е. ни одна из ошибок не локализована. При этом (Х) может 4 принимать любые значения, т.е. возможно как tt=О, так и t< =1 на выходе элемента ИЛИ 8, Однако ф(Х)Ф09 и на выходе элемента ИЛИ-НЕ 9 всегда

t ==О, поэтому в соответствии с логи9

50 ко-алгебраическим выражением для вычисления значения ошибок на выходах

17 образуется У =- О. Во-вторых, локализована одна из двух сшибок, например, ХХ =1. Тогда ХХг ф1 и K г„(Х) ФО

P(X) =Q. Поэтому на выходе элемента ИЛИ 8 и -a выходе элемента ИЛИ-НБ 9 образуются со-ответственно t = 1 и t2 =, 1. В этом случае на выходах 17 образуется значение ошибки У, .

У=Х S+ - — — =Х (Х,У, +Х,У )+

2 .(Х) г г

24(Х (Х,У +Х,У,)+Х (Х У,+Х У,)

Таким образом, благодаря сокращению числа вычисляемых переменных удается упростить устройство.

Ф о р м у л а и з обретения

Вычислитель ошибок помехоустойчивого декодера, содержащий преобразователь кода, элемент ИЛИ, блок сумматоров, первые, вторые и третьи выходы которого подключены соответственно к первым входам первого перемножителя, входам квадратора и вторым входам первого перемножителя, выходы которого соединены с соответствующими первыми входами первого сумматора, выходы которого подключены к входам элемента ИЛИ-НЕ, выход которого соединен с первым входом элемента И, выходы квадратора подключены к соответствующим вторым входам первого сумматора и первым входам второго перемножителя, выходы которого соединены с первыми входами первого блока элементов И, выходы которого подключены к соответствующим первым входам второго сумматора, второй блок элементов И, выходы которого подключены к соответствуюшим вторым входам второго сумматора, выходы которого являются выходами вычислителя, выход элемента И соединен, с вторым входом первого блока элементов И, первые входы блока сумма-. торов являются первыми входами вычислителя, вторые и третьи, четвертые и пятые, шестые и седьмые входы блока сумматоров соответственно объединены и являются вторыми, третьими и четвертыми входами вычислителя, восьмые входы блока сумматоров и первые входы второго блока элементов И соответственно объединены и подключейы к вторым входам вычислителя, отличающийся тем, что, с целью упрощения устройства, четвертые выходы блока сумматоров подключены непосредственно к входам элемента ИЛИ и через преобразователь

В !295532 б кода к соответствующим вторым входам мента И, второй вход второго блока второго перемножителя, выход злемен- элементов И подключен к выходу элета ИЛИ соединен с вторым входом эле- мента ИЛИ-НЕ.

Составитель О. Ревинский

Редактор О, Юрковецкая Техред Л.Сердюкова Корректор Т. Колб

Заказ 628/62 Тираж 902 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4