Адаптивное устройство анализа цифровых сигналов

Иллюстрации

Показать всеРеферат

Изобретение относится к области радиотехники и может быть использовано в системах обработки цифровой информации когерентно-импульсных радиолокационных станциях кругового или секторного обзора пространства. Цель / изобретения - повышение быстродействия устройства. Адаптивное устройство содержит аналого-цифровой преобразователь 1, фильтр 2 подавления помехи и блок 4 дискретного преобразователя Фурье. В устройство введен ;блок 3 уменьшения разрядности, ; включающий шифратор и п параллель-, ных каналов, каждый из которых выполнен из последовательно соединенных элемента ИЛИ и ключа. Введение указанного блока уменьшает разрядность обрабатываемых исходных данных. При этом становится возможным осуществить адаптивное изменение разрядности обрабатываемых чисел. 1 з.п. ф-JЬзl, 2 ил. S (Л фи&1 о to со О5 СО. СП 00

(ЩОЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

„„Я0„„129 9 (51) 4 G 01 R 23/16 ф;ъ ..

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPGKOIVIY СВИДЕТЕЛЬСТВУ

Фс 1

ГОСУДАРСТ8ЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3967909/24-21 (22) 24.10.85 (46) 15.03. 87. Бюл. Р 10 (71) Московский авиационный институт им.Серго Орджоникидзе (72) В.Я.Плекин и М М.Леднев (53) 621.317.757 (088.8) (56) Оппенгейм Э. Применение цифровой обработки сигналов. М., 1980, с.347. (54) АДАПТИВНОЕ УСТРОЙСТВО АНАЛИЗА

ЦИФРОВЫХ СИГНАЛОВ (57) Изобретение относится к области радиотехники и может быть использовано в системах обработки цифровой информации когерентно-импульсных радиолокационных станциях кругового или секторного обзора пространства. Цель изобретения — повьппение быстродействия устройства. Адаптивное устройство содержит аналого-цифровой преобразователь 1, фильтр 2 подавления помехи и блок 4 дискретного преобразователя Фурье. В устройство введен блок 3 уменьшения разрядности,; включающий шифратор и и параллель-.

1 ных каналов, каждый из которых выполнен иэ последовательно соединенных элемента ИЛИ и ключа. Введение указанного блока уменьшает разрядность обрабатываемых исходных данных. При этом становится возможным осуществить адаптивное изменение разрядности обрабатываемых чисел. I з.п. ф-л|, ф

2 ил.! !г

Изобретение относится к радиотехнике и может быть использовано в сис темах обработки цифровой информации когерентно-импульсных радиолокационных станциях кругового или секторного обзора пространства для анализа цифровых сигналов.

Цель изобретения — повышение быстродействия путем снижения времени вычисления дискретного спектра эа счет уменьшения разрядности обрабатываемых исходных данных при помощи

:блока уменьшения разрядности, который позволяет осуществить адаптивное изменение разрядности обрабатываемых .чисел, что приводит к повышению быстродействия и снижению времени анализа.

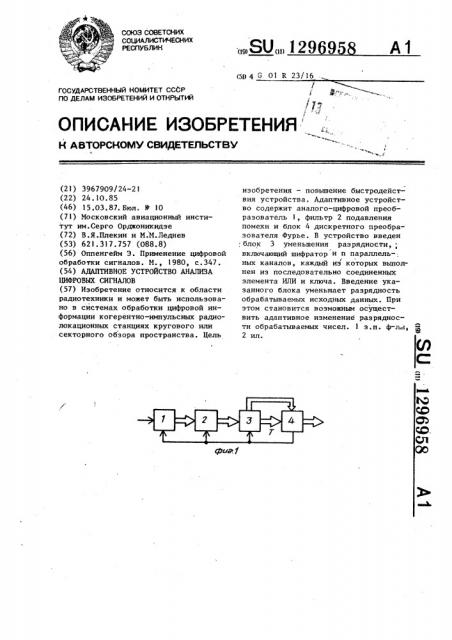

На фиг.! изображена структурная схема предлагаемого устройства; на фиг.2 — структурная схема блока уменьшения разрядности.

Устройство содержит последователь но соединенные аналого-цифровой преобразователь !, фильтр 2 подавления помехи, блок 3 уменьшения разрядности, блок 4 дискретного преобразования Фурье, управляющие вход и выход которого соединены соответственно с управляющим выходом блока уменьшения разрядности и объединенными управляющими входами аналого-цифрового преобразователя, фильтра подавления помехи и блока уменьшения разрядности.

Блок 3 уменьшения разрядности содержит шифратор 5 и и параллельных каналов, каждый из которых выполнен иэ последовательно соединенных элемента ИЛИ 6 и ключа 7, при этом выходом и входом блока уменьшения разрядности являются соответственно выходы ьФючей и вторые входы элемента

ИЛИ б, объединенными со входами соответствующих ключей, а выход элемента ИЛИ .каждого из каналов соединен с первым входом элемента ИЛИ соседнего канала и соответствующим входом шифратора, управляющий вход и выходы которого являются соответственно управляющими входом и выходом блока уменьшения разрядности.

Устройство работает следующим образом.

В когерентно-импульсных радиолокационных станциях кругового нли секторного обзора пространства решается задача обнаружения сигнала, отраженного от движущегося объекта при на96958 2 личин коррелированной помехи, мощность которой, как правило, превосходит мощность полезного сигнала на

60-80 дБ. Эта задача решается системой селекции движущихся целей (СДЦ),.

Формирование потока цифровых сигналов в системе СДЦ происходит следующим образом. Аналоговый видеосигнал поступает на вход аналого-цифрового

10 преобразователя с выхода канала фазового детектирования радиолокационной станции (РЛС), (не показан)., Так как динамический диапазон входного сигнала определяется мощностью коррелированной помехи, то разрядность аналого-цифрового преобразователя (АЦП) I выбирается в соответствии со следующим соотношением к = dt á, (!)

20 где r — число двоичных разрядов,"

d — динамический диапазон входного сигнала, дБ.

Исходя иэ формулы (I) разрядность

АЦП 1 обычно выбирается равной

25 !О !2

Поскольку доплеровское смещение частоты отраженного от объекта сигнала значительно превосходит максимальную доплеровскую частоту сигнала помехи,. тЬ его можно подавить, используя специальные фильтры подавления помехи. При этом на выходе фильтра динамический диапазон сигнала будет снижен.

Уменьшение динамического диапазона приводит к тому, что часть старших разрядов цифрового кода будет все время нулевая и лишь r младших

1 разрядов будут нести информацию.

40 Таким образом, без ухудшения точности обрабатываемых данных появляется возможность снизить разрядность обрабатываемых цифровых кодов до rÄ.

С этой целью в предлагаемое устрой45 ство введен блок 3 уменьшения разрядности

Основу схемы фильтра подавления помехи составляет структурная схема известного двухимпульсного подавите50 ля помех.

Как показывают расчеты при типовых значениях параметров корреляции междупериодная компенсация помехи позволяет снизить число разрядов на

55 3-5.

Аналоговый сигнал преобраэовывается в АЦП 1 в параллельный код при помощи импульсов дискретизации, 58 4 нии, и, следовательно, разрядность входного кода уменьшения до r . В ка1 честве ключей 7 можно использовать

ИМС серии К514КТ1.

С выхода блока 3 уменьшения разрядности цифровой код поступает в блок 4 дискретного преобразования

Фурье, который вычисляет дискретный спектр сигнала в соответствии с известным алгоритмом.

Основу блока 4 ДПФ составляет известная схема цифрового спектро-анализатора.

Таким образом, введение блока уменьшения разрядности позволяет уменьшить число разрядов представления обрабатываемых данных и сформировать сигнал управления блоком вычисления дискретного спектра, что приводит к уменьшению времени обработки.

Указанные преимущества объясняются тем, что при вычислении дискретного спектра обрабатываемых сигналов, для представления которых используется меньшее число разрядов, снижается общее время анализа данных.

Была проведена сравнительная оценка производительности предлагаемого устройства и базового объекта.

В зависимости от типовых значений коэффициента междупериодной корреляции и динамического диапазона входных сигналов выигрьпп по производительности .составляет величину от 20 до 45Х. с

Формула изобретения

1. Адаптивное устройство анализа цифровых сигналов, содержащее последовательно соединенные аналого-цифровой преобразователь и фильтр подавления помехи, а также блок дискретного преобразования Фурье, правляющий выход которого соединен с управляющими входами аналого-цифрового преобразователя и фильтра по- давления помехи, а информационный выход является выходом устройства, о т л и ч а ю щ е е с я тем, что, с целью повьппения быстродействия, в него введен блок уменьшения pasрядности, включенный между выходом фильтра подавления помехи и информационным входом блока дискретного преобразования Фурье„ управляющий выход которого соединен с управляющим входом блока уменьшения разрядности, при этом второй выход этого

3 12969 поступающих с управляющего выхода блока 4. В качестве АЦП 1 можно использовать известную параллельную схему преобразования, которую можно реализовать с использованием компараторов 521СА1-521СА4 и кондирующего элемента с приоритетом К500ИВ165.

Параллельный код поступает в фильтр 2 подавления помехи, который представляет собой систему ме;,дупе- 10 риодной компенсации.

С выхода фильтра 2 подавления помехи цифровой параллельный код поступает в блок 3 уменьшения разрядности. Блок 3 уменьшает разрядность входных данных, а. также вырабатывает управляющий сигнал, который поступа— ет в блок 4 дискретного преобразования Фурье (ДПФ). Цифровой код поступает на вторые входы элементов ИЛИ 6,2р в качестве которых можно использовать интегральные микросхемы (ИМС)

К155ЛЛ1. При этом через время (где — время распространения сигнала в элементе ИЛИ) на выходе эле- 25 мента ИЛИ, соответствующего старшему из разрядов, установится логическое напряжение, которое определяется состоянием старшего разряда. Это напряжение поступит на первый вход 30 элемента ИЛИ, соответствующего соседнему старшему разряду. Напряжение на выходе этого элемента ИЛИ установится с учетом и состояния (r-1)-го разряда. Таким образом, через время

r на выходах элементов ИЛИ 6 установится параллельный единичный код вида:

000...00111...11, в котором число нулей равно числу 40 .старших незначащих разрядов. Этот; единичный код поступает в шифратор 5, который преобразовывает его в параллельный двоичный код, являющийся управляющим сигналом для блока 4 ДПФ.45

Шифратор 5 выполняется на базе ИМС

К500ИВ165, а для согласования логи ческих уровней с ТТЛ можно использовать микросхемы К500ПУ124 и К500ПУ125.

Работа шифратора 5 синхронизирована импульсами дискретизации. Единичный параллельный код с выходов элементов ИЛИ 6 поступает.на управляющие входы соответствующих ключей 7, на входы KoTopblx подается паралль- 55 ный код. В результате этого только

r ключей 7, соответствующих младшим разрядам окажутся в замкнутом состоя1296958 6 ходом элемента ИЛИ, при этом входом блока уменьшения разрядности .являются вторые входы элементов ИЛИ, каждый из которых соединен с вторым входом соответствующего ключа, а

его выходом — выходы ключей, причем выход элемента ИЛИ каждого из каналов, кроме последнего, соединен с первым входом элемента ИЛИ соседнего канала и с соответствующим входом шифратора, выходы которого являются управляющим выходом блока уменьшения разрядности. блока подключен к второму управляющему входу блока дискретного преоб— разования Фурье.

2. Устройство no rx.1, o r л и ч а ю щ е е с я тем, что блок уменьшения разрядности содержит шифратор, управляющий вход которого является управляющим входом блока уменьшения разрядности, и п парал- 10 лельных каналов, каждый из которых содержит элемент ИЛИ и ключ, управляющий вход которого соединен с выСоставитель А.Орлов

Техред А.Кравчук

Редактор А.Ревин

Корректор A,Çèìoêîñoí

Заказ 773/47 . Тираж 731 Подписное

ВИИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r.Óæãîðîä, ул.Проектная 4