Устройство для вычисления функции @

Иллюстрации

Показать всеРеферат

Изобретение относится к цифровой вычислительной технике и может быть использовано для ускоренного вычисления функции arctg у/х. В устройстве регистр 2 аргумента у непосредственно и через блок 7 памяти соединен со входами коммутатора 3, а регистр аргумента X соединен со входом коммутатора 4. Выходы коммутаторов подключены ко входам сумматора 5 и вычитателя 6, выход сумматора 5 связан череё регистр 11 и блок 10 памяти, а также через блок 8 памяти и регистр 12 со входами коммутатора 4. Выход вычитателя 6 через регистр 13 и блок 9 памяти соединен со входом коммутатора 3. Блоки 7, 8, 9, 10 памяти хранят таблицы промежуточных , преобразований.,. Процесс вычисления в устройстве осно .J . и ван на разложении arctg вь р arctg об + arctg fi вытекающей из свойств функции арктангенса, и pear лизуется за три такта сложения и три такта выборки из блоков памяти, 1 ил. i О) ;о

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (11) (51)4 G 06F 7 548

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 3962716/24-24 (22) 11, 10. 85 (46) 15.03.87. Ъюл. Р 10 (71) Омский политехнический институт (72) А.Н.Флоренсов и В.А.?михайлов (53) 681.325(088.8) (56) Авторское свидетельство СССР

Р 1067510, кл. G 06 F 15/31, 1984.

Авторское свидетельство СССР

N 1206767, кл. G 06 Г 1/02, 1984. (54) УСТРОЙСТВО ДЗИ ВЫЧИСЛЕНИЯ ФУНКЦИИ arctg— у,, х (57) Изобретение относится к цифровой вычислительной технике и может быть использовано для ускоренного вычисления функции arctg y/х. В . устройстве регистр 2 аргумента у непосредственно и через блок 7 памяти соединен со входами коммутатора

3, а регистр аргумента Х соединен со входом коммутатора 4. Выходы коммутаторов подключены ко входам сумматора 5 и вычитателя 6, выход- сумматора 5 связан через регистр 11 и блок 10 памяти, а также через блок

8 памяти и регистр 12 со входами коммутатора 4. Выход вычитателя 6 через регистр 13 и блок 9 памяти соединен со входом коммутатора 3. Блоки 7, 8, 9, 10 памяти хранят таблицы промежуточных, преобразований:„

Процесс вычисления в устройстве основан на разложении arcgg

Ф &

1- 8

= arctg о(, + arctg P вытекающей из свойств функции арктангенса, и реа-. лизуется за три такта сложения и три такта выборки из блоков памяти.

1 HJI

1297041

Изобретение относится к вычисли» тельной технике и предназначено для ускоренного вычисления функций

arctg —, необходимои при выполнении у х преобразования декартовых координат в полярные координаты.

Цель изобретения — повьгление точ ности вычислений.

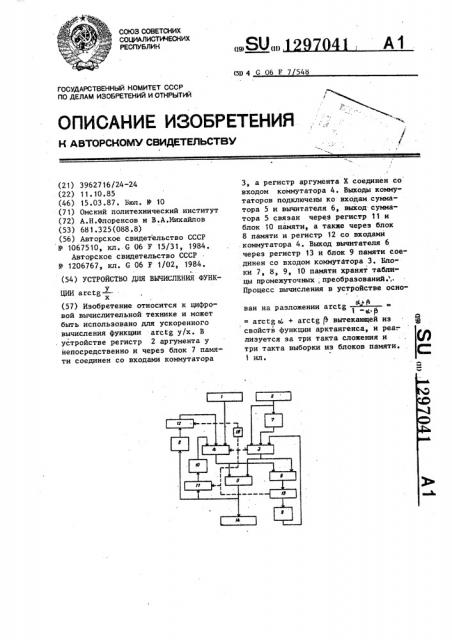

На чертеже изображена блок-схема

10 предлагаемого устройства °

Устройство содержит регистр 1 первого аргумента, регистр 2 второго аргумента, первый и второй коммутаторы 3 и 4, сумматор 5, вычитатель

6, первый, второй, третий и четвертый блоки 7- 10 памяти, первый, второй и третий буферные регистры 11-13, регистр 14 результата и блок 15 синхронизации.

Устройство вычисляет значения функции arctg — путем введения вспоX могательных переменных g. u P, при 25 которых р + = у, 1 - a P = х, и

gs (3 использования формулы arctg

1-oL ф

= arctg М + arctg P, вытекающей из свойств функции арктангенса. Это да- З0 ет для вычисления функции агс д— у х определяющее соотношение

arctg — = arctg(—, + у х 2

35 х) + arctg(—, 2 позволяющее на всех этапах промежуточных, преобразований вычислять вспо" 40 могательные функции от одного аргумента разрядности и а наличие двух аргументов учитывать с помощью суммирования на сумматоре или вычитателе.

Регистр 1 первого аргумента хранит 15 значение аргумента Х, а регистр 2 второго аргумента содержит значение аргумента У, В первом блоке 7 памяти

2 хранится таблица значений (у /4 — 1), во втором блоке 8 памяти — таблица 5р значений квадратного корня, а в третьем и четвертом блоках 9-10 памяти — таблица значений арктангенса.

Устройство работает в три такта, определяемых блоком 15 синхронизации следующим образом. В первом такте сигналы от блока 15, воздействуя на управляющие входы, подключают к выходу первого коммутатора 3 первый его вход, к выходу второго коммутатора 4 третий его вход, а второй буферный регистр 13 фиксирует в этом такте поступающую на его вход информацию.

В первом такте значение у с регистра 2 второго аргумента преобразуется в первом блоке ? памяти, образуя на его выходе значение у /4 — 1, z поступающее через первый вход первого коммутатора 3 на первый вход сумматора 5, на второй вход которого поступает через третий вход второго коммутатора 4 с регистра 1 первого аргумента значение Х. В результате на выходе сумматора 5 формируется

2 значение (—, — 1 + х), запоьынаемое

4 во втором буферном регистре 12.

Во втором такте сигналы от блока

15, воздействуя на управляющие входы, подключают к выходу первого коммутатора 3 третий его вход, к выходу второго коммутатора 4 — первый его вход, а первый и третий буферные регистры 11 и 13 фиксируют в этом такте поступающую на его вход информацию. Выход регистра 2 второго аргумента подключен к третьему входу первого коммутатора 3 со смещением на один двоичный разряд вправо, чтобы обеспечить формирование на этом входе значения кода у/2. На первые входы сумматора 5 и вычитателя б поступает значение у/2, а на вторые их входы с выхода второго блока памяти

8 значение 1у /4 — 1 + х . Ha выходе суммато а о Формируется значение у/2 е у /4 — 1 з х, запоминаемое на первом буферном регистре 11, а на выходе вычитателя 6 — значение у/2— — - ут/4 — 1 т х, запоминаемое а тоетьем буферном регистре 13.

В третьем такте сигналы от блока

15, воздействуя на управляющие входы, подключают к выходу первого и второго коммутаторов 3 и 4 вторые их входы. Третий и четвертый блоки

9-10 памяти выполняют вычисление арктангенса от промежуточных аргументов, а сумматор 5 складывает эти результаты, образуя на своем выходе окончательный результат arctg —, y х запоминаемый в регистре 14 результата.

Составитель 3.Шершнева

Техред М.Ходанич Корректор Т.Колб

Редактор Л.11овхан

Тираж 673 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 782/52

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

3 12970

Формула изобретения

Устройство для вычисления функции

are tg —, содержащее регистр аргумену х та Х, регистр аргумента У, блок синхронизации, сумматор, два коммутатора, три буферных регистра, регистр результата, причем выходы первого и второго коммутаторов соединены с входами первого и второго слагаемых сум- 10 матора соответственно, выход которого соединен с информационными входами регистра результата, первого буферного регистра, первый и второй выходы блока синхронизации соединены 15 соответственно, с управляющими входами первого и второго коммутаторов, о т л и ч а ю щ е е с я тем, что, с целью повышения точности, в него введены вычитатель, блок памяти зна- 20 чений (у /4 — 1), блок памяти значений квадратного корня, первый и второй блоки памяти значений арктангенса, выходы которых соединены с первыми информационными входами пер- 25 вого и второго коммутаторов соответственно, вторые входы которых соединены с выходами регистра аргумента

41 4

Y и регистра аргумента Х соответственно, третьи информационные входы первого и второго коммутаторов соединены с выходами блока памяти значений (у /4 — 1) и второго буферного регистра соответственно, адресный вход блока памяти значений (у /4Я

1) соединен с выходом регистра аргумента Y выходы первого и второго коммутаторов соединены с входами уменьшаемого и вычитаемого вычитателя соответственно, выход которого соединен с информационным входом третьего буферного регистра, выход которого соединен с адресным входом второго блока памяти значений арктангенсов, выход сумматора соединен . с адресным входом блока памяти значений квадратного корня, выход которого соединен с адресным вхоДЬм второго буферного регистра, третИй, четвертый и пятый выходы блока синх1 ронизации соединены с входами синхронизации соответственно первого, втотрого и третьего буферных регистров, выход первого буферного регистра соединен с адресным входом первого блока памяти значений арктангенса.