Устройство для контроля логических схем

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано для контроля и диагностики интегральных логических микросхем и устройств, построенных на их основе. Цель изобретения - повышение быстродействия . Устройство позволяет контролировать сложные логические схемы без разработки специальных тестов за минимальное время. Оно содержит генератор 1 задающих воздействий, первый делитель частоты 2, второй делитель частоты 3, контролируемую схему 4, эталонную логическую схему 5, первый 6 и второй 7 датчики тока, первый 8 и второй 9 фильтры нижних частот, блок вычитания 10, пороговый элемент 11, анализатор спектра 12, аналогоцифровой преобразователь 13, схему сравнения 14, блок постоянной памяти 15, счетчик 16 и блок индикации 17. Кроме того, устройство позволяет определять характер неисправности с точностью до компонента. 1 ил. О) /7 Э :о

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (19) (И) (5D4С06 F 11 26

k (ОПИСАНИЕ ИЗОБРЕТЕНИЯ / ., ГОСУДАРСТ8ЕННЫЙ КОМИТЕТ СССР

flO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ угх

H A BTOPCHQMV СВИДЕТЕЛЬСТВУ (21) 3961876/24-24 (22) 05. 10.85 (46) 15.03.87. Бюл. У 10 (72) M.À.Øåïåëåâ, В.М.Бабушкин, Л. Ф.Чумак и Д.А.Шушко (53) 681.3 (088.8) (56) Авторское свидетельство СССР

У 608125, кл. G 05 В 23/02, 1976.

Авторское свидетельство СССР

У 656064, кл. G 06 F 11/26, 1977. (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЛОГИЧЕСКИХ СХЕМ (57) Изобретение относится к вычислительной технике и может быть использовано для контроля и диагностики интегральных логических микросхем и устройств, построенных на их основе.

Цель изобретения — повышение быстродействия. Устройство позволяет контролировать сложные логические схемы без разработки специальных тестов за минимальное время. Оно содержит генератор 1 задающих воздействий, первый делитель частоты 2, второй делитель частоты 3 контролируемую схему 4, эталонную логическую схему 5, первый

6 и второй 7 датчики тока, первый 8 и второй 9 фильтры нижних частот, блок вычитания 10, пороговый элемент

11, анализатор спектра 12, аналогоцифровой преобразователь 13, схему сравнения 14, блок постоянной памяти

15, счетчик 16 и блок индикации 17.

Кроме того, устройство позволяет определять характер неисправности с точностью до компонента. 1 ил.

С:

1 t2

Изобретение относится к автоматике и вычислительной технике и может быть использовано для контроля и диагностирования интегральных логических микросхем и устройств, построенных на их основе.

Целью изобретения является повышение быстродействия.

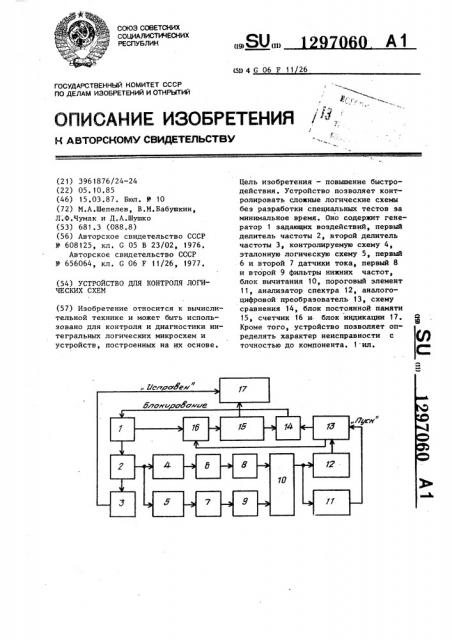

На чертеже показана структурная схема устройства.

Устройство содержит генератор 1 задающих воздействий, первый делитель частоты 2, второй делитель час-. тоты 3, контролируемую схему 4, эталонную схему 5, первый б и второй 7 датчики тока, первый 8 и второй 9 фильтры нижних частот, блок вычитания 10, пороговый элемент 11, анализатор спектра 12, аналого-цифровой преобразователь (АЦП) 13, схему сравнения 14, блок 15 постоянной памяти, счетчик 16 и блок 17 индикации.

Устройство работает следующим образом.

Генератор 1 вырабатывает высокочастотный импульсный сигнал, который с помощью первого делителя частоты преобразуется в множество сигналов некратных частот. Каждый из этих сигналов поступает на соответствующий вход контролируемой схемы 4 и эталонной схемы 5. Первый 6 и второй 7 датчики тока вырабатывают сигналы, закон изменения которых соответствует изменениям тока в цепях контролируемой и эталонной логических схем соответственно. Первый 8 и второй 9 фильтры нижних частот производят фильтрацию сигналов с целью . исключения высокочастотных импульсных помех. Блок вычитания 10 определяет разность между сигналами, снимаемыми с датчиков тока. Полученная разность значений сигналов поступает на входы порогового элемента 11 и анализатора спектра 12, При значении рассогласования, превышающем определенную величину, установленную заранее в виде порога срабатывания порогового элемента, на выходе последнего появляется логический сигнал, характеризующий наличие неисправности в схеме 4. Данный сигнал порогового элемента 11 является сигналом пуска для АЦП 13, входы которого соединены с выходами анализатора спектра 12. По окончании преобразования АЦП 13 вырабатывает

97060 2 сигнал разрешающий работу счетчика 16, второй вход которого соединен с генератором 1 задающих воздействий.

При этом счетчик начинает преобразовывать импульсный сигнал в двоичную последовательность, поступающую на адресные входы блока 15. Из блока

15 извлекается информация о возможных неисправностях контролируемой схемы, причем длина "слова" такова, что в первой половине его записана информация о возможной неисправности, а во второй — код неисправности, необходимый для индикации результатов в блоке индикации 17. При совпадении данных, хранящихся в блоке 15, с данными, снимаемыми с АЦП 13, схема 14 сравнения вырабатывает сигнал, блокирующий работу генератора 1 задающих воздействий. При этом блок

17 индикации индицирует характер неисправности. Если же эа время цикла, устанавливаемого в виде коэффициента деления делителя 3 частоты,в блок индикации не. поступают данные о характере неисправности, т.е. не сраба- тывает пороговый элемент, АЦП, счетчик и блок 15, то второй делитель 3 частоты формирует сигнал "Исправен", подаваемый в блок 17.

Формула изобретения

Устройство для контроля логических схем, содержащее генератор задающих воздействий, первый делитель частоты, анализатор спектра, схему сравнения, эталонную схему, блок индикации, причем первый выход генератора задающих воздействий соединен с входом первого делителя частоты,первый выход которого подключен к входу эталонной схемы и является информационным выходом устройства для подключения к входу контролируемой схемы, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия устройства, в него введены второй делитель частоты, счетчик, два датчика тока, два фильтра нижних частот, блок вычитания, пороговый элемент, аналого-цифровой преобразователь и блок постоянной памяти, причем;входы первого и второго датчиков тока подключены соответственно к выходу эталонной схемы и информационному входу устройства для подключения к выходу контролируемой схемы, выходы первого и второго датчиков тока

97060

Составитель И. Сафронова

Редактор Т.Парфенова Техред М.Ходанич Корректор Н.Король

Заказ 782/52 Тираж 673 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

1роиэводственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

3 12 через соответствующие фильтры нижних частот подключены к соответствующим входам блока вычитания, выход разности которого соединен с входами порогового элемента и анализатора спектра, выход которого подключен к информационному входу аналого-цифрового преобразователя, вход запуска которого подключен к выходу порогового элемента, информационный выход аналого-цифрового преобразователя соединен с первым входом схемы сравнения, второй вход которой соединен с выходом информации о возможной неисправности блока постоянной памяти, выход кода неисправности которого подключен к первому входу блока индикации, второй вход которого подключен к выходу второго делителя частоты, вход которого подключен к второму выходу первогб делителя частоты, выход равенства схемы сравнения соединен с входом блокировки генератора задаю- . щих воэдействйй, второй выход кото10 рого соединен с счетным входом счетчика, вход разрешения которого соединен с выходом конца преобразования аналого-цифрового преобразователя, выход счетчика подключен к адресно-!

5 му входу блока постоянной памяти..