Устройство для отладки программ

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано при отладка программ и при создании аппаратной части специализированных устройств, предназначенных дпя отладки программ. Целью изобретения является расширение функциональных возможностей устройства. Устройство для отладки программ содержит блок 1 задания режима отладки, шифратор 2, блок 3 памяти, регистр 4 адреса и регистр 5 данных, триггер 7 управления, триггер 11 готовности, элемент И 12, мультиплексор 6, блок 8 формирования адреса, блок 10 индикации. Сущность изобретения заключается в том. что для осуществления программноаппаратной отладки в среде проектируемого микропроцессорного устройства введены элементы сопряжения магистралей адреса и данных, алгоритм работы которых определяется служебными сигналами управляющей магистрали; для организации режима прямого доступа к памяти в блок установки режимов устройства для отладки программ введены регистр адреса, регистр данных, кодер, формирователь управляющих сигналов, позволяющие передать через элементы сопряжения в магистрали микропроцессорного устройства содержимое регистра адреса и регистра данных при сформированных сигналах данного отладочного режима; для реализации покомандного режима выполнения программ с одновременной индикацией регистров общего назначения и указателя стека микропроцессорного устройства введены триггер управления, счетчик команд программной выборки регистров общего назначения, триггер готовности , делитель, блок формирования адресов памяти, блок динамической инхщкации, светодиодная матрица. 2 3.п. ф-лы, 7 ил, I (Л 1чд СО sa О а 4 .« cftufj

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

<А!1 4 G 06 F 11/28

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

И ASTOPCHOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

Г1О ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

:(21) 3966287/24-24 (22) 16.10.85 (46) 15,03.87. Бюл. 11 - 10 (72) С.К.Киселев, А.И.Гуляев и Ю.Б.Садомов (53) 68 3 (088. 8) (56) Авторское свидетельство СССР

Р 960821, кл. G 06 F 11/00, 1982.

Авторское свидетельство СССР

11 1043657, кл. G 06 F 11/00, 1983 (прототип) . (54) УСТРОЙСТВО ДЛЯ ОТЛАДКИ ПРОГРАММ (57) Изобретение относится к вычислительной технике и может быть использовано при отладке программ и при создании аппаратной части специализированных устройств, предназначенных для отладки программ.

Целью изобретения является расширение функциональных возможностей устройства. Устройство для отладки программ содержит блок 1 задания режима отладки, шифратор 2, блок 3 памяти, регистр 4 адреса и регистр

5 данных, триггер 7 управления, триггер 1! готовности, элемент И 12, мультиплексор 6, блок 8 формирования адреса, блок 10 индикации. Сущность изобретения заключается в том, „.Я0„„1297О64 А 1 что для осуществления программноаппаратной отладки в среде проектируемого микропроцессорного устройства введены элементы сопряжения магистралей адреса и данных, алгоритм работы которых определяется служебными сигналами управляющей магистрали для организации режима прямого

Э доступа к памяти в блок установки режимов устройства для отладки программ введены регистр адреса, ре-, гистр данных, кодер, формирователь управляющих сигналов, позволяющие передать через элементы сопряжения . в магистрали микропроцессорного устройства содержимое регистра адреса и регистра данных при сформирован- ных сигналах данного отладочного режима; для реализации покомандного режима выполнения программ с одновременной индикацией регистров общего назначения и указателя стека микропроцессорного устройства введены триггер управления, счетчик команд программной выборки регистров общего назначения, триггер готовности, делитель, блок формирования адре" сов памяти, блок динамической индикации, светодиодная матрица.

2 з.п. ф-лы, 7 ил.

1 129706

Изобретение относится к вычислительной технике и может быть использовано при отладке программ и тести ровании микропроцессорных устройств и систем. 5

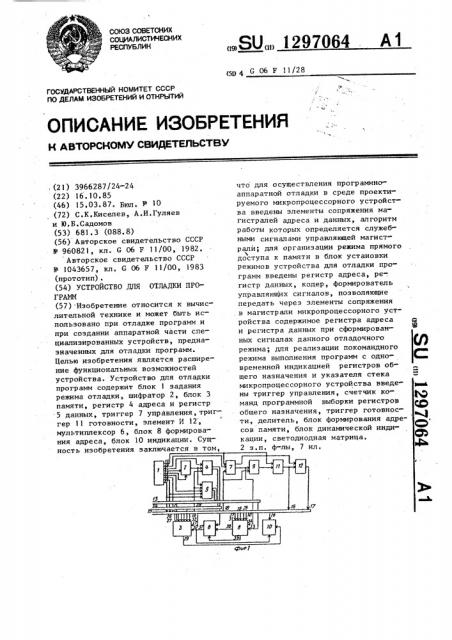

Целью изобретения являет ся р асширение функциональных возможностей устройства отладки программ за счет обеспечения индикации содержимого ре- 10 гистров общего назначения и указателя стека отлаживаемого микропроцессорного устройства в покомандном режиме отладки, На фиг.1 представлена структурная М схема устройства для отладки программ; на фиг.2 — функциональная схема блока задания режима отладки; .на фиг.3 — функциональная схема блока памяти; на фиг.4 — функциональная 20 схема блока формирования адреса; на фиг.5 — функциональная схема блока динамической индикации; на фиг.б— диаграмма функционирования; на фиг. 7блок-алгоритм программы выборки регистра общего назначения (РОН) и УС, Устройство для отладки nporpaMM (фиг. 1) состоит из блока 1 задания режима отладки, шифратора 2, блока

3 памяти, регистра 4 адреса, регист- 30 ра 5 данных, мультиплексора 6 адреса памяти, триггера 7 управления, блока 8 формирования адреса, счетчика 9 команд, блока 10 динамической индикации, триггера 11 готовности, элемента И 12, причем к входу 13 данных отлаживаемого микропроцессорного устройства присоединены регистр

S блоки 3 и 10, к входу 14 адреса— регистр 4, мультиплексор 6, к входу 40

15 управления — блоки 1, З.и 8. Шина адреса содержит 16 разрядов адреса

А0-А15, шина данных — 8 разрядов данных DO-D7, в шину управления вхо- дят типовые сигналы управления микро- 45

ЭВМ: готовность 1б, блокировка памяти 17, начало команды 18, выходы блока i задания режима имеют следующее функциональное назначение: выход

19 пуска, выход 20 признака началь- gp ного выполнения, выход 21 ввода адреса, выход 22 установки режима, тактовый выход 23, выход 24 ввода данных, выход 25 захват памяти, выход

26 чтения памяти, выход 27 записи, вход 28 подтверждения захвата, информационный выход 29 блока 3 памяти, первый 30 и второй 31 тактовые входы устройства, адресный вход 32 блока

4 2

3 памяти, информационный вход 33 бло- . ка 8, вход 34 обнуления блока 8, выход 35 управления мультиплексора блока 8, информационный выход 36 блока 8, выход 37 мультиплексора 6.

Блок 1 задания режима отладки (фиг,2) содержит цифронаборник 38, одновибратор 39, дешифратор 40 управляющих сигналов. Одновибратор предназначен для снятия "дребезга" цифронаборника и формирует тактовый выход блока. Блок задания режима предназначен для формирования сигналов нажатия клавиатуры и управляющих сигналов, инициирующих работу устройства в режиме, заданном оператором с клавиатуры, Шифратор 2 предназначен для кодирования позиционных выходов цифронаборника в двоичный код, который подается на регистры адреса 5 и данных 4. Блок 3 памяти (фиг.3) содержит триггер 41 стека, элементы ИЛИНЕ 42,1-42,5, элементы И-НЕ 43.1- :

43.4, элемент ИЛИ 44, элементы 45.1 и 45.2 оперативной памяти, элемент

46 постоянной памяти, элементы И

47.!.-47.4, 48.1--48 ° 4, Адресные входы элемента постоянной памяти соединены с входом 49 адресного входа 14, адресные входы элементов оперативной памяти подсоединены к выходу мультиплексора 6. Блок памяти реализует программу выборки содержимого внутренних регистров РОН и УС отлаживаемого микропроцессорного устройства в режиме останова или отладки по шагам.

Регистр 4 адреса предназначен дпя хранения адресного шестнадцатиразрядного двоичного слова, набираемого на цифронаборнике 38 в режиме прямого доступа к памяти . В этом режиме на сигнал "Захват памяти" 25 отлаживаемая микроЭВМ отвечает сигналом "Подтверждение захвата" 28, по которому из регистра адреса происходит передача адресного слова на вход 14 адреса.

Регистр 5 данных предназначен для хранения байта данных, набираемого на клавиатуре в режиме прямого доступа к памяти. При поступлении из блока задания режима сигнапа "3aпись памяти" 27 регистр данных передает байт данных на вход 13 данных, при поступлении сигнала "Чтение па- I

7064 4

50

f5 на тактовый вход И, устанавливает в нуль триггер 11 готовности.

Блок 10 динамической индикации (фиг.5) содержит дешифратор 55 адреса, мощные токовые ключи 56 и 57, светодиодную матрицу 58 ° Блок пред- 25 назначен для индикации содержимого

POH и УС. На выходы дешифратора 55 адреса непрерывно поступают адреса

AO-АЗ 37. При поступлении сигнала готовность" нулевого уровня выходы дешифратора поочередно через мощные токовые ключи 56 подключают гори- зонтальные шины светодиодной матрицы.

В соответствии с включенной горизонтальной шиной одновременно на токовые ключи 57 подается байт считываемой информации из блока ОЗУ и подключаются соответствующие вертикальные шины светодиодной матрицы. Таким образом светодиодная матрица индици- 40 рует содержимое POH и УС.

Устройство для отладки программ работает следующим образом.

В исходном состоянии триггеры 7 управления и готовности 11 устанавли-45 ваются в нулевое и единичное состояние соответственно и на микропроцессорное устройство поступают управляющие сигналы 16 и 17, обеспечивающие

его непрерывное выполнение программ.

При задании пошагового режима отладки блок задания режима формирует сигнал "lllar" 20, который поступает на D-вход триггера 7 управления, на тактовый вход которого поступает управляющий сигнал "Начало команды"

18. Таким образом, по началу следующей команды отлаживаемой программы пользователя триггер 7 управления

3 129 мяти" 26 в регистр данных заносится байт, считанный из памяти.

Мультиплексор б предназначен для коммутации разрядов MAO-МАЗ входа адреса или разрядов АО-АЗ 36 блока формирования адреса и подачи на одноименные адресные входы блока 3 памяти.

Блок 8 формирования адреса и уп-. равления мультиплексором (фиг.4) содержит делитель 50 тактовой частоты, триггер 51 стековых операций, элементы И 52, элемент ИЛИ-НЕ 53, счетчик 54 адреса. Блок 8 предназначен для фиксации стековых операций при выполнении программы выборки содержимого POH и УС отлаживаемого микропроцессорного устройства и организации адреса хранения содержимого POH и УС в блоке 3 памяти. переходит в другое устойчивое состояние, и элемент И 12 формирует управляющий сигнал "Блокировка памяти" 17, который отключает основную память микропроцессорного устройства, в которой располагается отлаживаемая программа. Этот же сигнал является сигналом разрешения работы с блоком

3 памяти устройства отладки программ (фиг.б), Далее сигнал с триггера 7 управления открывает счетчик 9 команд, который осуществляет подсчет числа команд блока 3 памяти. Сигнал переноса счетчика 9 команд поступает

Микро проц ес сор ное у стр ой ст во при получении сигнала Блокировка памяти"

17 не приостанавливает свою работу, а принимает единичный байт, соответствующий коду команды "КЕЗТАКТ" (7), так как шина 13 данных при блокировке основной памяти имеет высокий логический уровень. При выполнении

2 и 3 циклов команды RESTART (7) производятся две стековые операции— пересылка содержимого счетчика команд в стек. В этом случае устанавливаются в единицу триггеры 41 и 51, а мультиплексор 6 подключает адреса

AO-АЗ 36 счетчика 54 на адресные входы 45 оперативной памяти блока

3 памяти, счетчик 54 уменьшает свое состояние на 2 (число пересылок в стек).

Таким образом, оперативная память

45 выполняет функцию стека, а счет-. .чик 54 — указателя стека, который начинает работу с нулевого состояния независимо от текущего состояния указателя стека микропроцессорного устройства, Выполнив команду "RESTART" микропроцессорное устройство устанавливает адрес 0038 (Н) и начинает выполнение программы выборки POH u

УС (фиг.7), хранимой в элементе 46 постоянной памяти. Счетчик 9 команд отсчитывает с нулевого состояния число выполняемых команд.

При выполнении программы выборки

POH и указателя УС (фиг.7) в том случае, когда обращение к оперативной памяти 45 происходит не по стековым операциям, основным признаком вазделения оперативной и постоянной памяти является разряд МА7 для элемента 45 МА7 =.>."0", для элемента МА7

1297064

=) "1". Поэтому первая команда постоянной памяти (46),, которая осуществляет запись пары регистров Н, Ь в оперативную память (45), содержит в третьем байте команды признак

МА7 =>1.

Команды 6-8 служат для восстановления указателя стека микроЭВМ в результате выполненных стековых команд (фиг.7). Количество стековых опера- 1О ций РОН -+ стек, стек — +РОН одинаково, поэтому реверсивный счетчик 54 возвращается в исходное состояние.

Последняя команда "RETURN" возвращает микропроцессорному устройству 15 содержимое программного счетчика.

При этом счетчик 9 команд устанавливается в состояние 1111 (соответствующее числу команд программы выборки POH и УС) и формирует сигнал 20 переноса (фиг.6), Сигнал переноса снимается сигналом Начало команды", т.е. текущей команды пользователя.

Задним фронтом переноса счетчика 9 на выходе триггера I! готовности 25 устанавливается сигнал Готовность"

Сигнал "Пуск" устанавливает триггер 7 управления в нулевое состояние, а триггер 11 и сигнал "Готовность" .

16 — в единичное состояние, микропроцессорное устройство снимает состояние Ожидание" и выполняет ранее принятую команду пользователя. При поступлении следующего сигнала "Начало команды" 18 новой команды происходит установка в единицу триггера

7, элемент И 12 формирует сигнал

"Блокировка памяти" 17 и микроЭВМ принимает единичный байт — код команды "RESTART" (7). Затем снова повторяется цикл выборки POH и УС.

Для перехода в непрерывный режим прогона программ из блока 1 задания режима сигнал "Шаг" 20 переводится в нулевой уровень и подается сигнал

"Пуск" 19, При этом сигнал "Готовность" 16 принимает единичный уровень, "Блокировка памяти" 17 — нулевой уровень и микропроцессорное устройство продолжает автоматически прогон программы пользователя. низкого логического уровня и на выходе элемента И 12 снимается сигнал блокировки памяти 17.

Микропроцессорное устройство принимает код команды программы пользователя из разблокированной памяти и устанавливается в состояние ожидания, Одновременно разблокируется делитель 50, выходной сигнал которого запускает счетчик 54 в пересчетный режим, Мультиплексор 6 коммутирует разряды счетчика 54 на адресные входы 37 оперативной памяти 54 и производится периодическое считывание хранящего в оперативной памяти

45 содержимого POH и УС. Те же раз- ряды адреса AO-A3 37 с выхода мультиплексора 6 и считываемое содержимое D0-97 29 подаются на блок 10 динамической индикации. Блок 10 обеспечивает дешифрацию аде ..ов и подачу считываемой информации и управляющих сигналов на входы мощных элементов (56 и 57). Мощные элементы (56) подключают горизонтальные шины выбора индикаторов РОН, УС, а другие мощные элементы (57) — вертикальные шины разрядов содержимого РОН, УС светодиодной матрицы 5,8, Индикация POH и УС непрерывно продолжается до появления следующего сигнала "Пуск" 19.

Формула и з о б р е т ения

l Устройство для отладки программ, содержащее блок задания режима отладки, шифратор, регистр адреса и регистр данных, причем информационный и тактовый выходы блока задания режима соединены соответственно с информационным и тактовым входами шифратора, выход которого соединен с информационными входами регистра адреса и регистра данных, выходы разрешения ввода адреса и ввода данных блока задания режима отладки

v соединены соответственно с входом записи регистра адреса и первым входом записи регистра данных, о т— личающееся тем, что, с целью расширения функциональных возможностей устройства за счет обеспечения индикации регистров общего назначения и указателя стека в режиме пошагового выполнения программы, в устройство введены триггер управления, триггер готовности, счетчик команд, элемент И, блок памяти, мультиплексор, блок индикации и блок формирования адреса, причем выход пуска блока задания режима отладки соединен с нулевым и единичным входами соответственно триггера управления и триггера готовности, 1297064 8

40 3. Устройство по и. 1, о т л и— ч ающе е ся тем, чтоблокпамяти содержит триггер стека, пять элементов HJIH-HE, элемент ИЛИ, четы1 ре элемента И-НЕ восемь элементов

45 И, два элемента оперативной памяти и элемент постоянной памяти, причем первый тактовый вход и вход признака чтения блока соединены соответственно с тактовым входом триггера стека и с первым входом первого элемента И-НЕ, выход которого соединен с первым входом элемента ИЛИ, с первым входом первого элемента HJIH-HE и с первым инверсным входом чтения элемента постоянной памяти, выход триггера стека соединен с вторым входом первого элемента HJIH-НЕ и с вторым входом второго элемента И-НЕ, выход которого соединен с втовыходы признаков пошагового выполнения и захвата памяти блока задания режима отладки соединены- соответственно с информационным входом тригге" ра управления и с выходом требования захвата памяти устройства, выход признака чтения памяти. блока задания режима отладки соединен с входом записи регистра данных, с входом чтения блока памяти и с входом суммирования адреса блоки формирования адреса, выход признака записи блока задания режима отладки соединен с входом чтения регистра данных, с входом записи блока памяти и с входом уменьшения адреса блока формирования адреса, вход подтверждения захвата устройства соединен с входом чтения регистра адреса и с входом разрешения записи регистра данных, вход данных устройства через двустороннюю магистраль соединен с информационными входами-выходами регистра данных и блока памяти и информационным входом блока формирования адреса, выход ре гистра адреса соединен с первым информационным входом мультиплексора адреса и с аДресным входом блока памяти, признак начала команды устройства соединен с тактовым входом триггера управления и со счетным входом счетчика команд, инверсный выход триггера управления соединен с входом начальной установки счетчика команд и входом обнуления блока формирования адреса, выход переполнения счетчика команд соединен с нулевым входом триггера готовности, единичные выходы триггеров управления и готовности соединены соответственно с первым и вторым входами элемента И, выход которого соединен с входом блокировки блока памяти, единичный выход триггера готовности соединен с входом разрешения индикации блока индикации, с входом готовности блока формирования адреса и с входом обращения блока памяти, тактовый вход устройства соединен с тактовым входом блока памяти и с первым тактовым входом блока формирования адреса, второй тактовый вход устройства соединен с вторым тактовым входом блока формирования адреса, информационный выход и выход выбора адреса которого соединены соответственно с вторым информационным входом и управляющим входом мультиплексора, выход которого соединен с вторым

У

-c5

35 адресным входом блока памяти и с первым информационным входом блока индикации, информационный выход блока памяти соединен с вторым информационным входом блока индикации.

2. Устройство по п.1 о т л и чающее с я тем, что блок:, формирования адреса содержит первый и второй счетчики, триггер, первый и второй элементы И и элемент ИЛИ-НЕ, причем вход готовности блока соединен с входом начальной установки первого счетчика и с инверсным входом начальной установки триггера, инверсный выход которого является управляющим выходом устройства, прямой выход триггера соединен с первыми входами первого и второго элементов И, выход переполнения первого счетчика и выход первого элемента И соединены соот вет ственно с первым и вторым входами элемента ИЛИ-НЕ, выходы второго элемента И и элемента ИЛИ-НЕ соединены соответственно с входами прямого и инверсного счета, второго счетчиКа, выходы которого образуют информационный выход блока, второй вход первого элемента И, второй вход второго элемента И, информационный вход триггера, счетный вход первого счетчика и тактовый вход триггера являются соответственно входом признака записи блока, входом признака чтения блока, информационным входом блока, первым и вторым тактовыми входами блока, вход начальной установки второго триггера является входом обнуления блока.

9 129 рым инверсным входом чтения элемента постоянной памяти, выход первого элемента ИЛИ-НЕ соединен с первым входом второго элемента ИЛИ-НЕ, выход которого соединен с первым входом третьего элемента И-НЕ, вход признака записи блока соединен с первым входом четвертого элемента

И-НЕ и с первым входом третьего элемента ИЛИ-НЕ, вход признака блокировки соединен с нулевым входом триггера стека, с вторым входом первого элемента И-НЕ и с вторым входом четвертого элемента И-НЕ, выход элемента ИЛИ соединен с вторым входом третьего элемента И-НЕ, выход которого соединен с вторым входом третьего элемента ИЛИ-HЕ, выход которого соединен с входом признака чтения первого и второго элементов оперативной памяти, выход четвертого элемента

И-НЕ соединен с признаком записи первого и второго элементов оперативной памяти, вход признака обращения блока соединен с входом четвертого элемента ИЛИ-НЕ, выход которого соединен с вторым входом второго элемента ИЛИ-НЕ и с первыми входами первого, второго, третьего, четвертого, пятого, шестого, седьмого и

aocbMor элементов И, первый адрес7064 1О ный вход блока. соединен с адресными входами элемента постоянной памяти, вход пятого элемента ИЛИ-НЕ соединен с соответствующим разрядом первого адресного входа блока, выход пятого элемента ИЛИ-НЕ соединен с вторыми входами второго элемента ИНЕ и элемента ИЛИ, второй адресный вход блока соединен с адреснымн вхо10 дами первого и второго элементов оперативной памяти, разрядные выходы которых соединены с вторыми входами первого, второго, третьего, четвертого, пятого, шестого, седьмого и восьмого элементов И, выходы первого, второго, третьего, четвертого, пятого, шестого, седьмого и восьмого элементов И через двустороннюю информационную магистраль соединены с ин20 формационными входами первого и второго элементов оперативной памяти и входами данных, информационный вход триггера стека соединен с соответствующим разрядом информационной магистрали блока, выходы элемента постоянной памяти соединены через двустороннюю информационную магистраль с информационными входами первого и второго элементов оперативной памяти, информационные выходы которых соединены с информационным выходом блока.

1297064

1297064

1 297 064 маюй Юмжч

nonb3olomen ncr b Войтеку èà.Ю! 297064

Составитель И.Сигалов

Редактор Т.Парфенова Техред Л.Сердюкова Корректор Л.Патай

Заказ 783/53 Тираж 673 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул. Проектная, 4