Устройство интерполяции для отображения графической информации

Иллюстрации

Показать всеРеферат

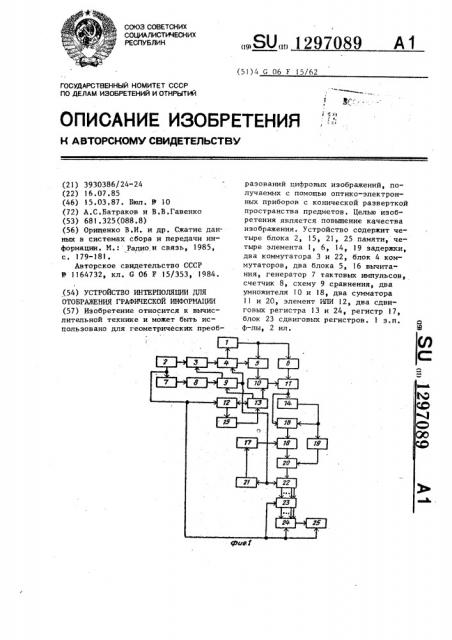

Изобретение относится к вычислительной технике и может быть использовано для геометрических преобразований цифровых изображений, получаемых с помощью оптико-электронных приборов с конической разверткой пространства предметов. Целью изобретения является повьшение качества изображения. Устройство содержит четыре блока 2, 15, 21, 25 памяти, четыре элемента 1, 6, 14, 19 задержки, два коммутатора 3 и 22, блок 4 коммутаторов , два блока 5, 16 вычитания , генератор 7 тактовых импульсов, счетчик 8, схему 9 сравнения, два умножителя 10 и 18, два сумматора 11 и 20, элемент Ш1И 12, два сдвиговых регистра 13 и 24, регистр 17, блок 23 сдвиговых регистров. 1 з.п. ф-лы, 2 ил. (Л tsD СО о 00 со фиеЛ

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51)4 4G 06 F 15/62

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕКНЫЙ HOMHTET СССР

ПО ДЕЛАМ ИЗОБРЕТЕКИЙ И ОТКРЫТИЙ (21) 3930386/24-24 (22} 16.07.85 (46) 15.03.87. Бюл. Р 10 (72) А.С.Батраков и В.В.Гавенко (53) 681.325(088.8) (56) Орищенко В.И. и др. Сжатие данных в системах сбора и передачи информации. М.: Радио и связь, 1985, с. 179-181.

Авторское свидетельство СССР

Р 1164732, кл. С 06 F 15/353, 1984. (54) УСТРОЙСТВО ИНТЕРПОЛЯЦИИ ДЛЯ

ОТОБРАЖЕНИЯ ГРАФИЧЕСКОЙ ИНФОРМАЦИИ (57) Изобретение относится к вычислительной технике и может быть использовано для геометрических преоб„„SU„1297089 А1 раэований цифровых изображений, получаемых с помощью оптико-электронных приборов с конической разверткой пространства предметов. Целью изобретения является повьппение качества изображения. Устройство содержит четыре блока 2, 15, 21, 25 памяти, четыре элемента 1, 6, 14, 19 задержки, два коммутатора 3 и 22, блок 4 коммутаторов, два блока 5, 16 вычитания, генератор 7 тактовых импульсов, счетчик 8, схему 9 сравнения, два умножителя 10 и 18, два сумматора

11 и 20, элемент ИЛИ 12, два сдвиговых регистра 13 и 24, регистр 17, блок 23 сдвиговых регистров. 1 з.п. ф-лы, 2 ил, 9

7089 2 фазовый генератор сдвиговых импульсов, запускаемый управляющим импульсом), При этом количество регистров и их расположение в блоке 23 определяется в соответствии с выражением

m,.=int(L„.), где i равно 1,2,...,n— порядковый номер сдвигового регистра. Счетчик 8 расчитан íà и-1 импульсов. Сдвигоный регистр 24 сос10 тоит иэ генератора сдвиговых импульсов, запускаемого управляющим импульсом, поступающим на управляемый вход регистра 24 и собственного сдвигового n — - элементного регистра.

15 Элемент задержки 14 имеет длительность задержки, равную периоду следования синхроимпульсов, т.е. периоду сканирования

-2 4

Т = - — ек gQ

1 129

Устройство интерполяции для отображения графической информации.

Изобретение относится к вычислительной технике и может быть применено для геометрических преобразований цифрового изображения, получаемого с помощью оптико-электронных приборов с конической разверткой пространства предметов.

Цель изобретения — поныщение качества изображения за счет устранения геометрических и яркостных искажений при его преобразовании, На фиг. 1 приведена функциональная схема устройства, на фиг. 2— пример конкретной реализации блока коммутаторов.

Устройство содержит (фиг. 1) первый элемент задержки 1, первый блок

2 памяти, второй коммутатор З,блок

4 коммутаторов, первый блок 5 вычитания, второй элемент задержки 6, генератор 7 тактовых импульсов, счетчик 8, схему 9 сравнения, первый умножитель 10, первый сумматор

11, элемент ИЛИ 12, второй сдниговый регистр 13, третий элемент задержки 14, четвертый блок 15 памяти, второй блок 16 вычитания, регистр 17, второй умножитель 18, четвертый элемент задержки 19 сумматор

20, третий блок памяти 21, первый коммутатор 22, блок 23 сдвигових регистров, первый сдвиговый регистр

< 24, второй блок 25 памяти.

Блок 4 коммутаторов (фиг. 2) содержит коммутаторы 26-28, элемент

И 29, элемент задержки 30. . I

Сдвйговый регистр 13 содержит два связанных последовательных регистра. При этом первый выход сдвигового регистра 13 соединен с разрядами целой части числа, записанного в первый регистр. Второй выход сдвигового регистра 13 связан с раз" рядами дробной части числа, записанного во второй регистр. Блоки 15 и

21 выполнены циклическими, что обеспечивает многократное, последовательное считывание записанных в них предварительно значений М; и К„,. Для пред варительной записи указанных массивов блоки 15 и 21 имеют специальный вход (на фиг. 1 не показан}.Блок 23 сдвиговых регистров состоит из и сдвиговых,m, — элементных регистров и может быть выполнен, например, на приборах с, зарядовой связью (ПЗС) (в этом случае блок содержит многоЭлемент задержки 30 имеет длительность задержки, равную периоду следования видеосигналов at. При ко25 нической развертке пространства предметов траектория визерного луча в плоскости предметов представляет собой дугу окружности с радиусом R, При этом развертка по строке осуще3п стнляется с помощью сканирующего элемента с угловой скоростью вращения

<ду, а развертка по кадру — за счет поступательного перемещения оптикоэлектронного прибора -co скоростью W.

35 фотор е F ист рация полученных видео сигналов должна производиться синхронно и синфазно процессу формирования исходного иэображения. Однако эта синхронность и синфазность не всего да может быть обеспечена ввиду ряда технических причин (погрешность изготовления и юстировки оптических деталей и т.д.), что приводит к заметным геометрическим и яркостным

45 искажениям получаемых изображений.

Поэтому предлагается для повьпнения качества сканерных изображений осуществлять их геометрические преобразования к ортогональной проекции, gp т.е, нидеосигнал, соответствующий дуговому растру, трансформировать в видеосигнал, соответствующий линейно-строчному растру, образующему сетку с квадратными ячейками ape

55 путем интерполяционного восстановления значений видеосигнала в узлах сетки. Используя формулы линейной интерполяции по строке (по оси У) и по кадру по осн Х), т.е.

1297! »89 (3) (4) ьх (6) где: Ч»

1п

2 !!» й

„(М. — 1) ьХ=(-2W,У) /(q а„), 9;=arctg (Z Y. (7) (8) ), (9) В„=В, +(В. -В„) К„, f1)

» 1»»»»» где N . . — — номер видеосигнала в дуго I вой строке;

L. — номер видеосигнала в дуговом столбце;

i-1,2,...,п — номер видеосигнала в линейной строке;

j=1,2,...,1 — номер видеосигнала в линейном столбце;

В,, — исходные видеосигналы;

— преобразованные по строке

У, видеосигналы;

В .. — преобразованные по строке

Х !,» и по кадру видеосигналы, К,К вЂ” коэффициенты интерполяции по строке и по кадру соответственно, при этом п Щ )ь, В.„.=L . -int (L; ), 9 - Р

N,= +1, (5) ! Ь3 а

Щсов!! -cos P )-VfintgN )-N, ) at начальный угол поворота сканирующего элемента; оператор выделения целой части действительного числа; период квантования видеосигнала;

i-тое значения угла поворота сканирующего элемента; количество видеосигналов в строке исходного изображения, причем

У; =Rsin9,-ьХ(i-1), (I0) где Z — картинное расстояние;

h " коэффициент использования развертки;

Н вЂ” расстояние от центра проек,тирования задней узловой точки объектива до плоскости предметов; ш " знаменатель масштаба; получим значения преобразованного видеосигнала В,, фоторегистрация

35 0

55 которого значитепьно проще, чем исходного. Поэтому преобразованное по предложенному алгоритму и зарегистрированное пзображение свободно от геометрических и яркостннх искажений, присущих исходному изображению.

Устройство работает следующим об-. разом.

В исходном состоянии: в блоке 2 построчно записан исходный фрагмент иэображения, счетчик 8 обнулен, коммутатор 3 и блок 4 закрыты, генератор 7 тактовых импульсов отключен, сдвиговнй регистр 13 и блок 25, блок сдвиговых регистров 23, сдвиговый регистр 24, регистр 17 обнуленн, коммутатор 22 соединяет свой вход с последним своим выходом, в блоке 15 записан массив из п значений N. в ! блоке 21 записан массив из и значений коэффициентов К„

При включении блока 2 на воспроизведение с его первого выхода построчно последовательно.поэлементно на вход коммутатора 3 поступают цифровые видеосигналы с частотой

=) /ët ь

Со второго выхода блока 2 строчные синхроимпульсы поступают на вход генератора 7 тактовых импульсов, который запускается для формирования и импульсов с частотой 1 ., блока 23 сдвиговых регистров, благодаря чему осуществляется сдвиг на один элемент содержимого всех сдвиговых регистров этого блока, сдвигового регистра 24 и блока 25, благодаря чему обеспечивается перезапись строки обработанного изображения из сдвигового регистра 24 и блока 25, благодаря чему обеспечивается перезапись строки обработанного изображения из сдвигово- го регистра 24 в блок 25, на первый вход элемента ИЛИ 12, с выхода кото » рого они поступают на управляющий вход блока 15, обеспечивая этим считывание из блока 15 и запись через первый вход сдвигового регистра 13 в первый его регистр значения N;.

Выходные импульсы генератора 7 тактовых импульсов поступают на вход счетчика 8, который подсчитывает ко личество поступивших импульсов i °

С выхода. счетчика 8 текущее значение числа импульсов постоянно поступает на первый вход схемы 9 сравнения, на второй вход которой поступает значение целой части int(N ) 5 129 числа, записанного в первый регистр сдвигового регистра 13, с первого выхода этого регистра. При равенстве значений на обоих входах схемы 9 сравнения на первом и втором выходах последней формируются управляющие импульсы различной длительности. При этом на первом выходе формируется управляющий импульс, равный по длительности 2/Е т.е. равный периоду следования двух . видеосигналов, На втором выходе формируется импульс половинной длительности, т.е. равный длительнос ти периода следования одного видеосигнала. С первого выхода схемы сравнения 9 импульс поступает на управляющий вход коммутатора 3 и открывает его на время длительности управляющего импульса, т.е, на время периода следования двух видеосигналов {i-того и (i+I)-го. С выхода открытого ключа 3 видеосигналы

В и В., последовательно поступа а +ц ют на первый вход блока 4. Со второго выхода схемы сравнения 9 импульс поступает на вторые входы блока 4 и элемента ИЛИ 12 и на управляющие входы сдвигового регистра 13, блока

21 обеспечивает считывание и запись очередного i-ro значения коэффициента К . в регистр 17. Поступление

Х1 первого управляющего импульса Обеспечивает переключение коммутатора

22 для прохождения входного видеосигнала на первый выход последнего.

Очередные i-ые управляющие импульсы переключают коммутатор 22 для прохождения входного видеосигнала коммутатора 22 В ..на соответствующий

xij его -ый выход. Управляющий импульс также обеспечивает сдвиг на один элемент содержимого сдвигового регистра 13, т.е. перезапись числа N. с его первого во второй его регистр, С выхода элемента ИЛИ 12 импульс поступает на управляющий вход блока

15, благодаря чему очередное значение — число N. считывается из бло1+1 ка 15 и записывается в первый регистр

I сдвигового регистра 13. Поступление управляющего импульса на второй вход блока 4, а второго видеосигна ла В - на второй выход блока 4. С й. д, первого выхода блока 4 N-ый видеосигнал через элемент задержки 1, задерживающий на период следования видеосигналов at поступает через элемент задержки 6, в котором задер9 6 живается на время Обработки випеосигналов в блоках 5 и 10, на первый вход сУмматора 10, II на первый вход блока 5 вычитАния одновременно с поступлением на его второй вход (N, )-ro видеосигнала. Выходной сигнал (Р„ -В;„ ) блока 5 вычитания

"1+13 поступает на первый вход умножителя

10, на второй вход которого поступаfg ет дробная часть числа N-, т.е. коэффициент I(„. со второго выхода сдвигового регистра 13, Выходной сигнал (В -В )„К цумножителя 10 поступает на второи вход сумматора 11, где суммируется с соответствующим значением В„ . С

14 выхода сумматора 11 частично обработанный видеосигнал В .., поступает

la непосредственно на первый вход бло2ц ка 16 вычитания и через элемент задержки 14, в котором задерживается

EIa время периода следования строчных синхроимпульсов Т,„, т,е. на период следования строк изображения, на второй вход блока 16 выхода вычитания, в котором вычисляется значением (Г .„ -В „ „ ),и через элемент за— ю чiь

1 держки ld, где задерживается на время обработки видеосигналов в блоках

30 16 и 18, на второй вход сумматора 20. С вьгхода блока 16 вычитания видеосигнал (В„ -В„„), поступает на пер,ь,„, вый вход умножителя !8, на второй, вход которого с выхода регистра 17

35 поступает i-oe значение коэффициента I(„,. Выходной: сигнал (В -R )"

I Y;t.- ЧД;

К умножителя 18 поступает на втоХ; рой.вход сумматора 20, где суммируется с соответствующим значением

4« . С выхода сумматора 20 Обрабоо танный видеосигнал В,.„. поступает на вход коммутатора 22. С соответствующего выхода коммутатора 22 (в зависимости от положения этого коммута45 тора„ т.е, от значения i) видеосигнал В,. поступает на соответствуюх1„. щий х.-ый вход блока сдвиговых регистров 23, в котором, продвигаясь с различной задержкой (в зависимости от номера регистра i) следовательно, в зависимости от значения m.

1 видеосигналы Б .. достигают соответствующего х-го элемента выходного сдвигового регистра 24 и записываются в

55 нем. В последующих тактах и строках обработка исходных видеосигналов производится аналогично.

Блок 4 работает следующим обраЗОМ, 7 12970

Видеосигнал H., с первого входа

t J блока 4 поступает одновременно на информационные входы коммутаторов

26-28. Управляющий сигнал со второго входа блока 4 поступает на вто5 рой вход коммутатора 26, открывая его для прохождения видеосигнала

В,, на первый выход блока 4, на первий вход логического элемента И 29 непосредственно и на вторые входы щ элемента И 29 и коммутатора 28 через элемент задержки 30, который задерживает управляющий импульс на период следования видеосигнала ьt, Благодаря этому коммутатор 28 открывается для прохождения на второй выход блока 4 видеосигнала B;„..

Если на первый вход элемента И 29 поступит следующий управляющий импульс одновременно с предыдущим, который поступит на второй его вход с задержкой на время gt то выходной сигнал элемента И 29 поступит на второй вход коммутатора

27 и откроет его для прохождения на первый выход блока 4 видеосигналаВ;„.

Таким образом, описанный алгоритм работы предлагаемого устройства обеспечивает реализацию выражений (1) и (2), что позволяет осуществить требуемые геометрические преобразования исходных фрагментов сканерных иэображений, устранив при этом за счет такой обработки имеющиеся геометрические и яркостные искажения изображения.

Формула изобретения

Устройство интерполяции для . отображения графической информации, содержащее генератор тактовых импуль.сов, счетчик, элемент ИЛИ, два сдвиговых регистра, .блок коммутаторов, первый блок вычитания, первый коммутатор, причем выход генератора так„45 товых импульсов соединен со счетным входом счетчика, вход запуска генератора тактовых импульсов соединен с первым входом элемента ИЛИ и с входом управления сдвигом первого сдвигового регистра, второй вход элемента ИЛИ соединен с входами управления и выдачей второго сдвигового регистра и с управляющими нходами 55 первого коммутатора и блока коммутаторов, первый выход блока коммутаторов соединен входом уменьшаемого первого блока вычитания, о т л и-. ч а ю щ е е с я тем, что, с целью повышения качества за счет устранения геометрических и яркостних искажений при его преобразовании изображения, в него введены четыре блока памяти, второй коммутатор, схема сравнения, четыре элемента задержки, второй блок вычитания, два сумматора, два умножителя, блок сдвиговых регистров, регистр, причем выход синхронизации первого блока памяти соединен с выходом запуска генератора тактовых импульсов, с входом управления сдвигом блока сдвиговых реГ гистров и с входом записи второго блока памяти, выход данных перного блока памяти соединен с информационным . входом второго коммутатора, выход второго коммутатора соединен с информационным входом блока коммутаторов, первый выход схемы сравнения соединен с управляющим входом второго коммутатора, второй выход схемы сравнения соединен с входом считывания третьего блока памяти и вторым входом элемента ИЛИ, выход элемента ИЛИ соединен с входом считывания четвертого блока памяти, выход которого соединен с информационным входом второго сдвигового. регистра, первый и второй выходы второго сдвигового регистра соединены с первым информационным входом схемы сравнения и входом первого сомножителя первого умножителя соответственно, выход счетчика соединен с вторим информационным входом схемы сравнения, второй выход блока коммутаторон соединен с входом первого элемента задержки, выход которого соединен с входом вычитаемого первого блока вы< читания и через второй элемент задержки с входом первого слагаемого первого сумматора, выход первого бло-, ка вычитания соединен с выходом второго сомножителя первого умножителя, выход которого соединен с входом второго слагаемого первого сумматора, выход первого сумматора соединен с входом уменьшаемого и через третий элемент задержки с входом вычитания второго блока вычитания, а через последовательно включенные третий и четвертый элементы задержки с входом первого слагаемого второго сумматора, выход второго блока вычитания соединен с входом первого сомножителя второго умножителя, выход которого соединен с входом второго слагаСоставитель В,Бородин

Редактор Н.Горват Техред Л.Сердюкова Корректор А.Зимокосов

Тираж 673 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раупская наб., д. 4/5

Заказ 784/54

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

9 12970 емого второго сумматора, выход второго сумматора соединен с информационным входом первого коммутатора, выходы первого коммутатора соединены с информационными входами блока сдвиговых регистров, выходы которого соединены с информационными входами первого сдвигового регистра, выход которого соединен с информационным входом второго блока памяти, выход 1п третьего блока памяти соединен с информационным. входом регистра, выход которого соединен с входом второго сомножителя второго умножителя.

2. Устройство по п. 1, о т л и" ч а ю щ е е с я тем, что блок коммутаторов содержит три коммутатора, элемент И и элемент задержки, причем информационный вход блока соединен с информационными входами с первого по третий коммутаторов, управляющий вход блока соединен с управляющим входом первого коммутатора, с, первым входом элемента И и через элемент задержки с вторым входом элемента И и с управляющим входом третьего коммутатора, выход элемента И соединен с управляющим входом второго коммутатора, выход третьего коммутатора является первым выходом блока, выходы первого и второго коммутаторов соединены с вторым выходом блока„